How to optimize LPUART power consumption on STM32 MCUs

### Introduction

STM32 microcontrollers listed in *Table 1* feature an alternative universal asynchronous receiver transmitter (UART) interface, enabling them to operate with minimum power requirements.

This document explains how to fully exploit the advantages of the low-power UART (LPUART), thus extending product battery life. It shows in practical examples the extremely low-power consumption of the device waiting for a communication.

The code used to perform the measurements described in *Section 7.1* and *Section 7.2* is supplied in the package X-CUBE-LPUART, and can be downloaded from *www.st.com*.

| Туре                    | Series, line or part number                    |

|-------------------------|------------------------------------------------|

|                         | STM32G0 and STM32G4 series                     |

| Microcontrollers        | STM32L0, STM32L4, STM32L4+, and STM32L5 series |

|                         | STM32H7 series                                 |

|                         | STM32U0, STM32U3, and STM32U5 series           |

|                         | STM32WB series                                 |

| STM32 Embedded Software | X-CUBE-LPUART                                  |

# Contents

| 1 | Defi | nitions  |                                  |

|---|------|----------|----------------------------------|

| 2 | Refe | erence d | ocuments                         |

| 3 | Sum  | mary of  | <sup>-</sup> features            |

|   | 3.1  | Clock s  | subsystem                        |

|   |      | 3.1.1    | MSI clock                        |

|   |      | 3.1.2    | HSI clock                        |

|   |      | 3.1.3    | Low speed clock sources          |

|   |      | 3.1.4    | CSI clock                        |

|   | 3.2  | Power    | management 10                    |

|   | 3.3  | Compa    | arison with USART peripheral 10  |

| 4 | Ope  | ration m | nodes                            |

|   | 4.1  | Polling  | mode                             |

|   | 4.2  | IT mod   | le 12                            |

|   | 4.3  | DMA m    | node                             |

|   | 4.4  | Combi    | ned mode examples                |

|   |      | 4.4.1    | Interrupt with polling           |

|   |      | 4.4.2    | Combining DMA with direct access |

| 5 | Othe | er consi | derations                        |

|   | 5.1  | Execut   | ion from SRAM                    |

|   | 5.2  | GPIO (   | configuration                    |

|   | 5.3  | Clock of | configuration                    |

|   |      |          | Clock prescalers                 |

|   | 5.4  |          | configuration                    |

|   |      | 5.4.1    | Use of Stop and Sleep modes      |

|   |      | 5.4.2    | Run time configuration           |

|   |      | 5.4.3    | STM32H7 core domain sections     |

|   |      | 5.4.4    | SMPS                             |

|   | 5.5  | Cache    | memory                           |

|   |      |          |                                  |

AN4635 Rev 9

| 6 | Relia | Reliability and communication quality |                                               |      |

|---|-------|---------------------------------------|-----------------------------------------------|------|

|   | 6.1   | Noise a                               | and frequency shift                           | . 18 |

|   | 6.2   | Droppe                                | ed bytes                                      | . 18 |

| 7 | Powe  | er consi                              | umption comparison                            | . 19 |

|   | 7.1   | Measu                                 | rements on the STM32L053 Nucleo board         | 20   |

|   |       | 7.1.1                                 | Stop vs. Sleep mode                           | . 20 |

|   |       | 7.1.2                                 | Short periods of Sleep mode and Low-power run | . 21 |

|   |       | 7.1.3                                 | Interrupt operation overhead                  | . 22 |

|   |       | 7.1.4                                 | Going to Stop between received bytes          | . 23 |

|   |       | 7.1.5                                 | Different oscillator clock speeds             | . 25 |

|   |       | 7.1.6                                 | Changing AHB divider ratio                    | . 26 |

|   |       | 7.1.7                                 | Different peripheral clock settings           | . 28 |

|   |       | 7.1.8                                 | ULP bit setting                               | . 29 |

|   |       | 7.1.9                                 | Higher communication speed                    | . 30 |

|   |       | 7.1.10                                | Wake-up from Stop mode on HSI                 | . 31 |

|   |       | 7.1.11                                | Voltage regulator settings                    | . 33 |

|   |       | 7.1.12                                | GPIO pull-up                                  | . 34 |

|   | 7.2   | Measu                                 | rements on STM32L476 Nucleo board             | 36   |

|   |       | 7.2.1                                 | Three approaches at a glance                  | . 36 |

|   |       | 7.2.2                                 | Simple polling mode on low core frequency     | . 37 |

|   |       | 7.2.3                                 | The role of voltage regulator settings        | . 38 |

|   |       | 7.2.4                                 | Idle modes compared                           | . 39 |

|   |       | 7.2.5                                 | Use of MSI PLL-mode for higher speeds         | . 41 |

|   |       | 7.2.6                                 | Using two oscillators                         | . 42 |

|   | 7.3   | Measu                                 | rement on the STM32H743 Nucleo144 board       | 43   |

|   | 7.4   | STM32                                 | WB55 Nucleo board testing                     | 43   |

|   | 7.5   | STM32                                 | G474 Nucleo board testing                     | . 44 |

|   | 7.6   | STM32                                 | 2U575 Nucleo 144 board testing                | 45   |

|   | 7.7   | STM32                                 | 2U073RC Nucleo 64 board testing               | 47   |

| 8 | Exan  | nple pro                              | oject                                         | 48   |

|   | 8.1   | HW set                                | tup                                           | . 48 |

|   | 8.2   | Configu                               | uring the example                             | 48   |

|   | 8.3   | Examp                                 | le operation                                  | 49   |

| 9  | Conclusion       | 50 |

|----|------------------|----|

| 10 | Revision history | 51 |

# List of tables

| Table 1.  | Applicable products and software            | 1  |

|-----------|---------------------------------------------|----|

| Table 2.  | List of acronyms                            | 7  |

| Table 3.  | Comparison of features                      | 10 |

| Table 4.  | Clock options                               |    |

| Table 5.  | Configurations - Stop vs. Sleep mode        | 20 |

| Table 6.  | Configurations - Sleep mode vs. LPRUN       | 22 |

| Table 7.  | Configurations - Interrupt operation        |    |

| Table 8.  | Configurations - Stop during data reception | 24 |

| Table 9.  | Configurations - Core clock speed           | 25 |

| Table 10. | Configurations - AHB divider                | 27 |

| Table 11. | Configurations - Clock divider              | 28 |

| Table 12. | Configurations - ULP bit effect             |    |

| Table 13. | Configurations - Higher communication speed | 31 |

| Table 14. | Configurations - HSI vs. MSI                |    |

| Table 15. | Configurations - Voltage regulator settings | 33 |

| Table 16. | Configurations - GPIO pull-up               | 34 |

| Table 17. | Configurations - Managing communication     | 36 |

| Table 18. | Configurations - Polling                    |    |

| Table 19. | Configurations - Voltage regulator settings | 39 |

| Table 20. | Configurations - Idle modes                 | 40 |

| Table 21. | Configurations - HSI and PLL                |    |

| Table 22. | Configurations - Stop with 56700 Bd speed   |    |

| Table 23. | Configurations - Managing communication     |    |

| Table 24. | Influence of the AHB prescaler              |    |

| Table 25. | Comparison of different operation modes     | 46 |

| Table 26. | Comparison of different operation modes     | 47 |

| Table 27. | Document revision history                   | 51 |

|           |                                             |    |

# List of figures

| Figure 1.  | Test loop description.                                           | 19 |

|------------|------------------------------------------------------------------|----|

| Figure 2.  | Stop vs. Sleep mode                                              | 20 |

| Figure 3.  | Sleep mode vs. LPRUN                                             | 21 |

| Figure 4.  | Interrupt operation overhead                                     | 23 |

| Figure 5.  | Using the Stop during data reception                             | 24 |

| Figure 6.  | Core clock speed comparison                                      |    |

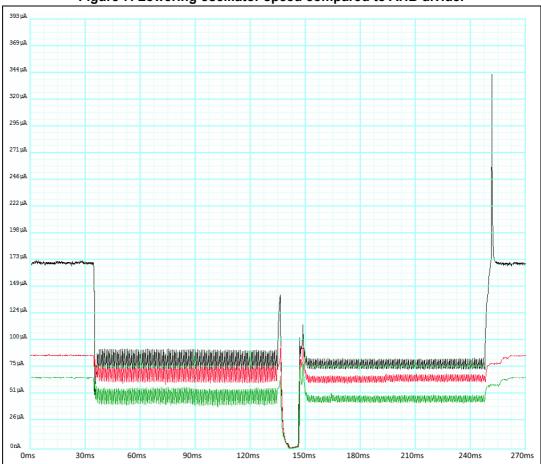

| Figure 7.  | Lowering oscillator speed compared to AHB divider                | 27 |

| Figure 8.  | Three different settings of peripheral clock divider             | 28 |

| Figure 9.  | ULP bit effect                                                   | 29 |

| Figure 10. | Operating at 57600 Bd                                            | 30 |

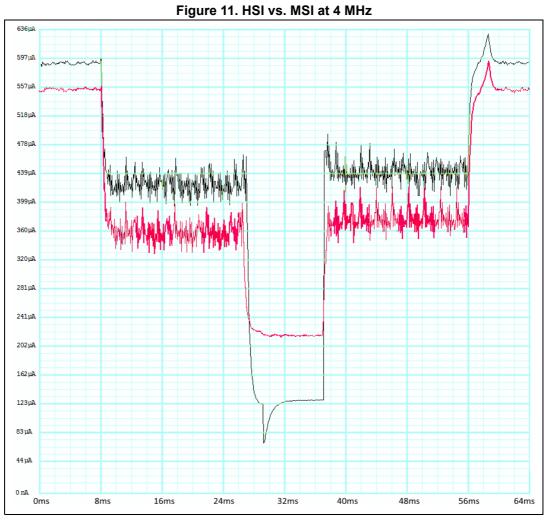

| Figure 11. | HSI vs. MSI at 4 MHz                                             | 32 |

| Figure 12. | Comparison between voltage regulator settings                    | 33 |

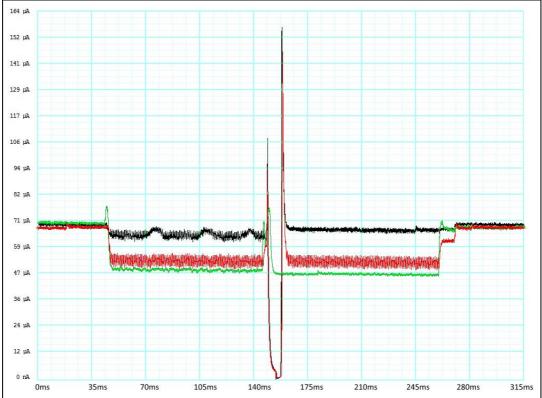

| Figure 13. | GPIO internal pull-up                                            | 34 |

| Figure 14. | Comparison of three different approaches to manage communication | 36 |

| Figure 15. | Polling communication at minimum settings                        | 37 |

| Figure 16. | Voltage regulator settings                                       | 39 |

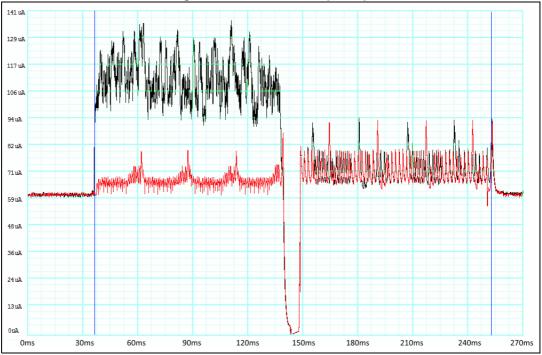

| Figure 17. | Comparison of Idle modes                                         | 40 |

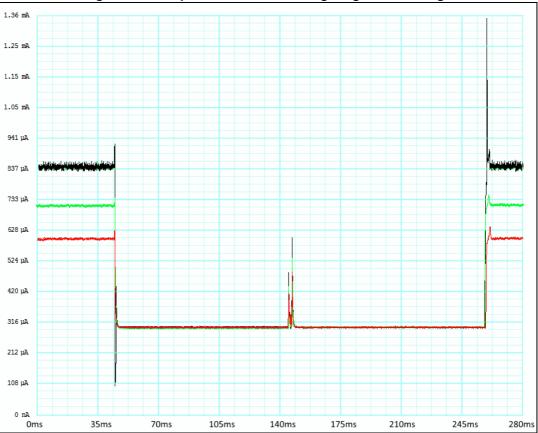

| Figure 18. | HSI and PLL current consumption                                  | 41 |

| Figure 19. | Using Stop with 57600 Bd speed                                   | 42 |

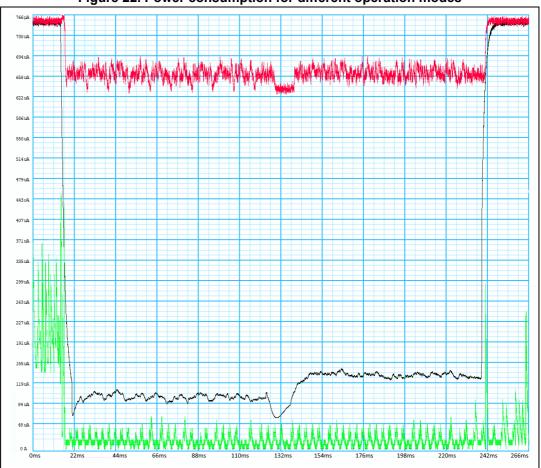

| Figure 20. | Comparison of three different approaches to manage communication | 44 |

| Figure 21. | Interrupt operation with three different core clocks             | 45 |

| Figure 22. | Power consumption for different operation modes                  | 46 |

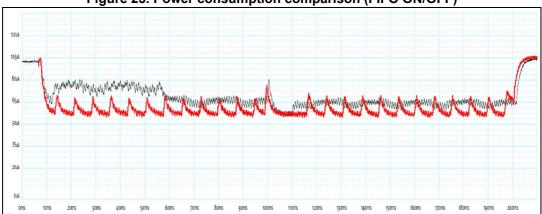

| Figure 23. | Power consumption comparison (FIFO ON/OFF)                       | 47 |

|            |                                                                  |    |

# 1 Definitions

| Table | 2.       | List | of         | acronyms |

|-------|----------|------|------------|----------|

| TUDIC | <b>-</b> | LIUL | <b>U</b> 1 | acronyms |

| Term       | Description                                                 |

|------------|-------------------------------------------------------------|

| LSE        | Low-speed external clock                                    |

| LSI        | Low-speed internal clock                                    |

| HSE        | High-speed external clock                                   |

| HSI, HSI16 | High-speed internal clocks                                  |

| MSI        | Multispeed internal clock source                            |

| UART       | Universal asynchronous receiver transmitter                 |

| LPUART     | Low-power UART                                              |

| MCU        | Microcontroller                                             |

| USART      | Universal synchronous and asynchronous receiver transmitter |

| BLE        | Bluetooth <sup>®</sup> Low Energy                           |

| CPU        | Central processing unit (part of the MCU)                   |

| NVIC       | Nested vector interrupt controller                          |

| DMA        | Direct memory access                                        |

| тс         | Transmission complete                                       |

| RF         | Radio frequency                                             |

| RM         | Reference manual                                            |

| SWD        | Serial wire debug interface                                 |

| BAM        | Batch acquisition mode                                      |

| LPBAM      | Low-power background autonomous mode                        |

## 2 Reference documents

The following documents (available on *www.st.com*) must be considered as reference:

- STM32L0xx ultra-low-power features overview (AN4445)

- STM32L4xx ultra-low-power features overview (AN4621)

- STM32L5 Series microcontroller ultra-low power features overview (AN5213)

- Using STM32 cache to optimize performance and power efficiency (AN5212)

- Optimizing power and performance with STM32L4 and STM32L4+ Series microcontrollers (AN4746)

- STM32L47xxx, STM32L48xxx, STM32L49xxx and STM32L4Axxx advanced Arm<sup>®</sup>based 32-bit MCUs (RM0351)

- Ultra-low-power STM32L0x2 advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0376)

- STM32H7x3 advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0433)

- STM32H7A3/B3 advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0455)

- STM32H723/733, STM32H725/735 and STM32H730 Value line advanced Arm<sup>®</sup>based 32-bit MCUs (RM0468)

- STM32H7R/7Sxx Arm<sup>®</sup>-based 32-bit MCUs (RM0477)

- Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> Low Energy and 802.15.4 radio solution (RM0434)

- Multiprotocol wireless 32-bit MCU Arm<sup>®</sup>-based Cortex<sup>®</sup>-M4 with FPU, Bluetooth<sup>®</sup> Low Energy or 802.15.4 radio solution (RM0471)

- STM32L552xx and STM32L562xx advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0438)

- STM32G4xx advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0440) and STM32G0x1 advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0444)

- STM32L4+ Series advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0432)

- STM32U5 Series Arm<sup>®</sup>-based 32-bit MCUs (RM0476)

- STM32U0 series advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0504)

- STM32U3 series advanced Arm<sup>®</sup>-based 32-bit MCUs (RM0487)

### 3 Summary of features

While the LPUART peripheral is practically the same, there are significant differences in its integration on the MCUs addressed by this document. They feature different Arm<sup>®</sup> Cortex<sup>®</sup> cores<sup>(a)</sup>, and there are other architectural differences impacting the LPUART efficiency.

### 3.1 Clock subsystem

#### 3.1.1 MSI clock

This is an internal oscillator capable of fast, simple, and seamless change in operating frequency of low-power oriented devices. The maximum frequency is different for various MCUs, and so are the MSI ranges. This gearing up of the MSI reduces the choice of low speeds, the slowest possible frequency on STM32U0, STM32WB, STM32L4 and STM32L4+ products is 100 kHz, vs. 65 kHz on STM32L0xx MCUs.

On STM32U3 and STM32U5 series, the MSI is split (MSIS and MSIK). MSIK can be used for LPUART autonomous operation up to Stop2 mode (including wake-up capability), with clock speed different from system MSIS clock.

For speeds closer to 1 MHz, a direct comparison of efficiency is difficult. In the STM32L4, STM32L4+, STM32L5, STM32U0, STM32U3, STM32U5, and STM32WB series the MSI can use the HW auto calibration with LSE in its PLL-mode (option not available on STM32L0 products). This makes the MSI much more precise.

The MSI clock is not implemented on STM32G0, STM32G4, STM32H5, and STM32H7 series, not primarily intended as low-power devices.

#### 3.1.2 HSI clock

The STM32L0 series features a simple clock factor-4 divider, associated with the HSI clock source, making the HSI the effective source of either the 16 or the 4 MHz. MCUs of other low-power series do not have a divider directly on the HSI16 clock. As a result, the STM32L0 is much more efficient in certain applications requiring UART speeds higher than 9600 Bd. If (for STM32WB, STM32L4, STM32L4+, STM32L5, STM32U3, and STM32U5 series) 16 MHz is not efficient, the solution is to use a second source for system clock.

STM32G0 and STM32G4 series MCUs feature an even more flexible divider, allowing to set the two dividers in the 1-512 range, using the HPRE bits in the RCC\_CFGR register.

STM32H5 and STM32H7 series MCUs have a similar flexible setup, with HSIDIV divider values of 1, 2, 4, and 8, but with a 64 MHz nominal frequency oscillator.

#### 3.1.3 Low speed clock sources

LSI clock frequency also differs, but this is not relevant to our case.

arm

a. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

#### 3.1.4 CSI clock

This is a low-power oscillator integrated on STM32H5 and STM32H7 devices. Its nominal frequency (4 MHz) is sufficient for most of the low-power tasks.

### 3.2 Power management

The main LDO regulator on STM32L4, STM32L4+, STM32G0, STM32G4, STM32U0, STM32U3, and STM32WB<sup>(a)</sup> series has only two ranges, instead of the three available on the STM32L0xx MCUs. Moreover, these two ranges are shifted towards higher frequencies, supported by the more powerful MCU.

This deficiency is compensated by the Low-power run mode.

STM32L0xx MCUs cannot return to the Low-power run mode directly upon waking from Sleep or Stop Low-power mode, this limitation is not present in the series featuring a Low-power mode. Low-power run on STM32L4, STM32L4+, STM32G0, STM32G4, STM32U0, and STM32WB series is not limited by the MSI range 1, but works up to 2 MHz system clock speed. HSI16 can still be used as peripheral clock, even in Low-power run.

STM32H5, STM32H7<sup>(b)</sup>, and STM32U5 MCUs feature four LDO or SMPS power regulator ranges, resulting in an extended performance range.

STM32L5 relies on SMPS regulation, which is only optional in other products.

### 3.3 Comparison with USART peripheral

The LPUART has less features compared to the USART, however it operates using less power, and uses the LSE clock more efficiently.

The main features for the two peripherals are summarized in Table 3.

| Configuration              | LPUART | USART |  |  |

|----------------------------|--------|-------|--|--|

| LSE clocked 9600 Bd option | +      | -     |  |  |

| Synchronous mode           | -      | +     |  |  |

| Ir SIR compatibility       | -      | +     |  |  |

| Smartcard mode             | -      | +     |  |  |

| Auto baud rate detection   | -      | +     |  |  |

| Modbus communication       | -      | +     |  |  |

| LIN mode                   | -      | +     |  |  |

#### Table 3. Comparison of features

The USART is also able to operate using the LSE clock, the communication speed is limited to 4000 Bd in case of oversampling by 8, to 2000 Bd when oversampling is by 16.

a. Only one range is available on STM32WB15xx devices.

b. STM32H7R/7Sx devices are limited to two ranges.

When using the LPUART, only the 32.768 kHz LSE clock is required for serial communication up to 9600 Bd, with minimal energy consumption and very precise speed setting made possible by the external crystal.

For higher speeds the LPUART energy efficiency advantage drops, but still remains close to 5% (see *Section 7.1.9*).

This document focuses on communication at 9600 Bd, common to many applications: the efficiency advantage of LPUART is obvious when using wake-up from Stop at the 9600 Bd speed setting.

The LPUART can initiate wake-up from deeper Stop modes, such as Stop2 or Stop1.

## 4 Operation modes

Real-world scenarios cover a wide variety of configurations, using different baud rates, ratios of transmit/receive and delays between messages. All these factors influence the choice of the operation mode.

### 4.1 Polling mode

Polling mode (also known as blocking mode) is the simplest possible operating mode. The CPU is processing a single task, switching to a low-power mode during periods of inactivity. There is almost no processing overhead, making it possible to use very low system clock speeds.

This mode is extremely efficient for very simple scenarios, however it effectively blocks the CPU from executing other tasks, like data processing or concurrent communication.

### 4.2 IT mode

The second option is to rely completely on interrupts, waking the CPU for every transferred byte. This operation mode uses the Arm<sup>®</sup> Cortex<sup>®</sup> advanced NVIC to keep the processing split to atomic operations, never blocking the CPU, and achieving real-time responses.

This mode strains the CPU a little more, adding processing overhead related to stack and context resuming.

### 4.3 DMA mode

In DMA mode the CPU is spared a large portion of processing, setting a DMA channel to move data between the peripheral and the SRAM. The CPU can spend part of the processing time in Sleep mode. The user can disable half-buffer interrupt when not needed for circular buffer management, to let the CPU core rest even longer. In most of the cases the DMA cannot be used in combination with the Stop mode, hence all DMA channels have to be disabled before entering the Stop Low-power mode. Some of the STM32H7 MCUs are an exception to this rule because the power domains are split, and the DMA with LPUART can operate within separate domains. Details are provided in *Section 7.3*. The STM32U5 introduces an LPBAM, which can operate while the CPU is in Stop mode.

On devices that do not feature LPBAM, the LPUART transfer can be done thanks to the batch acquisition mode (BAM), in which the MCU is in Sleep or in Low-power sleep mode (CPU is clocked off). The consumption is optimized by configuring the flash memory in Power-down mode, switching off its clock, and by clocking only the DMA, the LPUART, and the SRAM.

The DMA has one definitive advantage over the previous two methods: the transfer to memory is handled independently from the CPU load and the interrupt is only triggered once the data is stored in RAM for the firmware to process the following action. With interrupt and polling mode the firmware must read the data from the peripheral register, and with wrong timing some data can be lost in overrun error.

### 4.4 Combined mode examples

Real-world applications usually are a mix of the described modes, and the developers always try to strike the best bargain between conflicting needs. The following examples are not covered in bundled source codes.

#### 4.4.1 Interrupt with polling

Some embedded systems are not real-time critical, in this case there is an option to block the CPU for a limited time to process a message frame. Especially in case of transmission, energy normally used to process all TC interrupts is saved. The message is transmitted in blocking mode, possibly with clock speed lowered and power regulator switched to Low-power mode (LPRUN). Only approximately half clock speed is required if the CPU can treat the message in blocking mode. Normal operation is then restored, preferably waiting for incoming reply interrupt in Stop mode.

#### 4.4.2 Combining DMA with direct access

The DMA channel is convenient for transmission of data, and is power-efficient during reception.

The downside is that in DMA mode the LPUART cannot take advantage of wake-up from Stop mode. The reason is that after wake-up event the DMA has difficulty picking up on the ongoing communication. This is a serious disadvantage for all applications staying idle for long periods of time.

The DMA can still be used for transmission and then reception can proceed with blocking or interrupt approach. In communication systems where incoming messages are coming in quick succession or predictable timing, the DMA based reception is an efficient option.

### 5 Other considerations

For a complete overview of low-power advantages refer to the already mentioned AN4445, AN4621 and AN4746. The following recommendations are specific for our case and example.

### 5.1 Execution from SRAM

If the program can be executed from SRAM, there is an option to turn off the embedded flash memory (by clock gating), further reducing the power consumption. The SRAM is also capable of execution at full CPU speed, without flash memory latency.

### 5.2 GPIO configuration

Some GPIO settings have great influence on power consumption, while others do not.

The pins used for the UART communication lines should be configured to their alternate function mode. It is not recommended to activate pull-ups if lowest possible power consumption is the most important goal, however, in some applications it may be necessary to improve the communication reliability. The speed setting has no consequences regarding the power consumption on the tested baud rates.

Half-duplex mode, when applicable, can lead to further power savings, but this configuration is not addressed in this document.

Other pins, not used by the application, must be configured as analog inputs. The developer must put the debug lines also to analog, once the application is ready for deployment.

On some products, such as the STM32L4 series, the LPUART can be assigned to GPIOG port with alternate (lower) voltage, leading to additional energy savings.

### 5.3 Clock configuration

For LPUART peripheral clock, LSE source is the choice to reach 9600 Bd with wake-up from Stop mode.

HSI/CSI is recommended for higher speeds.

The obvious (and default) choice for system clock is usually the MSI oscillator. On STM32L4, STM32L4+, STM32U0, STM32U3, STM32U5, and STM32WB series the MSI offers even more flexibility and its fluctuations can be corrected using HW auto calibration with the LSE in its PLL-mode.

Prescalers and PLL can be used to derive other speeds, different options are analyzed later in this document. These solutions are not the best ones when power consumption is the first concern. User must refer to the product datasheet for typical power consumptions for different clock configurations.

It makes sense to use a single high speed clock for system and peripherals, as each high speed oscillator contributes to power consumption. On the other hand, it is advantageous to run the low speed clock in parallel to the system clock, and use it for the peripherals able to work at that frequency.

AN4635 Rev 9

| Source    | Advantages                                                                                                                                                | Limitations                                                                                                                                                                  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HSI/HSI16 | <ul> <li>Ready to use high speed clock with<br/>precise trimming</li> </ul>                                                                               | <ul> <li>Worst MHz / W ratio option</li> <li>Fixed speed on most of STM32 MCUs</li> </ul>                                                                                    |  |  |

| MSI       | <ul> <li>Easy and fast clock throttling</li> <li>Lowest overall power consumption (on STM32L0 series when clocked below 1 MHz)</li> </ul>                 | <ul> <li>Only available on low-power MCUs</li> <li>Clock is relatively unstable and imprecise<br/>(unless the auto-calibration using LSE in<br/>PLL-mode is used)</li> </ul> |  |  |

| HSE       | <ul> <li>Potentially most power efficient at<br/>1 MHz and above on STM32L0 series</li> <li>Efficiency comparable to MSI on<br/>STM32L4 series</li> </ul> | <ul> <li>Needs additional external components<sup>(1)</sup></li> <li>Limited options of speed control<br/>(prescalers only)</li> </ul>                                       |  |  |

| Table 4. Clock opti | ions |

|---------------------|------|

|---------------------|------|

1. HSE is used by the RF block in STM32WB series MCUs, so the components are needed anyway.

#### 5.3.1 Clock prescalers

The RCC module offers the possibility to tune down peripheral bus clocks, the AHB and APB frequency (RCC\_CFGR register).

Slowing the AHB down brings significant power savings if there is no other clock source with a suitable frequency. The memory interface is also clocked with AHB. While power consumption with prescaler of 8 drops by approximately 50%, the processing capability of the system drops even more, due to delays in fetching instructions from the program memory and in storing the data in the memory. If possible, it is better to slow down the system clock rather than set an AHB prescaler (*Section 7.1.6*).

Slowing down the APB limits the bandwidth between the LPUART peripheral and the core. This is usually not a problem, as the amount of data transferred is low, especially in case of DMA transfers. In case of CPU driven transfers the core can be stalled waiting for the bus transfer to complete. This causes the overall energy budget for the operation to increase in extreme cases. Also, if the bus transfer is not complete, the core is prevented from going to a low-power mode. In the examples described in this document it is usually safe to set an APB prescaler value of 4, as higher values are likely to cause problems, and do not reduce power consumption (*Section 7.1.7*).

### 5.4 **Power configuration**

This section deals with practical implications when configuring power modes for LPUART communication. For complete information read the dedicated sections in the reference manuals.

#### 5.4.1 Use of Stop and Sleep modes

It is a paradigm in embedded software that, during the idle time, the CPU must not run and actively check flags, but rather switch to Low-power mode, suspend clock, and only resume operation on external interrupts or events.

In MCUs based on Arm<sup>®</sup> cores, this is achieved by executing WFE or WFI instruction. All STM32 microcontrollers offer highly configurable selection of Idle modes, described in detail

AN4635 Rev 9

in the reference manuals. The great advantage of LPUART is the ability to take advantage of Stop mode when waiting for message reception (*Section 7.1.1*).

If the application running on STM32L0xx products does not use VREFINT frequently and spends most of the time in low-power modes, configure Ultra-low-power mode with fast wake-up (ULP and FWU bit in PWR configuration register). Even in applications using internal voltage reference, it is advised to switch it off, and check only the startup time when a measurement is needed (VREFINT startup requires some additional energy). For short periods of Low-power mode (i.e. Sleep mode between bytes) there is no advantage in turning it off and on again, the overall energy budget increases.

*Note:* Ultra-low-power mode without fast wake-up is unable to keep the LPUART Tx register fed, or to keep up with incoming data in blocking and interrupt mode, even with 9600 Bd communication speed.

There is no option to completely switch off the VREFINT on the other series addressed by this document.

In most cases, it is desirable to activate the Sleep mode between processing individual bytes. In case or data reception even Stop mode is available (*Section 7.1.4*). This practice offers great advantage at higher clock speeds, but at core clock speeds near the bare minimum needed for communication it is not recommended. The overhead related to putting device to Sleep mode and waking it causes a slight increase of power consumption, not balanced by the very short time spent in Low-power mode (*Section 7.1.2*).

#### 5.4.2 Run time configuration

The voltage regulator settings are very important. Use the core voltage scaling as much as possible (see dedicated sections in datasheets and reference manuals). As an example, on STM32L0xx switching from Range 1 to Range 3 is an easy way to lower typical consumed power by more than 25% (*Section 7.1.11*).

Other low-power series (except STM32L0 and STM32U5) provide only two ranges of the main regulator, however all these series (except STM32U5) feature a Low-power run mode.

As an example, on STM32L0xx MCUs in polling mode, which requires the least CPU processing resources, it is possible to take advantage of the Low-power run mode. This mode essentially bypasses the main voltage regulator, and powers the core with a consumption approximately 25% lower than that achievable with Range 3 of the main power regulator (*Section 7.1.2*).

On STM32L0xx MCUs waking from Stop or Sleep mode brings the main regulator back on, and because of the current low clock speed (MSI Range 1 at most), the core must immediately dedicate all processing power to data reception. In practical terms the LPRUN is great for transmission phase, but when waiting for data reception it is usually better to take advantage of the Stop mode instead of keeping the CPU in LPRUN. It is however possible to put the main voltage regulator temporarily to Range 3 (it must be in Range 2 when switch to LPRUN is done). Changing configuration of main regulator is quicker than switching the regulator, and less likely to cause dropped bytes in incoming message (wake-up from Stop and power configuration changes must be handled in time shorter than 1 byte duration).

On STM32L4, STM32L4+, STM32L5, and STM32U0 series the LPRUN mode provides additional functionality. It works up to 2 MHz, providing enough processing power for 57600 Bd communication speed in interrupt mode. It is even possible to wake from Stop or Sleep directly to Low-power run, without waking up the main regulator.

The STM32WB regulator power scaling is identical to that of STM32L4 and STM32L5, but, because of the second core, there are more options, exceeding the scope of this document.

The STM32G4 and STM32G0 have two base power scaling ranges, with Range 2 available up to 26 and 16 MHz, respectively.

STM32U5, STM32H5 and STM32H7 MCUs feature four ranges of the internal LDO, there are two on STM32U3 devices. All come with some cache and prefetch. It is advised, for power efficiency, to accept higher latency, and choose the lowest LDO voltage setting for the chosen system clock.

#### 5.4.3 STM32H7 core domain sections

Larger devices, based on the Cortex-M7 core, use independent power domains to maintain DMA operation while the CPU is in low power mode. In STM32H74x/H75x/H72x/H73x the LPUART is linked to D3 domain, while on STM32H7Ax/H7Bx it is called SRD, serving the same purpose.

The power domain has its dedicated memory section, to avoid powering the whole memory during the low-power state.

See the specific product reference manual for details and implementation examples.

#### 5.4.4 SMPS

Some STM32L4+, STM32L5, STM32U3, STM32U5, and STM32WB products feature an integrated SMPS, a power supply option that increases efficiency, especially if the available  $V_{DD}$  branch of the PCB is relatively high voltage (like 3.3 V).

A detailed explanation of the usage of the embedded SMPS is out of the scope of this document.

#### 5.5 Cache memory

Several STM32 microcontrollers feature a cache memory. Having the instructions or data available in the cache instead of waiting for fetch from system memory improves execution efficiency and power consumption. Refer to "*STM32 power mode examples*" (AN4777), available on *www.st.com*, to learn more about different cache configurations.

## 6 Reliability and communication quality

### 6.1 Noise and frequency shift

Line noise usually causes no issues at the low communication speed typical of low-power applications. In some cases, random noise can be mitigated by adding a weak pull-up, at the expense of additional energy. For example, the internal pull-up (no extra parts) increases power consumption by approximately 30  $\mu$ A during transmission in the example described in *Section 8*.

Framing errors occur as result of incorrect base frequency (speed setting) at one of the communication participants. The LSE clock source, which is best suited for low-power applications, is very accurate. The framing errors are likely only if the LPUART peripheral clock is derived from MSI clock. The LPUART cannot auto detect the uncalibrated communication speed of its counterpart, relying only on the precise speed settings with framing reliability.

### 6.2 Dropped bytes

To achieve lower power consumption tune down core frequency and use low-power modes.

This imposes a challenge of waking up and responding to peripheral events. In transmission case this may cause delay between bytes sent, leading to prolonged period of activity, impacting system efficiency, but without data loss.

The problem is data reception. In polling or interrupt driven mode, if the received data in the LPUART data register is not read in time (before a new data is received), an overrun error occurs, and data received during overrun are lost.

To avoid missing data in reception, the following guidelines can be provided:

- ensure a correct clock speed (not below a certain minimum) for the core

- boost the LPUART interrupts priorities to the highest possible level in the application, to make them basically un-interruptible

- use the DMA for data transfers

### 7 Power consumption comparison

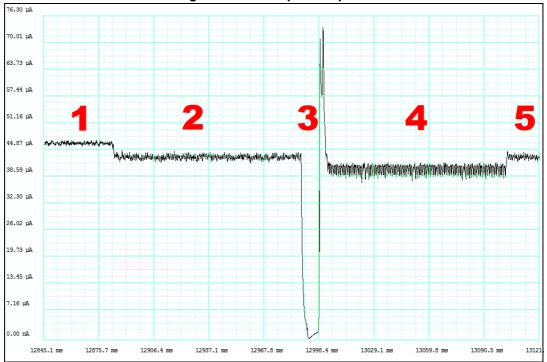

All the pictures in this section show the detailed measurement of differently configured Low-power Nucleo running the following routine, graphically illustrated in *Figure 1*:

- 1. Run mode in waiting loop, showing the regular power consumption

- 2. Transmission of a 100-byte message

- 3. Idle state 10 ms: Stop or Sleep mode waiting for reply (depending on configuration)

- 4. Reception of the same 100 bytes

- 5. Compare the message to detect communication errors and go back to 1

Figure 1. Test loop description

The device starts running full speed in the loop to showcase the regular power consumption on its clock configuration. This is followed by approximately 100 ms of 9600 Bd transmission, then 10 ms of idle state, waiting for the incoming reply. Only few measurements feature the higher communication speed of 57600, where the communication phases 2 and 4 are significantly shorter. Receiving the reply takes another 100 ms.

Both the transmission and reception usually consume less power than the regular run mode, as the device is configured to save power in short periods between single bytes of the message.

The measurements detailed in the following pages are an example of how the X-CUBE-LPUART Expansion Package can be used: it does not cover all the MCU with LPUART and it does not compare all their configurations, but points out interesting features and shows some available solutions.

#### 7.1 Measurements on the STM32L053 Nucleo board

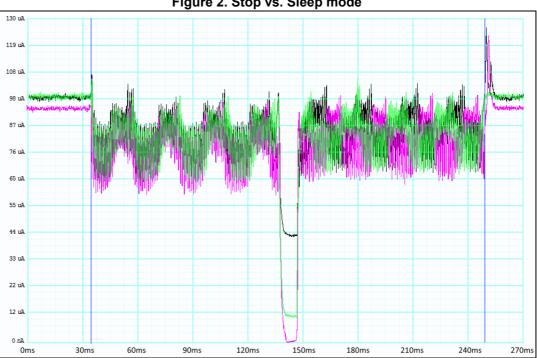

#### 7.1.1 Stop vs. Sleep mode

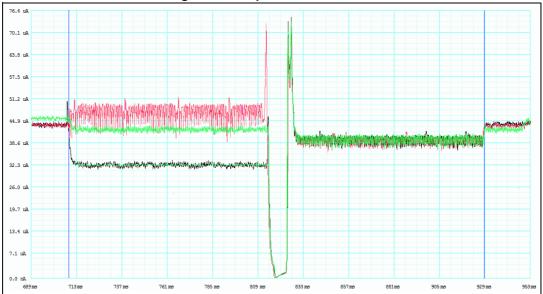

The first comparison deals with the difference between Sleep and Stop modes.

While waiting for the incoming communication, the device tries to minimize the power consumption. The black line in Figure 2 represents debug configuration with device waiting in Sleep mode. Using the LSE clock and LPUART peripheral the Stop mode can be employed up to speed of 9600 Bd (the green line). The purple line shows the absolute minimum current absorbed in Stop mode where the debug lines are configured as analog input and the device uses the ULP + FWU combination.

| Curve in <i>Figure</i> 2                | Black             | Green Purple |         |

|-----------------------------------------|-------------------|--------------|---------|

| Idle mode between transmissions         | Sleep             | Stop         |         |

| Debug interface                         | ON                |              | OFF     |

| Current average over phases 2, 3, and 4 | 83.3 μΑ 80.3 μΑ 7 |              | 77.3 µA |

| Clock                                   | 500 kHz MSI       |              |         |

| Table 5. Configurations - Stop VS. Sleep mode (continued) |                                                               |         |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------|---------|--|--|

| Curve in <i>Figure</i> 2                                  | Black Green Purple                                            |         |  |  |

| Voltage regulator                                         |                                                               | Range 3 |  |  |

| ULP/FWU                                                   | +/+                                                           |         |  |  |

| AHB/APB ratio                                             | 1/1                                                           |         |  |  |

| Baud rate                                                 | 9600 Bd                                                       |         |  |  |

| SW used                                                   | Interrupt operation (Com IT) with defines RXSLEEP and TXSLEEP |         |  |  |

Table 5. Configurations - Stop vs. Sleep mode (continued)

#### 7.1.2 Short periods of Sleep mode and Low-power run

In some cases the WFE can be used to put the core to suspended mode while waiting for a flag or event, but this can increase the power consumption. When the core clock speed is just enough to perform the requested operation, adding WFE instruction can increase the power consumption. Consider using the Low-power run regulator mode instead. The Low-power run effect is terminated with each wake-up from either Stop or Sleep mode, but until that wake-up it saves a lot of energy.

In *Figure 3* the red line represents the configuration where the execution in Low-power run mode is terminated by the code that goes to Sleep mode after each byte transmission. The green line is a code that runs with voltage regulator set to Range 3, making no attempts to use Sleep mode during transmission. The black line is the power consumption of a code that stays in LPRUN until it goes to Stop mode after finishing the transmission. All three codes use the regulator Range 3 along with Sleep mode after each byte during reception phase. In case of such a short time in Stop mode it is more efficient to leave the code in LPRUN all the time.

Figure 3. Sleep mode vs. LPRUN

|                                         | le el configuratione                                           |  |                      |  |  |

|-----------------------------------------|----------------------------------------------------------------|--|----------------------|--|--|

| Curve in <i>Figure</i> 3                | Black Green Red                                                |  |                      |  |  |

| Idle mode between transmissions         | Stop                                                           |  |                      |  |  |

| Debug interface                         | OFF                                                            |  |                      |  |  |

| Current average over phases 2, 3, and 4 | 34.9 μA         40.0 μA         42.0 μ                         |  | 42.0 µA              |  |  |

| Clock                                   | 130 kHz MSI                                                    |  |                      |  |  |

| Voltage regulator                       | LPRUN, then Range 3 Range 3                                    |  |                      |  |  |

| AHB/APB ratio                           | 1/1                                                            |  |                      |  |  |

| ULP/FWU                                 | +/+                                                            |  |                      |  |  |

| Baud rate                               | 9600 Bd                                                        |  |                      |  |  |

| SW used                                 | Blocking operation (Com polling)<br>with define RXSLEEP define |  | Also TXSLEEP defined |  |  |

Table 6. Configurations - Sleep mode vs. LPRUN

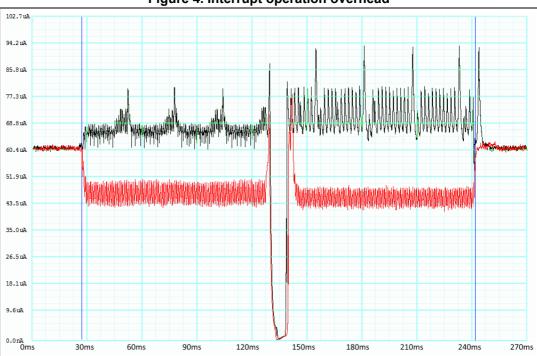

#### 7.1.3 Interrupt operation overhead

The interrupt mechanism on the Arm<sup>®</sup> Cortex<sup>®</sup> core is very efficient, but still represents an additional effort. This fact is best illustrated by comparison on the very minimum core clock suitable for interrupt driven operation of our example code, 250 kHz.

As shown in *Figure 4*, the IT code (black line) actually spends almost no time in Sleep mode (waiting for interrupt) and the power consumption is comparatively high. Blocking operation represented by the red line saves some energy in waiting for event (Tx buffer empty or Rx buffer full).

This comparison cannot be absolutely fair, as a different code is executed, nevertheless it holds significance of code optimization too.

Figure 4. Interrupt operation overhead

| Table 7. | Configurations | - Interrupt | operation |

|----------|----------------|-------------|-----------|

|          | ooningarations | micinapi    | operation |

| Curve in <i>Figure 4</i>                | Black                                                                                             | Red     |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------|---------|--|

| Idle mode between transmissions         | Stop                                                                                              |         |  |

| Debug interface                         | OFF                                                                                               |         |  |

| Current average over phases 2, 3, and 4 | 66.6 µA                                                                                           | 44.3 µA |  |

| Clock                                   | 250 kHz MSI                                                                                       |         |  |

| Voltage regulator                       | Range 3                                                                                           |         |  |

| AHB/APB ratio                           | 1/1                                                                                               |         |  |

| ULP/FWU                                 | +/+                                                                                               |         |  |

| Baud rate                               | 9600 Bd                                                                                           |         |  |

| SW used                                 | Interrupt operation (Com IT)<br>with defines RXSLEEP<br>and TXSLEEP<br>and TXSLEEP<br>and TXSLEEP |         |  |

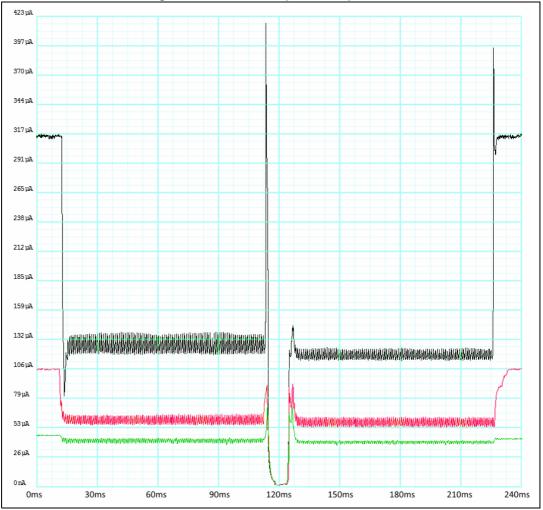

#### 7.1.4 Going to Stop between received bytes

The LPUARTs ability to wake from Stop on external event leads to possibility to enter the Stop mode even during pause between bytes in reception phase.

The best results comes with operational speeds slightly below the limit of voltage regulator Range 3, specifically 4 MHz MSI clock. In this way the interrupt overhead time is very short and the MCU spends most of the time in Stop mode.

Lower speeds actually lead to slightly higher power consumption during reception. The difference is not big, just around 10%. Yet still using polling and very slow clock setting the power consumption can be even lower than this, at the expenses of the flexibility of serving any other tasks.

Figure 5. Using the Stop during data reception

| Curve in <i>Figure 5</i>           | Black Red                                                    |  |  |

|------------------------------------|--------------------------------------------------------------|--|--|

| Idle mode between<br>transmissions | Stop                                                         |  |  |

| Debug interface                    | OFF                                                          |  |  |

| Current average                    | 55.5 μA (Rx only) 61.8 μA (Rx only)                          |  |  |

| Clock                              | 4 MHz MSI 500 kHz MSI                                        |  |  |

| Voltage regulator                  | Range 3                                                      |  |  |

| AHB/APB ratio                      | 1/1                                                          |  |  |

| ULP/FWU                            | +/+                                                          |  |  |

| Baud rate                          | 9600 Bd                                                      |  |  |

| SW used                            | Interrupt operation (Com IT) with defines RXSTOP and TXSLEEP |  |  |

#### 7.1.5 Different oscillator clock speeds

Using the MSI clock the application computing power and power consumption can be easily tuned to imminent needs of the system. It is of course possible to change the clock settings on the fly, during execution.

*Figure 6* shows the test execution at 2 MHz (black line), 500 kHz (red line) and 130 kHz (green line). The difference is large, but using the Sleep mode between both transmitted and received bytes the duty cycle makes it less prominent, at higher speeds the core spends more time in Low-power state.

There is, of course, no observable difference during the Stop mode.

Figure 6. Core clock speed comparison

#### Table 9. Configurations - Core clock speed

| Curve in <i>Figure 6</i>        | Black Green Red |      | Red |

|---------------------------------|-----------------|------|-----|

| Idle mode between transmissions |                 | Stop |     |

| Debug interface                 |                 | OFF  |     |

AN4635 Rev 9

| Curve in <i>Figure 6</i>                | Black                                                             | Groop     | Red     |  |  |

|-----------------------------------------|-------------------------------------------------------------------|-----------|---------|--|--|

| Curve in Figure o                       | DIACK                                                             | Green Red |         |  |  |

| Current average over phases 2, 3, and 4 | 136.6 µA                                                          | 42 µA     | 57.1 µA |  |  |

| Clock                                   | 2 MHz MSI 130 kHz MSI 500 kHz N                                   |           |         |  |  |

| Voltage regulator                       | Range 3                                                           |           |         |  |  |

| AHB/APB ratio                           | 1/1                                                               |           |         |  |  |

| ULP/FWU                                 | +/+                                                               |           |         |  |  |

| Baud rate                               | 9600 Bd                                                           |           |         |  |  |

| SW used                                 | Blocking operation (Com polling) with RXSLEEP and TXSLEEP defined |           |         |  |  |

Table 9. Configurations - Core clock speed (continued)

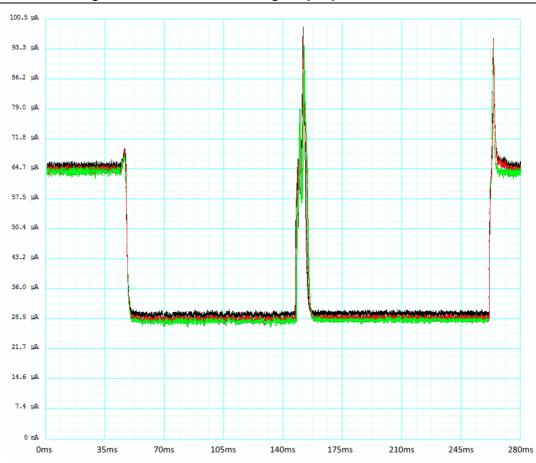

### 7.1.6 Changing AHB divider ratio

Changing the AHB divider ratio leads to decreased power consumption since most of the circuitry runs at lower frequency.

This is demonstrated in *Figure* 7, where the black line is the current absorption of the example running at 1 MHz MSI clock, and the red line is the same code running with AHB divider set to 4. If the clock can be directly configured to lower frequency, it is always better to choose this option. The green line represents the same example, only the MSI oscillator is set directly to 250 kHz. Proven by the difference between Sleep mode and run phase the actual processing power is the same, but the solution without AHB divider is more efficient.

Use of the AHB divider only makes sense with external clock or if there is necessity to use the HSI.

Figure 7. Lowering oscillator speed compared to AHB divider

| Table 10. Configurations - AHB divider |

|----------------------------------------|

|----------------------------------------|

| Curve in <i>Figure</i> 7                | Black                                                             | Green       | Red       |

|-----------------------------------------|-------------------------------------------------------------------|-------------|-----------|

| Idle mode between<br>transmissions      | Stop                                                              |             |           |

| Debug interface                         | OFF                                                               |             |           |

| Current average over phases 2, 3, and 4 | 75.9 µA                                                           | 44.3 µA     | 63.9 µA   |

| Clock                                   | 1 MHz MSI                                                         | 250 kHz MSI | 1 MHz MSI |

| Voltage regulator                       | Range 3                                                           |             |           |

| AHB/APB ratio                           | 1/1 4/1                                                           |             |           |

| ULP/FWU                                 | +/+                                                               |             |           |

| Baud rate                               | 9600 Bd                                                           |             |           |

| SW used                                 | Blocking operation (Com polling) with RXSLEEP and TXSLEEP defined |             |           |

### 7.1.7 Different peripheral clock settings

DMA based communication was measured on three different APB clock divider settings, as shown in *Figure 8*, where the black line represents current consumption with no divider, the red and green lines with divider set to 4 and to 8, respectively.

Figure 8. Three different settings of peripheral clock divider

| Table 11. | Configurations | - Clock | divider |

|-----------|----------------|---------|---------|

|           | Soundarianons  | Olook   | annaci  |

| Curve in <i>Figure 8</i>                | Black       | Red     | Green   |

|-----------------------------------------|-------------|---------|---------|

| Idle mode between transmissions         | Stop        |         |         |

| Debug interface                         | OFF         |         |         |

| Current average over phases 2, 3, and 4 | 31.5 µA     | 30.5 µA | 30.1 µA |

| Clock                                   | 250 kHz MSI |         |         |

| Voltage regulator                       | Range 3     |         |         |

| AHB/APB ratio                           | 1/1         | 1/4     | 1/8     |

| ULP/FWU                                 | +/+         |         |         |

28/53

| Curve in <i>Figure 8</i> | Black                                                       | Red | Green |

|--------------------------|-------------------------------------------------------------|-----|-------|

| Baud rate                | 9600 Bd                                                     |     |       |

| SW used                  | DMA operation (Com DMA) with half buffer interrupt disabled |     |       |

The power trace of the DMA operated example is different from the interrupt or blocking mode code execution. There is a peak in half of the transmission, caused by the half message interrupt. Then for half of the reply data reception the core stays in Sleep mode, it is only active during the second half. Different arrangement is of course possible.

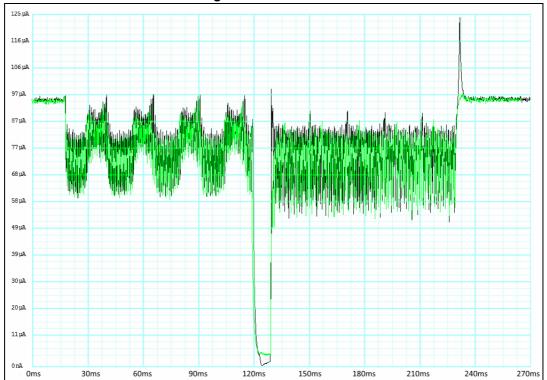

#### 7.1.8 ULP bit setting

The role of the ULP bit is to disconnect the internal voltage reference during Stop mode. The power analysis screen-shot in *Figure 9* illustrates that this setting (black line) achieves lower power consumption in the Stop mode, but produces significant peaks when waking up (compared to green trace without ULP).

The microcontroller waiting for incoming data in the ULP mode consumes approximately 0,8  $\mu$ A compared to almost 3  $\mu$ A without ULP mode, but if it wakes from idle mode too frequently, the effect is negated by the voltage reference startup peaks.

Figure 9. ULP bit effect

| Curve in <i>Figure</i> 9                | Black                                                        | Green   |  |  |

|-----------------------------------------|--------------------------------------------------------------|---------|--|--|

| Idle mode between<br>transmissions      | Stop                                                         |         |  |  |

| Debug interface                         | O                                                            | OFF     |  |  |

| Current average over phases 2, 3, and 4 | 74.5 μΑ                                                      | 72.6 µA |  |  |

| Clock                                   | 500 kHz MSI                                                  |         |  |  |

| Voltage regulator                       | Ran                                                          | Range 3 |  |  |

| AHB/APB ratio                           | 1/1                                                          |         |  |  |

| ULP/FWU                                 | +/+                                                          | -/-     |  |  |

| Baud rate                               | 9600 Bd                                                      |         |  |  |

| SW used                                 | Interrupt operation (Com IT) with defines RXSTOP and TXSLEEP |         |  |  |

Table 12. Configurations - ULP bit effect

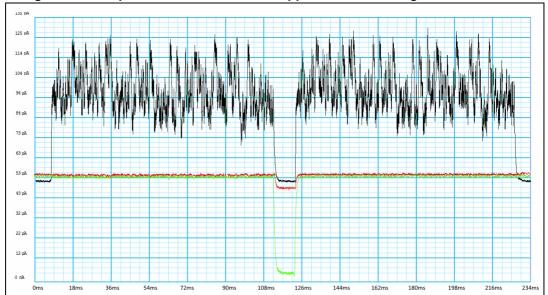

### 7.1.9 Higher communication speed

While no advanced power saving features of the LPUART can be used on higher communication speeds (as compared with regular USART peripheral), still the LPUART simpler circuitry will result in lower power consumption (red line) compared to a full featured USART (black line), see *Figure 10*.

Figure 10. Operating at 57600 Bd

| Curve in <i>Figure 10</i>               | Black                                                                                                                     | Red      |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| Idle mode between transmissions         | Stop                                                                                                                      |          |  |  |

| Debug interface                         | ON                                                                                                                        |          |  |  |

| Current average over phases 2, 3, and 4 | 434.5 µA                                                                                                                  | 415.2 μA |  |  |

| Clock                                   | 4 MHz MSI                                                                                                                 |          |  |  |

| Voltage regulator                       | Range 1                                                                                                                   |          |  |  |

| AHB/APB ratio                           | 1/1                                                                                                                       |          |  |  |

| ULP/FWU                                 | +/+                                                                                                                       |          |  |  |

| Baud rate                               | 57600 Bd                                                                                                                  |          |  |  |

| SW used                                 | Interrupt operation (Com IT) Interrupt operation (Com IT)<br>modified with USART on SYSCLK modified with LPUART on SYSCLK |          |  |  |

Table 13. Configurations - Higher communication speed

Note: The timing is slightly different for the 2 cases. This is a common problem when MSI is used to clock the LPUART peripheral. MSI clock is generally less precise than LSE or even HSI.

#### 7.1.10 Wake-up from Stop mode on HSI

Another possible option at higher communication speeds is to exploit the feature of wake-up from Stop mode with peripheral clocked from the HSI clock (see *Figure 11*).

The HSI oscillator in Stop mode draws approximately the same current as the MSI in Sleep mode at 2 MHz. It is however more precise, and provides the core with more processing power in Run mode.

Note that the timing with MSI is slightly off in the transmission phase. This is a common problem when MSI is used to clock the LPUART peripheral.

| Table 14. Configurations - H | ISI vs. MSI |

|------------------------------|-------------|

|------------------------------|-------------|

| Curve in <i>Figure 11</i>               | Black Red |           |  |

|-----------------------------------------|-----------|-----------|--|

| Idle mode between<br>transmissions      | Stop      | Sleep     |  |

| Debug interface                         | OFF       |           |  |

| Current average over phases 2, 3, and 4 | 369.1 μA  | 329.7 µA  |  |

| Clock                                   | 4 MHz HSI | 4 MHz MSI |  |

| Voltage regulator                       | Range 3   |           |  |

| AHB/APB ratio                           | 1/1       |           |  |

| ULP/FWU                                 | +/+       |           |  |

| Curve in <i>Figure 11</i> | Black Red                    |  |  |  |

|---------------------------|------------------------------|--|--|--|

| Baud rate                 | 57600 Bd                     |  |  |  |

| SW used                   | Interrupt operation (Com IT) |  |  |  |

Table 14. Configurations - HSI vs. MSI (continued)

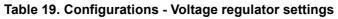

### 7.1.11 Voltage regulator settings

Setting lower core voltage level is an easy and straightforward way to save energy.

In *Figure 12* it is demonstrated that even with HSI clock the run mode can be significantly more current-hungry just by changing the voltage.

Note that the setting has little or no influence on idle mode.

Figure 12. Comparison between voltage regulator settings

| Table 15. Configurations | - Voltage regulator | settings |

|--------------------------|---------------------|----------|

|--------------------------|---------------------|----------|

| Curve in <i>Figure 12</i>       | Red   | Green | Black |

|---------------------------------|-------|-------|-------|

| Idle mode between transmissions | Sleep |       |       |

| Debug interface                 | OFF   |       |       |

| Red                     | Green                      | Black                                                                                                     |  |  |

|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| 296.9 µA                | 300.8 µA                   | 301.1 µA                                                                                                  |  |  |

| 4 MHz HSI               |                            |                                                                                                           |  |  |

| Range 3                 | Range 2                    | Range 1                                                                                                   |  |  |

| 1/1                     |                            |                                                                                                           |  |  |

| 9600 Bd                 |                            |                                                                                                           |  |  |

| DMA operation (Com DMA) |                            |                                                                                                           |  |  |

|                         | Red<br>296.9 μA<br>Range 3 | Red     Green       296.9 μA     300.8 μA       4 MHz HSI       Range 3     Range 2       1/1     9600 Bd |  |  |

Table 15. Configurations - Voltage regulator settings (continued)

### 7.1.12 GPIO pull-up

*Figure 13* demonstrates the energetic costs of enabling the GPIO pull-up, in this case on the transmission line. Black line refers to internal GPIO pull-up enabled, red line to no pull-up.

It is clearly visible that no other phases are affected by extra power consumption.

Figure 13. GPIO internal pull-up

| Table 16 | Configurations | - GPIO | pull-up |

|----------|----------------|--------|---------|

|----------|----------------|--------|---------|

| Curve in <i>Figure 13</i>          | Black | Red |  |

|------------------------------------|-------|-----|--|

| Idle mode between<br>transmissions | Stop  |     |  |

| Debug interface                    | OF    | F   |  |

| Curve in <i>Figure 13</i>               | Black Red                                                              |                              |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------|------------------------------|--|--|--|

| Current average over phases 2, 3, and 4 | 87.8 µA                                                                | 66.6 µA                      |  |  |  |

| Clock                                   | 250 kHz MSI                                                            |                              |  |  |  |

| Voltage regulator                       | Range 3                                                                |                              |  |  |  |

| AHB/APB ratio                           | 1/1                                                                    |                              |  |  |  |

| ULP/FWU                                 | +/+                                                                    |                              |  |  |  |

| Baud rate                               | 9600 Bd                                                                |                              |  |  |  |

| SW used                                 | Interrupt operation (Com IT) modified<br>with Tx line internal PULL UP | Interrupt operation (Com IT) |  |  |  |

#### Table 16. Configurations - GPIO pull-up (continued)

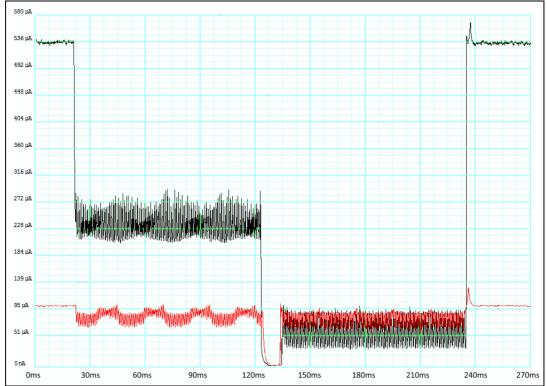

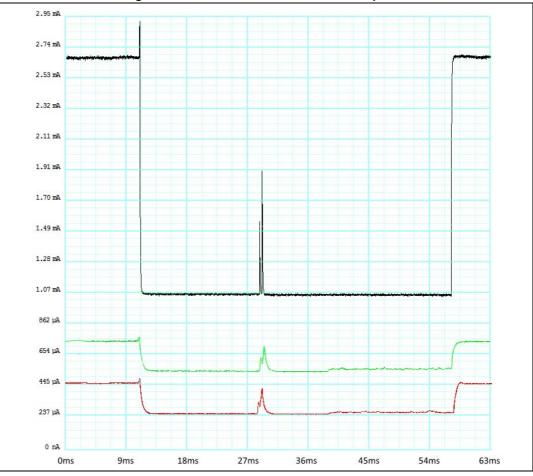

### 7.2 Measurements on STM32L476 Nucleo board

#### 7.2.1 Three approaches at a glance

In this section the advantages and disadvantages of the three basic approaches (DMA, Polling and Interrupt) to govern the communication will be compared.

Looking at *Figure 14*, the DMA one wins this comparison, but, if the pause before reply had been longer, it would have lost by a wide margin. Polling would then appear as the most efficient, but it assumes that a single task be processed. Interrupt seems to solve this problem, but at 200 kHz system clock it has no margin to do so (judging by the negligible time spent in Sleep between bytes).

While DMA and Polling driven communications are still operational at 100 kHz minimal MSI setting, Interrupt operation is not.

Figure 14. Comparison of three different approaches to manage communication

| Curve in <i>Figure 14</i>               | Black       | Red     | Green   |

|-----------------------------------------|-------------|---------|---------|

| Idle mode                               | Stop2       |         | Sleep   |

| Debug interface                         | OFF         |         |         |

| Current average over phases 2, 3, and 4 | 64.1 µA     | 51.6 µA | 49.4 µA |

| Clock                                   | 200 MHz MSI |         |         |

AN4635 Rev 9

| Curve in <i>Figure 14</i> | Black Red Green                                          |                                                       |                                                           |  |

|---------------------------|----------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|--|

| Voltage regulator         |                                                          | Low-power run                                         |                                                           |  |

| AHB/APB ratio             | 1/1                                                      |                                                       |                                                           |  |

| Baud rate                 | 9600 Bd                                                  |                                                       |                                                           |  |

| SW used                   | Interrupt driven<br>(Com IT) with Sleep<br>between bytes | POLL operation with<br>TXSLEEP and<br>RXSLEEP defines | DMA stream<br>(Com DMA) with half<br>buffer interruptions |  |

Table 17. Configurations - Managing communication (continued)

#### 7.2.2 Simple polling mode on low core frequency

After reset the MCU initializes with MSI oscillator running at 4 MHz, a compromise between low-power consumption and acceptable communication speed. A lower frequency is needed to establish a communication link using LPUART. Note that at this pace an interrupt from different peripheral can disrupt the ongoing communication.

Figure 15 shows the consumption profile using different low speeds of the MSI oscillator.

Figure 15. Polling communication at minimum settings

| Curve in <i>Figure 15</i>               | Black                                   | Red         | Green       |  |  |

|-----------------------------------------|-----------------------------------------|-------------|-------------|--|--|

| Idle mode                               | Stop2                                   |             |             |  |  |

| Debug interface                         |                                         | OFF         |             |  |  |

| Current average over phases 2, 3, and 4 | 81.2 μΑ 49.7 μΑ 44.9 μΑ                 |             |             |  |  |

| Clock                                   | 800 kHz MSI                             | 200 kHz MSI | 100 kHz MSI |  |  |

| Voltage regulator                       | Low-power run                           |             |             |  |  |

| AHB/APB ratio                           | 1/1                                     |             |             |  |  |

| Baud rate                               | 9600 Bd                                 |             |             |  |  |

| SW used                                 | POLL operation with TXSLEEP and RXSLEEP |             |             |  |  |

Table 18. Configurations - Polling

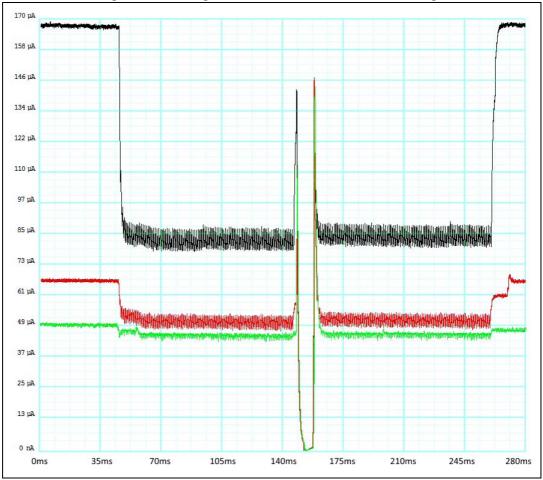

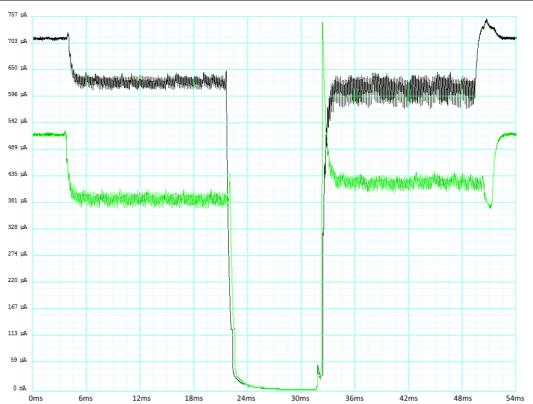

### 7.2.3 The role of voltage regulator settings

An important step towards lower power consumption is the use of regulator settings appropriate to the actual core frequency. Speed of 2 MHz (MSI Range 5) is the top setting supported by the Low-power run mode. Remaining connected to the main regulator (in *Figure 16* this is emphasized by using it even during Sleep) a lot of energy is wasted.

Figure 16. Voltage regulator settings

| Curve in <i>Figure 16</i>               | Black                                                       | Red     | Green         |  |

|-----------------------------------------|-------------------------------------------------------------|---------|---------------|--|

| Idle mode                               | Sleep                                                       |         |               |  |

| Debug interface                         | OFF                                                         |         |               |  |

| Current average over phases 2, 3, and 4 | 244.4 μΑ 215.5 μΑ 139.1 μΑ                                  |         |               |  |

| Clock                                   | 2 MHz MSI                                                   |         |               |  |

| Voltage regulator                       | Range 1                                                     | Range 2 | Low-power run |  |

| AHB/APB ratio                           | 1/1                                                         |         |               |  |

| Baud rate                               | 9600 Bd                                                     |         |               |  |

| SW used                                 | DMA operation (Com DMA) with half buffer interrupt disabled |         |               |  |

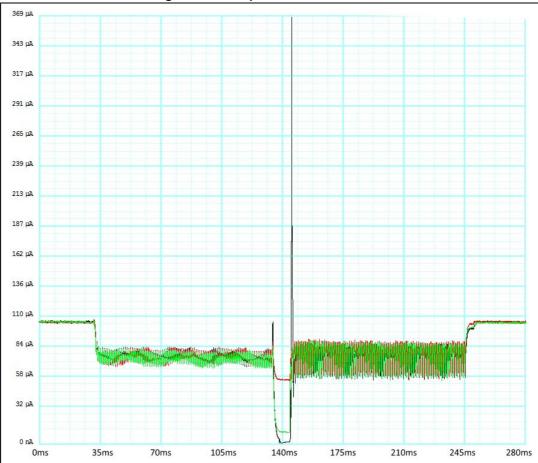

#### 7.2.4 Idle modes compared

Microcontrollers of the L4 series feature three basic Idle modes, namely Sleep, Stop1 and Stop2.

Note, in *Figure* 17, how Stop 2 minimizes the power consumption drastically, and how waking up produces a notable peak. This causes the Stop1 to outperform Stop2 in measured case of approximately 10 ms of Idle. Main reason of this peak is the fact that the Stop2 mode cannot be entered directly from the Low-power mode. Main regulator must be ON when entering and leaving the Stop2.

#### Table 20. Configurations - Idle modes

| Curve in <i>Figure 17</i>               | Black                              | Red   | Green |  |  |

|-----------------------------------------|------------------------------------|-------|-------|--|--|

| Idle mode                               | Stop2                              | Sleep | Stop1 |  |  |

| Debug interface                         | OFF                                |       |       |  |  |

| Current average over phases 2, 3, and 4 | 73.2 μΑ 75.6 μΑ 72.8 μΑ            |       |       |  |  |

| Clock                                   | 400 kHz MSI                        |       |       |  |  |

| Voltage regulator                       | Low-power run                      |       |       |  |  |

| AHB/APB ratio                           | 1/1                                |       |       |  |  |

| Baud rate                               | 9600 Bd                            |       |       |  |  |

| SW used                                 | IT operation (Com IT) with Rx Stop |       |       |  |  |

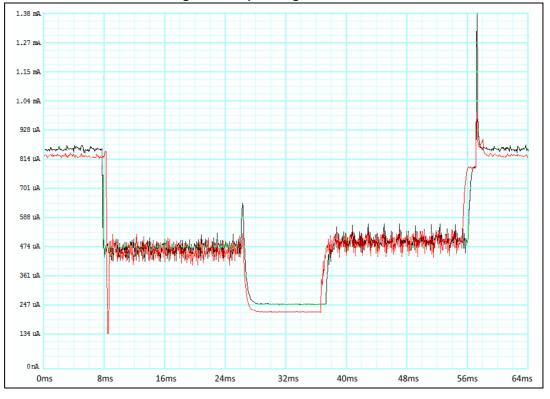

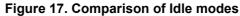

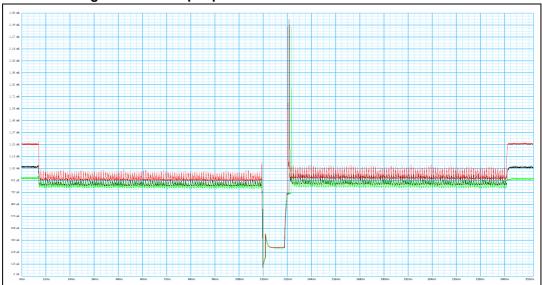

#### 7.2.5 Use of MSI PLL-mode for higher speeds

Higher communication speeds require an LPUART clock source different from LSE.

System clock driven by MSI up to 48 MHz can be used, configured in PLL-mode, in which it is auto-calibrated using the LSE. An obvious but not efficient solution is to use the HSI clock with dividers (such as the AHB).

HSE external source is another option. The measurement shown in *Figure 18* compares the HSI configurations using the MSI PLL-mode to get lower clock frequency and lower consumption.

Figure 18. HSI and PLL current consumption

| Curve in <i>Figure 18</i>               | Black   | Green    | Red                                             |  |

|-----------------------------------------|---------|----------|-------------------------------------------------|--|

| Idle mode                               | Sleep   |          |                                                 |  |

| Debug interface                         | OFF     |          |                                                 |  |

| Current average over phases 2, 3, and 4 | 1.05 mA | 0.536 mA | 0.250 mA                                        |  |

| Clock                                   | HSI16   |          | MSI auto-callibrated using LSE;<br>Sysclk 2 MHz |  |

| Table 21. Configurations - fior and field (Continued) |                                                             |     |               |  |

|-------------------------------------------------------|-------------------------------------------------------------|-----|---------------|--|