# AN5417

Application note

Low consumption standby implementation with STSPIN32F0 and STSPIN32G0 families

### Introduction

The diffusion of the Lithium-ion batteries, thanks to their high energy density, extended the concept of portability and cordless to a wide range of products. Power tools, vacuum cleaners and lawn mowers are only a few examples of this trend.

A key requirement of these applications is the low quiescent consumption extending the battery life when the equipment is stored.

This document describes an effective and affordable implementation of this feature using the brushless motor controllers of the STSPIN32F0 and STSPIN32G0 families.

# 1 List of abbreviations

Following is a list of the abbreviations used in this document:

#### Table 1. List of abbreviations

| Abbreviation | Meaning                                                     |

|--------------|-------------------------------------------------------------|

| MCU          | Microcontroller Unit                                        |

| PMOS         | P-channel metal-oxide-semiconductor field-effect transistor |

| NMOS         | N-channel metal-oxide-semiconductor field-effect transistor |

| AMR          | Absolute maximum rating                                     |

# Basic principle and proposed solution

7/

The best way to reduce the quiescent consumption to the lowest level possible, is disconnecting the battery from the unused circuitry. This is usually done though a PMOS placed between the battery (source) and the circuitry (drain).

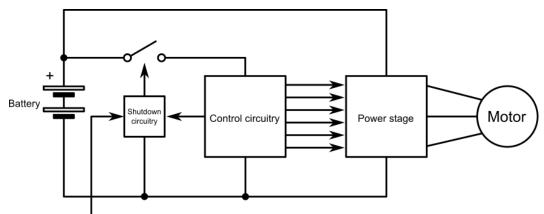

In the proposed solution (see Figure 1), the disconnected circuitry is the motor controller together with all the devices dedicated to the control of the motor (e.g. Hall-effect sensors, encoders, NTC, ...).

On the contrary, the power stage is directly connected to the battery. The main reason is that the current required to drive the motor is typically too high to be managed by a PMOS-based switch.

The key points to be considered during the design of this solution are:

- 1. The PMOS performing the disconnection must be able to sustain the operating current of the circuitry.

- 2. Take care of parasitic connections with other circuitries that cannot be disconnected from the battery (e.g. battery monitor, power stage, ...).

- 3. The PMOS should be disabled by default. It is not a must, but the low-consumption mode is normally considered the idle status of the equipment.

User interface

#### 2.1 Turn-on through external trigger switch

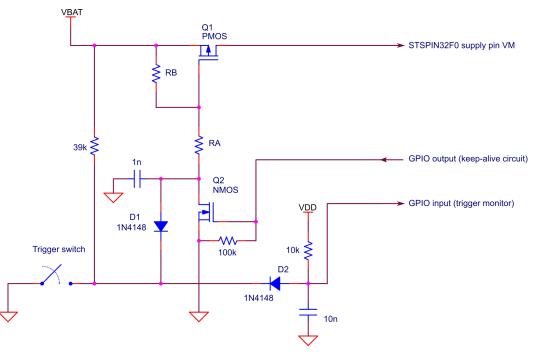

One of the most common ways to enable a battery-supplied tool is through a mechanical switch. As soon as the switch is closed, the tool returns operative and the motor must be driven as required by the control algorithm. In the proposed schematic of Figure 2 closing the trigger switch, the gate of the PMOS is forced low connecting the battery to the control circuitry. The Vgs of the PMOS is calculated by Eq. (1). In order to guarantee a good turn-on of D1 diode, a bias current of 100 µA or more is recommended (see Eq. (2) for an approximated value).

#### Equation 1

$$V_{gs,Q1} = \left(V_{F,D1} - V_{BAT}\right) \frac{R_B}{R_A + R_B}$$

Equation 2

(1)

Figure 2. Turn-on through external trigger switch – schematic example

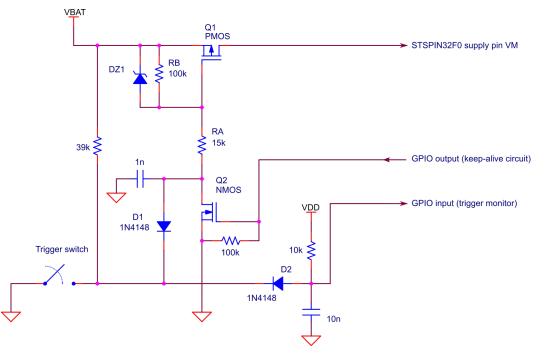

When the battery voltage is above the absolute rating of the PMOS' Vgs (in most cases 20 V), it is safer to use a solution based on Zener diodes (Figure 3). In this case, RB can be significantly higher than RA and the Vgs is imposed by the Zener voltage of DZ1. In this solution it is important to verify that the power dissipation of DZ1, RA and D1 are still in a safe operating area (see equations below):

#### **Equation 3**

(3)

$$P_{d,DZ1} = V_{Z,DZ1} \times I_{Z,DZ1} = V_{Z,DZ1} \times \left(\frac{V_{BAT} - V_{Z,DZ1} - V_{F,D1}}{R_A} - \frac{V_{Z,DZ1}}{R_B}\right)$$

**Equation 4**

$$P_{d,D1} = V_{F,D1} \times I_{F,D1} = V_{F,D1} \times \left(\frac{V_{BAT} - V_{Z,DZ1} - V_{F,D1}}{R_A}\right)$$

**Equation 5**

(5)

(4)

$$P_{d,RA} = \frac{\left(V_{BAT} - V_{Z,DZ1} - V_{F,D1}\right)^2}{R_A}$$

#### Figure 3. Turn-on through external trigger switch – schematic example with Zener diode

### 2.2 Keep-alive circuit

As soon as the PMOS connects the battery to the brushless motor controller and the VM rises above the turn-on threshold, the power-up sequence starts, and the integrated buck regulator performs the soft-start ramp suppling the MCU.

Details of the above sequence are listed in the datasheet of the devices.

When the MCU is operative, it is possible to keep the PMOS closed using Q2 NMOS. In fact, it acts as an MCUdriven switch in parallel to the external trigger switch.

In this way, the firmware takes control of the connection between the battery and the control circuitry, allowing the code to perform a safe switch-off, for example, braking the motor.

#### Table 2. Q2 NMOS key requirements

| Symbol  | Characteristic                | Recommended value |

|---------|-------------------------------|-------------------|

| VDS,max | Drain-source maximum voltage  | ≥ 1.2 × VBAT      |

| VGS(th) | Gate-source threshold voltage | ≤ 2.5 V           |

It is recommended to set this GPIO output at the very beginning of the MCU's initialization.

### 2.3 Detection of external trigger switch status

While the motor controller is kept supplied by the keep-alive circuit (see Section 2.2), the actual status of the external trigger switch must be constantly monitored in order to execute the shut-down sequence when it is released.

In the proposed circuit, the monitoring GPIO is connected to the switch thought the D2 diode.

As long as the switch is closed, the GPIO is forced low through D2. Releasing the switch, D2 turns off and the GPIO is pulled up by the resistor. A strong filtering of the signal is recommended.

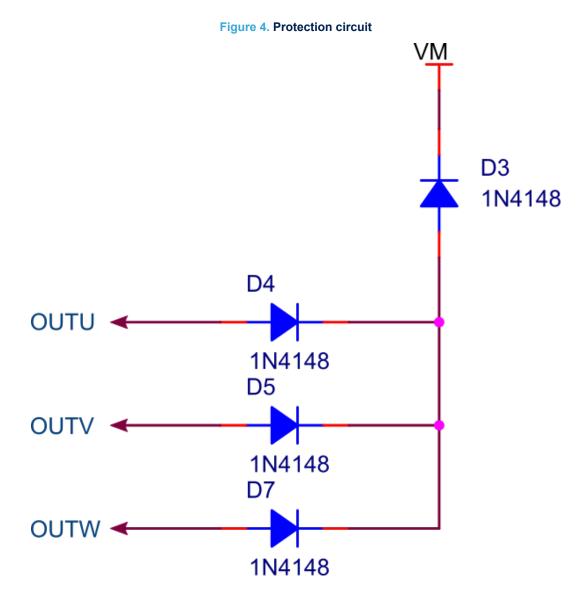

### 3 Protection against reverse biasing from power stage outputs

As shown in the block diagram of Figure 1, the battery is always connected to the power stage while the control side is disconnected through the PMOS switch. In this way, the voltage of the power stage outputs ( $V_{OUT}$ ) can be higher than the control logic supply ( $V_M$ ) violating the AMR limit of the gate driving circuitry:  $V_{OUT,max} = V_M + 2 V$ . The device can be protected against this condition by adding protection diodes between each output and the  $V_M$  supply, as shown in Figure 4.

The circuit imposes the Eq. (6) condition keeping the device within AMR. During normal operation the diodes are always off.

**Equation 6**

(6)

$MAX(V_{OUTx} - V_M) = 2 \times V_F \cong 1.2 V$

### **Revision history**

#### Table 3. Document revision history

| Date        | Version | Changes                                                                         |

|-------------|---------|---------------------------------------------------------------------------------|

| 05-Nov-2019 | 1       | Initial release.                                                                |

| 17-Jan-2025 | 2       | Changed title in cover page; changes to extend the AN to the STSPIN32G0 family. |

## Contents

| 1    | List   | of abbreviations                                        | 2  |

|------|--------|---------------------------------------------------------|----|

| 2    | Basi   | c principle and proposed solution                       | 3  |

|      | 2.1    | Turn-on through external trigger switch                 | 3  |

|      | 2.2    | Keep-alive circuit                                      | 5  |

|      | 2.3    | Detection of external trigger switch status             | 5  |

| 3    | Prot   | ection against reverse biasing from power stage outputs | 6  |

| Revi | sion   | history                                                 | 7  |

| List | of tab | oles                                                    | 9  |

| List | of fig | ures                                                    | 10 |

# List of tables

| Table 1. | List of abbreviations     | 2 |

|----------|---------------------------|---|

| Table 2. | Q2 NMOS key requirements  | 5 |

| Table 3. | Document revision history | 7 |

# List of figures

| Figure 1. | Basic principle block diagram                                                | 3 |

|-----------|------------------------------------------------------------------------------|---|

| Figure 2. | Turn-on through external trigger switch – schematic example                  | 4 |

| Figure 3. | Turn-on through external trigger switch – schematic example with Zener diode | 5 |

| Figure 4. | Protection circuit                                                           | 6 |

#### IMPORTANT NOTICE - READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved