## Migrating from STM32MP15x to STM32MP25x MPUs

#### Introduction

The STM32MP251, STM32MP253, STM32MP255 and STM32MP257 devices are part of the STM32 Arm<sup>®</sup> Cortex<sup>®</sup> microprocessors (MPUs) subclass; they all feature a Cortex-M33, a Cortex-M0+, and depending on the part number, either a single-core or a dual-core Cortex-A35 and a graphics processing unit (GPU)/neural processing unit (NPU).

These devices are referred to as STM32MP25x in this document.

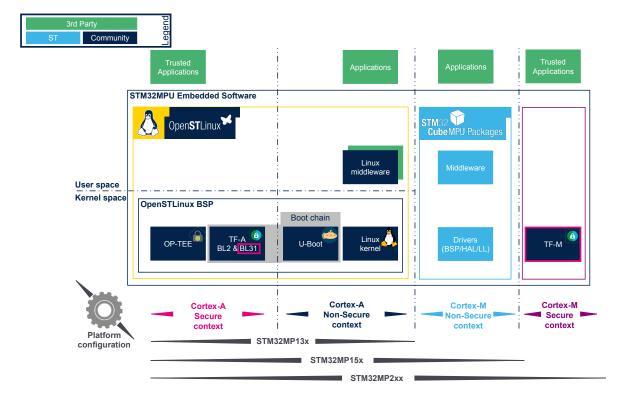

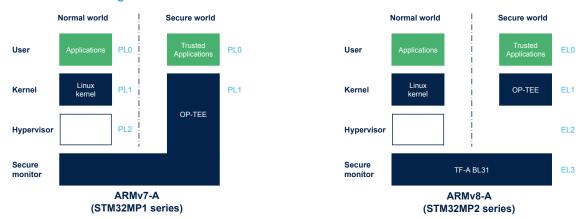

The Cortex-M33 inside the STM32MP25x devices is mostly backward compatible (for STM32Cube package) with the STM32MP15x devices. This compatibility allows the easy migration from an STM32MP15x device design to a similar STM32MP25x devices and to benefit from their significantly higher performances and security as well as advanced peripherals without adding any additional complexity. Similarly than to the STM32MP15x devices, the STM32MP25x high performance Cortex-A35 runs open operating systems like Linux<sup>®</sup>, which provides rich connectivity and the support of a software community. System configuration migration between different hardware using different device trees is supported with OpenSTLinux.

This application note provides information to facilitate the migration from an STM32MP15x design to an STM32MP25x design.

D3 domain (Cortex-M0+) has no equivalent on STM32MP15x devices, so not covered in this document.

New STM32MP25x features not present on STM32MP15x are not fully listed in this document as goal is migrating existing solution from previous product range. For whole coverage of STM32MP25x features, refer to STM32MP25x reference documents listed in Section 1.1: Reference documents.

Table 1. Applicable products

| Reference  | Product                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM32MP15x | STM32MP151A, STM32MP151C, STM32MP151D, STM32MP151F, STM32MP153A, STM32MP153C, STM32MP153D, STM32MP153F, STM32MP157A, STM32MP157C, STM32MP157D, STM32MP157F                                                     |

| STM32MP25x | STM32MP251A, STM32MP251C, STM32MP251D, STM32MP251F, STM32MP253A, STM32MP253C, STM32MP253D, STM32MP253F, STM32MP255A, STM32MP255C, STM32MP255D, STM32MP255F, STM32MP257A, STM32MP257C, STM32MP257D, STM32MP257F |

## 1 General information

This document applies to the STM32MP15x and STM32MP25x  $Arm^{\circledR}$ -based microprocesor.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## 1.1 Reference documents

Table 2. Reference documents

| Number | Reference  | Title                                                      |  |  |  |  |  |

|--------|------------|------------------------------------------------------------|--|--|--|--|--|

|        | STM32MP15x |                                                            |  |  |  |  |  |

| [1]    | RM0436     | STM32MP157 reference manual                                |  |  |  |  |  |

| [2]    | RM0442     | STM32MP153 reference manual                                |  |  |  |  |  |

| [3]    | RM0441     | STM32MP151 reference manual                                |  |  |  |  |  |

| [4]    | DS12505    | STM32MP157C/F datasheet                                    |  |  |  |  |  |

| [5]    | DS12504    | STM32MP157A/D datasheet                                    |  |  |  |  |  |

| [6]    | DS12503    | STM32MP153C/F datasheet                                    |  |  |  |  |  |

| [7]    | DS12502    | STM32MP153A/D datasheet                                    |  |  |  |  |  |

| [8]    | DS12500    | STM32MP151A/D datasheet                                    |  |  |  |  |  |

| [9]    | DS12501    | STM32MP151C/F datasheet                                    |  |  |  |  |  |

| [10]   | AN5031     | Getting started with STM32MP15x lines hardware development |  |  |  |  |  |

|        | STM32MP25x |                                                            |  |  |  |  |  |

| [11]   | RM0457     | STM32MP25x reference manual                                |  |  |  |  |  |

| [12]   | DS14285    | STM32MP25xA/D datasheet                                    |  |  |  |  |  |

| [13]   | DS14284    | STM32MP25xC/F datasheet                                    |  |  |  |  |  |

| [14]   | AN5489     | Getting started with STM32MP25x lines hardware development |  |  |  |  |  |

AN5718 - Rev 1 page 2/30

## 1.2 Glossary

**Table 3. Glossary**

| Term | Definition                                                                |

|------|---------------------------------------------------------------------------|

| ADC  | Analogue to digital converter                                             |

| CPU  | Central processing unit                                                   |

| DAC  | Digital to analog converter                                               |

| DDR  | Double density random access memory                                       |

| GPU  | Graphics processing unit                                                  |

| IC   | Integrated circuit                                                        |

| MCU  | Microcontroller unit                                                      |

| MPU  | Microprocessor unit                                                       |

| NPU  | Neural processing unit                                                    |

| OSTL | OpenSTLinux. Linux distribution based on the OpenEmbedded build framework |

| TSN  | Time sensitive networking defined by IEEE 802.1                           |

AN5718 - Rev 1 page 3/30

## 2 STM32MP15x lines overview

The STM32MP15x devices are part of the STM32MP1 series. Depending on the device part number, the system includes a Cortex-M4 and either a single-core or a dual-core Cortex-A7and a GPU.

The full featured system are listed in the table below and partitioned in:

- One MPU subsystem: dual Cortex-A7 with L2 cache

- One microprocessor (MCU) subsystem: Cortex-M4 with associated peripherals clocked according to central processor unit (CPU) activity

Table 4. Configuration of the lines of the STM32MP15x lines

| Devices    | Reference<br>manual | Cortex-A7<br>configuration | Cortex-M4 | GPU | DSI | FDCAN | Ethernet<br>port |

|------------|---------------------|----------------------------|-----------|-----|-----|-------|------------------|

| STM32MP151 | [3]                 | Single-core                | Yes       | No  | No  | No    | 1                |

| STM32MP153 | [2]                 | Dual-core                  | Yes       | No  | No  | Yes   | 1                |

| STM32MP157 | [1]                 | Dual-core                  | Yes       | Yes | Yes | Yes   | 1                |

AN5718 - Rev 1 page 4/30

## 3 STM32MP25x lines overview

The STM32MP25x devices are part of the STM32MP2 series devices. Depending on the device part number, the system includes a Cortex-M33 and either a single-core or a dual-core Cortex-A35 and a GPU/NPU.

The full featured system is described in the table below, and is partitioned as listed below:

- One MPU subsystem: dual Cortex-A35 with L2 cache

- One MCU subsystem: Cortex-M35 with associated peripherals clocked according to CPU activity

Table 5. Configuration of the lines of the STM32MP25x lines

| Lines      | Reference<br>manual | Cortex-A35<br>configuration | Cortex-M33 | GPU/NPU <sup>(1)</sup> | DSI | FDCAN | Ethernet ports   | LVDS |

|------------|---------------------|-----------------------------|------------|------------------------|-----|-------|------------------|------|

| STM32MP251 |                     | Single-core                 | Yes        | No                     | No  | No    | 1                | No   |

| STM32MP253 | [44]                | Dual-core                   | Yes        | No                     | No  | Yes   | 2                | No   |

| STM32MP255 | [11]                | Dual-core                   | Yes        | Yes                    | Yes | Yes   | 2                | Yes  |

| STM32MP257 |                     | Dual-core                   | Yes        | Yes                    | Yes | Yes   | 3 <sup>(2)</sup> | Yes  |

- 1 This includes hardware video encode/decode

- 2. With a two port TSN compliant switch

The STM32MP25x lines offer extra performance compared to the STM32MP15x devices. The STM32MP25x devices include similar set of peripherals, some with advanced features and higher performances compared to the STM32MP15x devices such as:

#### **Processing**

- Single or dual core Arm Cortex-A35 1200 MHz 32/64-bit processor:

- L1 and L2 caches

- 1500 MHz frequency overdrive

- 3D graphic processing unit (GPU) running at 800 MHz

- 900 MHz frequency overdrive

- Al neural processing unit (NPU) running at 800 MHz

- 900 MHz frequency overdrive

- Hardware video encoder/decoder

- Arm Cortex-M33 400 MHz processor

- L1 caches

- Arm Cortex-M0+ smart run domain

- HPDMA + LPDMA

- External LPDDR4/DDR4 16/32-bits 1200 MHz or DDR3L 16/32-bits 1066 MHz

- High-performance timers and low-power timers

- Digital temperature sensor

#### Connectivity

- USB2.0 high-speed host (up to 480 Mbits/s) with embedded PHY

- USB3.0 SuperSpeed dual role (up to 5 Gbits/s) with embedded PHYs

- USB Type-C power delivery

- PCI express (up to 5 Gbits/s) with embedded PHY

- 3 x SDMMC/SDIO

- 2 x OCTOSPI

- FMC for PSRAM or SLC NAND-flash

- USART, UART

AN5718 - Rev 1 page 5/30

- SPI/I<sup>2</sup>S

- I<sup>2</sup>C, I3C

- 3 x (TT)FDCAN 2.0

- 3 x Gigabit Ethernet with TSN, IEEE 1588 support

- CSI-2 at 2 x 2.5 Gbps with lite-ISP

- DSI at 4 x 2.5 Gbps

- LVDS dual link 4 x 1.1 Gbps

#### **Audio**

- 4 x SAI

- 8 x MDF

- 1 x ADF

- 4 x SPDIF-RX

#### Other

- Resource isolation framework

- 16- and 32-bit timers

- 3 x 12-bit ADC (5 MSPS) with voltage reference buffer (VREFBUF)

- Tj: -40°C to 125°C

This migration guide covers the migration from STM32MP15x devices towards STM32MP25x devices. This document only the features that are common to the STM32MP25x and the STM32MP15x devices. For more detailed information on the STM32MP25x devices, refer the appropriate reference manuals and datasheets.

There are some features available on STM32MP15x lines that are not present in the STM32MP25x devices. These features are listed below:

- HDMI-CEC

- MDIOS

- DAC

Security concept is different/enhanced, with different blocks names used.

AN5718 - Rev 1 page 6/30

## 4 Hardware migration

There is no compatible package between STM32MP15x devices and STM32MP25x devices, but a good candidate for migration towards an STM32MP15x device can be chosen by considering the following criteria:

- GPIO: equivalent number of available GPIOs. Precise count should be done for each application use case.

- Size: the package size (from 10×10 to 18×18)

- PCB: the PCB technology cost (TFBGA pitch 0.5 or LFBGA pitch 0.8)

- DDR: the DDR bus width (16- or 32-bit) which is linked to the maximum Cortex-A and GPU performances.

The table below presents a cross reference to assist the user to choose the closest migration candidate in number of GPIO, but also according to some different criteria priority.

Table 6. Cross-selector based on GPIO count, ball pitch and package size

| Product             | GPIO | Package   | Size (mm) | Ball pitch (mm) | DDR bus width | Priority | Closest reference | GPIO | Package  | Size (mm) | Ball pitch (mm) | DDR bus width |

|---------------------|------|-----------|-----------|-----------------|---------------|----------|-------------------|------|----------|-----------|-----------------|---------------|

| STM32MP15xxAA       | 176  | LFBGA448  | 18x18     | 8.0             | 32            | -        | STM32MP25xxAI     | 172  | VFBGA436 | 18x18     | 8.0             | 32            |

| STM32MP15xxAB       | 98   | LFBGA354  | 16x16     | 0.8             | 16            | PCB      | STM32MP25xxAI     | 172  | VFBGA436 | 18x18     | 8.0             | 32            |

| STIVISZIVIF TSXXAB  | 90   | LI BGA334 | 100.10    | 0.0             | 10            | DDR      | STM32MP25xxAL     | 144  | VFBGA361 | 10x10     | 0.5             | 16            |

| STM32MP15xxAC       | 148  | TFBGA361  | 12x12     | 0.40 0.5 00     |               | PCB      | STM32MP25xxAK     | 144  | VFBGA424 | 14x14     | 0.5             | 32            |

| 3 I WISZIVIP ISXXAC | 140  | II DGA301 | 12812     |                 |               | DDR      | STM32MP25xxAL     | 144  | VFBGA361 | 10x10     | 0.5             | 16            |

| STM32MP15xxAD       | 98   | TFBGA257  | 10x10     | 0x10 0.5 16     |               | -        | STM32MP25xxAL     | 144  | VFBGA361 | 10x10     | 0.5             | 16            |

AN5718 - Rev 1 page 7/30

## 4.1 Power supply aspects

To ensure better performance and better power consumption, STM32MP25x lines provide separated supply voltage domain for Cortex-A35 as well as for GPU/NPU.

When the activity requires or permits, these supplies could be overdriven to increase performances, lowered to reduce leakage or even shutdown.

The STM32MP15x which recommends the use of the STPMIC1 power supply management IC, however the STM32MP25x requires to use the STPMIC2.

The power supply and power supply mode comparisons are given in Table 7 and Table 8.

Table 7. Power supply comparison between STM32MP15x and STM32MP25x lines

| STM32MP                 | 15x lines           | STM32MF               | 25x lines            | Community                                 |  |  |  |  |  |  |  |

|-------------------------|---------------------|-----------------------|----------------------|-------------------------------------------|--|--|--|--|--|--|--|

| Supply Name             | Typical             | Supply Name           | Typical              | - Comments                                |  |  |  |  |  |  |  |

|                         |                     | $V_{DD}$              |                      | -                                         |  |  |  |  |  |  |  |

| V <sub>DD</sub>         |                     | V <sub>DDIO1</sub>    |                      | Optional domain for SD-Card on SDMMC1     |  |  |  |  |  |  |  |

| and                     | 1.8 / 3.3V          | V <sub>DDIO2</sub>    | 1.8 / 3.3V           | Optional domain for eMMC on SDMMC2        |  |  |  |  |  |  |  |

| V <sub>DD_DSI</sub>     |                     | V <sub>DDIO3</sub>    |                      | Optional domain for OCTOSPI port1         |  |  |  |  |  |  |  |

|                         |                     | V <sub>DDIO4</sub>    |                      | Optional domain for OCTOSPI port2         |  |  |  |  |  |  |  |

|                         |                     | V <sub>DDCORE</sub>   | 0.82V <sup>(2)</sup> | Also VDDDSI/LVDS/CSI/COMBOPHY/PCIECLK     |  |  |  |  |  |  |  |

| V <sub>DDCORE</sub>     | 1.2V <sup>(1)</sup> | V <sub>DDCPU</sub>    | 0.8V <sup>(1)</sup>  | For Cortex-A35. New in STM32MP25x lines   |  |  |  |  |  |  |  |

|                         |                     | V <sub>DDGPU</sub>    | 0.8V <sup>(3)</sup>  | For GPU/NPU. New in STM32MP25x lines      |  |  |  |  |  |  |  |

| V <sub>DDQ_DDR</sub>    | -                   | $V_{DDQDDR}$          | -                    | Different ranges to support available DDR |  |  |  |  |  |  |  |

| V <sub>DD_ANA</sub>     | 1.8 / 3.3V          | V <sub>DDA18AON</sub> | 1.8V                 | New in STM32MP25x lines                   |  |  |  |  |  |  |  |

| V <sub>DD_PLL</sub>     | 1.0 / 3.3 V         | V <sub>DDA18PLL</sub> | 1.8V                 | Also VDDA18DDR/USB/DSI/LVDS/CSI/COMBOPHY  |  |  |  |  |  |  |  |

| V <sub>DDA1V1_REG</sub> | 1.1V <sup>(4)</sup> | -                     | -                    | No equivalence (different USB PHY)        |  |  |  |  |  |  |  |

| V <sub>DD1V2_DSI</sub>  | 1.2V <sup>(4)</sup> | -                     | -                    | No equivalence (different DSI PHY)        |  |  |  |  |  |  |  |

| V <sub>DDA1V8_REG</sub> | 1.8V <sup>(4)</sup> | -                     | -                    | No equivalence (different USB PHY)        |  |  |  |  |  |  |  |

| V <sub>DDA1V8_DSI</sub> | 1.8V                | -                     | -                    | No equivalence (different DSI PHY)        |  |  |  |  |  |  |  |

| V                       | 3.3V                | V <sub>DD33USB</sub>  | 3.3V                 |                                           |  |  |  |  |  |  |  |

| V <sub>DD3V3_USB</sub>  | 3.3V                | V <sub>DD33UCPD</sub> | 3.3V                 | -                                         |  |  |  |  |  |  |  |

| V <sub>DDA</sub>        | 1.8 / 3.3V          | V <sub>DDA18ADC</sub> | 1.8V                 | ADC is 1.8V only in STM32MP25x            |  |  |  |  |  |  |  |

| V <sub>BAT</sub>        | 3V                  | V <sub>BAT</sub>      | 3V                   | -                                         |  |  |  |  |  |  |  |

| -                       | -                   | V <sub>08CAP</sub>    | 0.8V <sup>(4)</sup>  | New in STM32MP25x lines                   |  |  |  |  |  |  |  |

- 1. Supports lowering and overdrive

- 2. Supports lowering

- 3. Supports overdrive

- 4. Internal LDO

AN5718 - Rev 1 page 8/30

|           | S1                                | M32MP15x li     | nes             |                        |                               |                                   |         | S1              | M32MP25x I | ines           |                             |                              |                             |

|-----------|-----------------------------------|-----------------|-----------------|------------------------|-------------------------------|-----------------------------------|---------|-----------------|------------|----------------|-----------------------------|------------------------------|-----------------------------|

| Mode      | \ \ \                             | / <sub>DD</sub> | V <sub>DD</sub> | CORE                   | Maria                         | V                                 | DD      | V <sub>DE</sub> | CORE       | V <sub>D</sub> | DCPU                        | V <sub>D</sub>               | DGPU                        |

| Mode      | State                             | Control         | State           | Control                | Mode                          | State                             | Control | State           | Control    | State          | Control                     | State                        | Control                     |

| Run       | ON                                |                 | Overdrive       | HW/SW <sup>(2)</sup>   | Run1                          |                                   |         |                 |            | Overdrive      | HW/SW <sup>(2)</sup>        |                              |                             |

| Rull      | ON                                | -               | ON              | -                      | Rulli                         | ON                                | _       | ON              | _          | ON             | -                           | Overdrive or ON or           | HW/SW <sup>(2)</sup>        |

| -         | -                                 | -               | -               | -                      | Run2 <sup>(1)</sup>           |                                   |         |                 |            | OFF            | PWR_CPU<br>_ON              | OFF                          |                             |

| Stop      | ON                                |                 | ON              |                        | Stop1                         |                                   |         |                 |            | Overdrive      | HW / SW <sup>(2)</sup>      |                              |                             |

| Stop      | ON                                | -               | ON              | _                      | Stop1                         | ON                                | -       | ON              | -          | ON             | -                           | Overdrive<br>or ON or<br>OFF | HW/SW <sup>(2)</sup>        |

| -         | -                                 | -               | -               | -                      | Stop2 <sup>(1)</sup>          |                                   |         |                 |            | OFF            | PWR_CPU<br>_ON              |                              |                             |

| LP-Stop   | ON                                |                 | ON              |                        | LP-Stop1                      |                                   | -       |                 |            | Overdrive      | HW / SW <sup>(2)</sup>      |                              |                             |

| LF-Stop   | ON                                | -               | ON              | _                      | LF-Stop I                     | ON                                |         | ON              | -          | ON             | -                           | Overdrive or ON or           | HW/SW <sup>(2)</sup>        |

| -         | -                                 | -               | -               | -                      | LP-Stop2 <sup>(1)</sup>       |                                   |         |                 |            | OFF            | PWR_CPU<br>_ON              | OFF                          |                             |

| LPLV-Stop | ON                                | -               | Lowered         | PWR_ON<br>or<br>PWR_LP | LPLV-<br>Stop1                | ON                                | _       | Lowered         | PWR_ON or  | Lowered        | PWR_CPU<br>_ON or<br>PWR_LP | OFF or                       | PWR_CPU<br>_ON or<br>PWR_LP |

| -         | -                                 | -               | -               | -                      | LPLV-<br>Stop2 <sup>(1)</sup> |                                   |         |                 | PWR_LP     | OFF            | PWR_CPU<br>_ON              | Lowered                      | or HW/<br>SW <sup>(2)</sup> |

| Standby   | ON                                |                 | OFF             | PWR_ON                 | Standby1                      | ON                                | _       | OFF             | PWR_ON     | OFF            | PWR_CPU                     | OFF                          | PWR_CPU                     |

| Standby   | ON                                | -               | OFF             | F VVIX_OIN             | Standby2                      | OIN                               | _       | OFF             | F WR_ON    | OFF            | _ON                         | OFF                          | _ON                         |

| Voat      | OFF using LIM or SW(2)            |                 |                 | V <sub>BAT1</sub>      | OFF using HW or SW(2)         |                                   |         |                 |            |                |                             |                              |                             |

| , R∀I     | OFF using HW or SW <sup>(2)</sup> |                 |                 |                        | V <sub>BAT2</sub>             | OFF using HW or SW <sup>(2)</sup> |         |                 |            |                |                             |                              |                             |

- 1. STM32MP25x modes supported with STPMIC2 (new modes not available on STM32MP15x lines)

- 2. For example. GPIO or I<sup>2</sup>C command to STPMIC

The same power concept used on the STM32MP15x devices can be reused on STM32MP25x by having same control for  $V_{DDCPU}$ ,  $V_{DDCORE}$ , and  $V_{DDGPU}$  regulator modules, only use PWR\_ON (and PWR\_LP), with potential overdrive handled by GPIO or direct I<sup>2</sup>C commands to STPMIC2. With this simplified use, PWR\_CPU\_ON is not used, behavior versus low-power modes is similar to the STM32MP15x. In that case, the STM32MP25x power optimized modes such as Run2, Stop2, LP-Stop2 and LPLV-Stop2 are not available.

## 5 Boot modes selection

The STM32MP15x and STM32MP25x devices always start from internal BootROM. Internal BootROM starts based on boot pins and on internal OTP fuses.

- Boot from external Flash with default OTPs:

- SD-Card (SDMMC1)

- e•MMC (SDMMC2)

- SLC-NAND (FMC)

- Serial NOR-Flash or Serial NAND-Flash. Refer to Table 9

Table 9. Processor serial flash boot interface connection

| STM32MP15x lines | STM32MP25x lines |

|------------------|------------------|

| QUADSPI          | OCTOSPI          |

- Boot from UART or USB (device)

- Used to access the device from STM32CubeProgrammer (STM32CubeProg) for example program

the external Flash or internal OTP fuses. Refer to Table 10

Table 10. Processor USB boot interface connection

| STM32MP15x lines                  | STM32MP25x lines            |

|-----------------------------------|-----------------------------|

| USB OTG on High-Speed PHY port #2 | USB3DR on High-Speed PHY #2 |

Note:

Default pins for Boot interface are different between STM32MP15x lines and STM32MP25x lines. Refer to product datasheet and Application Note "Getting started with STM32MP25x lines hardware development."

Refer to following STM32 wiki articles:

- https://wiki.st.com/stm32mpu/index.php/Boot\_chains\_overview

- https://wiki.st.com/stm32mpu/index.php/STM32MP15 ROM code overview

- https://wiki.st.com/stm32mpu/index.php/STM32MP25\_ROM\_code\_overview

AN5718 - Rev 1 page 10/30

# page 11/3

## 6 Peripherals migration

1

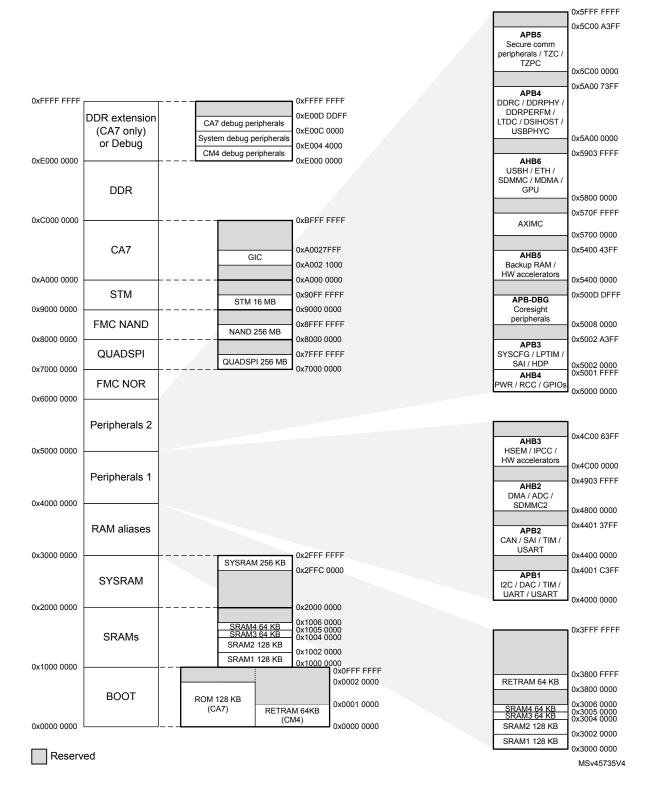

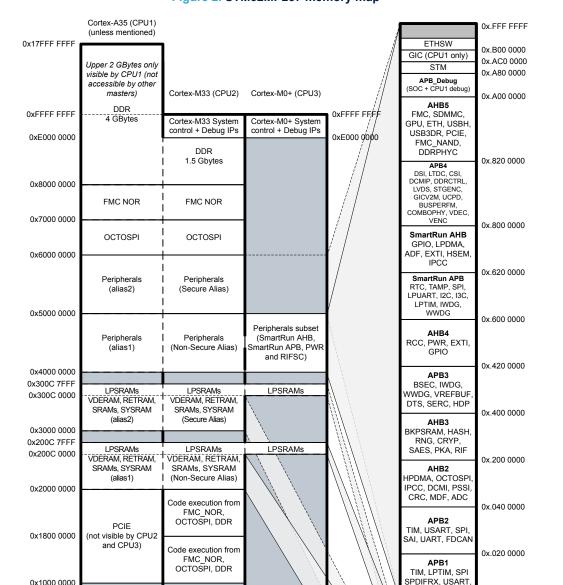

This section presents a full view of the features and peripheral counts of STM32MP15x and STM32MP25x lines, an analysis of peripheral cross compatibility between STM32MP15x and STM32MP25x lines and a peripheral address mapping snapshot for the concerned products.

Table 11. STM32MP15xxx features and peripheral counts Vs STM32MP25xxx

|                 | S             | TM32M         | IP157 li      | ne            | S                  | TM32N         | IP153 li      | ine           | S             | TM32M         | IP151 li      | ne            | STM           | 32MP2         | 7 line        | STM           | 32MP2         | 55 line       | STM           | 32MP2         | 3 line        | STM           | 32MP25        | 1 line        |

|-----------------|---------------|---------------|---------------|---------------|--------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Products        | STM32MP157xAD | STM32MP157xAB | STM32MP157xAC | STM32MP157xAA | STM32STM32MP153XAD | STM32MP153XAB | STM32MP153XAC | STM32MP153XAA | STM32MP151XAD | STM32MP151XAB | STM32MP151XAC | STM32MP151XAA | STM32MP257xAL | STM32MP257xAK | STM32MP257xAI | STM32MP255xAL | STM32MP255xAK | STM32MP255xAI | STM32MP253xAL | STM32MP253xAK | STM32MP253xAI | STM32MP251xAL | STM32MP251xAK | STM32MP251xAI |

| Package         | TFBGA257      | LFBGA354      | TFBGA361      | LFBGA448      | TFBGA257           | LFBGA354      | TFBGA361      | LFBGA448      | LFBGA448      | LFBGA354      | TFBGA361      | LFBGA448      | VFBGA361      | VFBGA424      | VFBGA436      |

| Size (mm)       | 10x10         | 16x16         | 12X12         | 18X18         | 10x10              | 16x16         | 12X12         | 18X18         | 10x10         | 16x16         | 12X12         | 18X18         | 10X10         | 14X14         | 18X18         |

| Ball pitch (mm) | 0.5           | 0.8           | 0.5           | 0.8           | 0.5                | 0.8           | 0.5           | 0.8           | 0.5           | 0.8           | 0.5           | 0.8           | 0.5           | 0.5           | 0.8           | 0.5           | 0.5           | 0.8           | 0.5           | 0.5           | 0.8           | 0.5           | 0.5           | 0.8           |

| GPIOs           | 98            | 98            | 148           | 176           | 98                 | 98            | 148           | 176           | 98            | 98            | 148           | 176           | 144           | 144           | 172           | 144           | 144           | 172           | 144           | 144           | 172           | 144           | 144           | 172           |

| CPU core        |               |               |               | С             | ortex-A            | 47 FPU        | Neon 1        | TrustZc       | ne            |               |               |               |               |               |               | Co            | rtex-A        | 35 FPU        | Neon          | TrustZ        | one           |               |               |               |

| Multicore       |               |               |               | Dua           | l-core             |               |               |               |               | Singl         | e-core        |               |               |               |               | [             | Dual-co       | re            |               |               |               | Single        | -core         |               |

|                 |               |               |               | 32-l          | Kbyte L            | 1 data        | cache f       | or each       | core          |               |               |               |               |               |               | 32-ł          | Kbyte L       | 1 data d      | cache fo      | or each       | core          |               |               |               |

| Cache sizes     |               |               |               | 32-Kby        | /te L1 ir          | nstructio     | on cach       | e for ea      | ach core      | е             |               |               |               |               |               | 32-Kby        | rte L1 ir     | nstructio     | on cach       | e for ea      | ach core      | )             |               |               |

|                 |               |               |               | 256-k         | Kbyte le           | evel 2 u      | nified co     | oherent       | cache         |               |               |               |               |               |               | 512-k         | (byte le      | vel 2 ur      | nified co     | oherent       | cache         |               |               |               |

| Frequency       |               |               |               |               |                    | up to 6       | 50 MH         | z             |               |               |               |               |               |               |               |               |               | up to 12      | 200 MH        | z             |               |               |               |               |

| Overdrive mode  |               |               |               |               | ı                  | up to 80      | 00 MHz        | (1)           |               |               |               |               |               |               |               |               | u             | p to 150      | 00 MHz        | (2)           |               |               |               |               |

|                     | Sī            | ГМ32М         | P157 li                                                          | ne                     | Sī                 | ГМ32М               | P153 li       | ne                     | S1            | M32M          | P151 liı            | ne                           | STM3                                                                | 2MP25         | 7 line        | STM3          | 2MP25         | 5 line        | STM32MP253 line     |               |                      | STM32MP253xAK STM32MP253xAI STM32MP251xAL - stZone che |               |               |  |  |  | STM32MP251 line |  |

|---------------------|---------------|---------------|------------------------------------------------------------------|------------------------|--------------------|---------------------|---------------|------------------------|---------------|---------------|---------------------|------------------------------|---------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------------|---------------|----------------------|--------------------------------------------------------|---------------|---------------|--|--|--|-----------------|--|

| Products            | STM32MP157xAD | STM32MP157xAB | STM32MP157xAC                                                    | STM32MP157xAA          | STM32STM32MP153XAD | STM32MP153XAB       | STM32MP153XAC | STM32MP153XAA          | STM32MP151XAD | STM32MP151XAB | STM32MP151XAC       | STM32MP151XAA                | STM32MP257xAL                                                       | STM32MP257xAK | STM32MP257xAI | STM32MP255xAL | STM32MP255xAK | STM32MP255xAI | STM32MP253xAL       | STM32MP253xAK | STM32MP253xAI        | STM32MP251xAL                                          | STM32MP251xAK | STM32MP251xAI |  |  |  |                 |  |

| GPU for 3D graphics |               |               | Vivante - Open GL ES 2.0 Vivante - Open GL ES 3.2.8 - Vulkan 1.2 |                        |                    |                     |               |                        |               |               |                     |                              |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| Frequency           | up to 533 MHz |               |                                                                  |                        |                    |                     |               |                        |               |               |                     | up to 800 MHz                |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| Overdrive mode      | -             |               |                                                                  |                        |                    |                     |               |                        |               |               |                     | up to 900 MHz <sup>(2)</sup> |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| MCU core            | Cortex-M4 FPU |               |                                                                  |                        |                    |                     |               |                        |               |               |                     | Cortex-M33 FPU TrustZone     |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| Cache size          | -             |               |                                                                  |                        |                    |                     |               |                        |               |               |                     |                              |                                                                     |               |               |               |               |               | Data ca<br>truction |               |                      |                                                        |               |               |  |  |  |                 |  |

| Frequency           |               |               |                                                                  |                        |                    | up to 20            | 09 MHz        | <u>:</u>               |               |               |                     |                              |                                                                     |               |               |               |               |               | 00 MHz              |               |                      |                                                        |               |               |  |  |  |                 |  |

| Embedded S          | RAM           |               |                                                                  |                        |                    |                     |               |                        |               |               |                     |                              |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| CPU<br>System       |               |               |                                                                  |                        |                    | 256 K               | bytes         |                        |               |               |                     |                              | 256 Kbytes (+128 Kbytes if video RAM is not used) 384 Kbytes        |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| Video RAM           |               |               |                                                                  |                        |                    |                     |               |                        |               |               |                     |                              | 128 Kbytes (free for CPU system if video accelerators are not used) |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| MCU<br>subsystem    |               |               |                                                                  |                        |                    | 384 K               | bytes         |                        |               |               |                     |                              |                                                                     |               | 2             | 256 Kby       | tes (128      | 8Kbytes       | are tar             | mper pr       | otected              | l)                                                     |               |               |  |  |  |                 |  |

| MCU retention       |               |               |                                                                  |                        |                    | 64 KI               | bytes         |                        |               |               |                     |                              |                                                                     |               |               |               |               | 128 K         | bytes               |               |                      |                                                        |               |               |  |  |  |                 |  |

| Backup              |               |               |                                                                  |                        | 4 Kbyte            | es (tam             | per pro       | tected)                |               |               |                     |                              |                                                                     |               |               |               | 8 Kbyte       | es (tam       | per prot            | tected)       |                      |                                                        |               |               |  |  |  |                 |  |

| SDRAM               |               |               |                                                                  |                        |                    |                     |               |                        |               |               |                     |                              |                                                                     |               |               |               |               |               |                     |               |                      |                                                        |               |               |  |  |  |                 |  |

| LPDDR 16-<br>bits   |               |               |                                                                  |                        | Up to              | 1 Gbyte             | e, singl      | e rank                 |               |               |                     |                              |                                                                     |               |               |               | Up to         | 4 Gbyt        | es, dua             | l rank        |                      |                                                        |               |               |  |  |  |                 |  |

| LPDDR 32-<br>bits   |               |               | Gb                                                               | to 1<br>yte,<br>e rank | -                  |                     | Gb            | to 1<br>yte,<br>e rank |               |               | Up<br>Gby<br>single |                              | , - Gbytes, - Gbytes, - Gbytes, -                                   |               |               |               |               |               |                     | -             | Up t<br>Gby<br>locks | tes,                                                   |               |               |  |  |  |                 |  |

| LPDDR freq.         |               |               |                                                                  |                        | LPDD               | R2/3 u <sub>l</sub> | p to 530      | 3 MHz                  |               |               |                     |                              |                                                                     |               |               |               | LPDD          | R4 up         | to 1200             | MHz           |                      |                                                        |               |               |  |  |  |                 |  |

Peripherals migration

| 3  |

|----|

| 71 |

|                                   | S1                                                                                  | ГМ32М                                               | P157 li       | ne            | STM32MP153 line    |               |               |               | S                   | ТМ32М         | P151 li       | ne            | STM32MP257 line STM32MP255 line STM32MP253 line STM32MP251 line |               |                       |               |               |                     |               |               | e STM32MP257 line STM32MP255 line |               |               |               | P255 line STM32MP253 line STI |  |  |  | M32MP251 line |  |

|-----------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|---------------|--------------------|---------------|---------------|---------------|---------------------|---------------|---------------|---------------|-----------------------------------------------------------------|---------------|-----------------------|---------------|---------------|---------------------|---------------|---------------|-----------------------------------|---------------|---------------|---------------|-------------------------------|--|--|--|---------------|--|

| Products                          | STM32MP157xAD                                                                       | STM32MP157xAB                                       | STM32MP157xAC | STM32MP157xAA | STM32STM32MP153XAD | STM32MP153XAB | STM32MP153XAC | STM32MP153XAA | STM32MP151XAD       | STM32MP151XAB | STM32MP151XAC | STM32MP151XAA | STM32MP257xAL                                                   | STM32MP257xAK | STM32MP257xAI         | STM32MP255xAL | STM32MP255xAK | STM32MP255xAI       | STM32MP253xAL | STM32MP253xAK | STM32MP253xAI                     | STM32MP251xAL | STM32MP251xAK | STM32MP251xAI |                               |  |  |  |               |  |

| DDR 16-bits                       | up to 1 Gbyte, single rank                                                          |                                                     |               |               |                    |               |               |               |                     | ι             | Jp to 2       | Gbytes        | dual ra                                                         | nk for [      | DDR3L,                | Up to 4       | 4 Gbyte       | s single            | rank fo       | or DDR        | 4                                 |               |               |               |                               |  |  |  |               |  |

| DDR 32-bits                       | Up to 1 Up to 1 Up to 1 Up to 1 Gbyte, - Gbyte, single rank single rank single rank |                                                     |               |               |                    |               | yte,          | -             | Up<br>Gby<br>single |               | -             | Gb            | to 1<br>yte,<br>e rank                                          | -             | Up :<br>Gby<br>single | yte,          | -             | Up<br>Gby<br>single | yte,          |               |                                   |               |               |               |                               |  |  |  |               |  |

| DDR freq.                         |                                                                                     |                                                     |               |               | DDR                | 3/3L up       | to 533        | MHz           |                     |               |               |               |                                                                 |               | DI                    | DR3L u        | p to 10       | 66 MHz              | . DDR4        | up to 1       | 200 MI                            | Ηz            |               |               |                               |  |  |  |               |  |

| On-the-fly<br>encrypt/<br>decrypt |                                                                                     |                                                     |               |               |                    |               |               |               |                     |               |               |               | Yes <sup>(3)</sup>                                              |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| Backup<br>registers               |                                                                                     |                                                     |               | 128 b         | ytes (3            | 2x32-bi       | t, tamp       | er prote      | ected)              |               |               |               |                                                                 |               |                       | 512 B         | ytes (12      | 8x32-b              | its, tam      | per prof      | tected)                           |               |               |               |                               |  |  |  |               |  |

| Timers                            |                                                                                     |                                                     |               |               |                    |               |               |               |                     |               |               |               |                                                                 |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| General<br>purpose 16<br>bits     |                                                                                     |                                                     |               |               | 8 x 1              | 6-bits        | + 2 x 32      | 2-bits        |                     |               |               |               |                                                                 |               |                       |               | 8 x ′         | 16-bits             | + 4 x 32      | 2-bits        |                                   |               |               |               |                               |  |  |  |               |  |

| Advanced control                  |                                                                                     |                                                     |               |               |                    | 2             | 2             |               |                     |               |               |               | 3                                                               |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| Basic                             |                                                                                     |                                                     |               |               |                    | 2             | 2             |               |                     |               |               |               | 2                                                               |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| Low power                         |                                                                                     |                                                     |               |               |                    | 2             | 2             |               |                     |               |               |               | 5                                                               |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| Watchdog                          |                                                                                     |                                                     | 3             | (indep        | endent,            | indepe        | endent        | secure,       | windov              | v)            |               |               |                                                                 |               |                       | 7             | (5 x Inc      | depend              | ent, 2 x      | Windov        | v)                                |               |               |               |                               |  |  |  |               |  |

| Communicat                        | tion int                                                                            | erfaces                                             | S             |               |                    |               |               |               |                     |               |               |               |                                                                 |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| SPI / I <sup>2</sup> S            | 6 / 3 (full-duplex)                                                                 |                                                     |               |               |                    |               |               |               |                     |               |               |               | 8                                                               | 3 / 3 (ful    | l-duple:              | x)            |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| I <sup>2</sup> C                  | 6                                                                                   |                                                     |               |               |                    |               |               |               |                     |               |               |               |                                                                 |               | 8                     |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| USART and<br>UART                 | d 4 + 4                                                                             |                                                     |               |               |                    |               |               |               |                     |               |               |               |                                                                 |               | 4                     | + 5           |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| SAI                               | 4                                                                                   |                                                     |               |               |                    |               |               |               | 4                   |               |               |               |                                                                 |               |                       |               |               |                     |               |               |                                   |               |               |               |                               |  |  |  |               |  |

| USB host                          |                                                                                     | USB 2.0 host (USBH), 2 ports, embedded hi-speed PHY |               |               |                    |               |               |               |                     |               |               |               |                                                                 | USB :         | 2.0 hos               | t (USBF       | H), 1 po      | rt, emb             | edded h       | ni-speed      | PHY                               |               |               |               |                               |  |  |  |               |  |

|                                         | S                                                    | TM32M         | P157 li       | ne            | S                  | TM32M         | P153 li       | ne            | STM32MP151 line   STM32MP257 line   STM32MP255 line   STM32MP253 line   STM32M |                                                                                         |                |                   |                                    |               |               |               | TM32MP251 line |               |                  |               |               |               |               |               |

|-----------------------------------------|------------------------------------------------------|---------------|---------------|---------------|--------------------|---------------|---------------|---------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------|-------------------|------------------------------------|---------------|---------------|---------------|----------------|---------------|------------------|---------------|---------------|---------------|---------------|---------------|

| Products                                | STM32MP157xAD                                        | STM32MP157xAB | STM32MP157xAC | STM32MP157xAA | STM32STM32MP153XAD | STM32MP153XAB | STM32MP153XAC | STM32MP153XAA | STM32MP151XAD                                                                  | STM32MP151XAB                                                                           | STM32MP151XAC  | STM32MP151XAA     | STM32MP257xAL                      | STM32MP257xAK | STM32MP257xAI | STM32MP255xAL | STM32MP255xAK  | STM32MP255xAI | STM32MP253xAL    | STM32MP253xAK | STM32MP253xAI | STM32MP251xAL | STM32MP251xAK | STM32MP251xAI |

| USB OTG                                 | USB                                                  | 2.0 Ho        | st/Devid      | ce (OTC       | 3), 1 po           |               | edded<br>t 2) | Hi-Spe        | ed PHY                                                                         | ed PHY (shared with USBH USB 2.0/3.0 dual role (USB3DR), embedded hi-speed and S<br>PHY |                |                   |                                    |               |               |               |                | and Su        | perSpeed 5 Gbps  |               |               |               |               |               |

| SPDIFRX                                 |                                                      | 4 inputs      |               |               |                    |               |               |               |                                                                                | 4 inputs                                                                                |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| FDCAN                                   | 2 (FDCAN)                                            |               |               |               |                    |               |               | -             |                                                                                | 3 (1 x TT-FDCAN), 10 Kbytes shared buffer                                               |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| HDMI-CEC                                | 1                                                    |               |               |               |                    |               |               |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| SDMMC<br>(SD, SDIO,<br>e•MMC)           | 3 (8 + 8 + 4 bits)                                   |               |               |               |                    |               |               |               |                                                                                | 3 (8 + 8 + 4 bits)                                                                      |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| Serial-flash                            |                                                      |               |               |               |                    |               |               |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| Interface                               |                                                      |               |               |               |                    | 2 x QL        | IADSPI        |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                | 2 x OC        | TOSPI            |               |               |               |               |               |

| On-the-fly decryption                   |                                                      |               |               |               |                    |               | -             |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                | Ye            | s <sup>(3)</sup> |               |               |               |               |               |

| FMC memor                               | y contr                                              | oller         |               |               |                    |               |               |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

| PSRAM                                   |                                                      |               |               |               | 4 × CS             | S, up to      | 4 × 64        | Mbytes        |                                                                                |                                                                                         |                |                   | 4 x CS, up to 4 x 64 MBytes        |               |               |               |                |               |                  |               |               |               |               |               |

| NAND                                    |                                                      |               |               |               | 1 ×                | CS, SL        | .C, BC        | 14/8          |                                                                                |                                                                                         |                |                   | 4 x CS, SLC, BCH4/8                |               |               |               |                |               |                  |               |               |               |               |               |

| Other interfa                           | aces                                                 |               |               |               |                    |               |               |               |                                                                                |                                                                                         |                |                   |                                    |               |               |               |                |               |                  |               |               |               |               |               |

|                                         | 1 00                                                 | ort MII       | RMII, C       | ZMII D        | CMII (C            | ZMII D        | ⊇MII on       | ılv on T      | EBCV3                                                                          | 61 and                                                                                  | I EBC/         | 1112              | 3 p                                | orts, R       | G)MII,        | MII           | 2 p            | orts, R       | (G)MII,          | MII           | 1 p           | oort, R(      | G)MII, I      | MII           |

| Ethernet                                | 1 pc                                                 | JIL, IVIII,   | Kiviii, C     | JIVIII, IX    | Givili (C          |               | ages)         | ily OII I     | I BGAS                                                                         | o i anu                                                                                 | LIBGA          | \ <del>44</del> 0 | TSN Switch with two external ports |               |               |               |                |               |                  |               |               |               |               |               |

| LCD-TFT parallel interface              | Up to 24-bit data (up to 1366×768 60 fps)            |               |               |               |                    |               |               |               |                                                                                | up                                                                                      | to 24-b        | its 150           | MHz pi                             | xel cloc      | ck (up to     | 1080p         | 60)            |               |                  |               |               |               |               |               |

| Display<br>Serial<br>Interface<br>(DSI) | 2 × data lanes 1 GHz each<br>(up to 1366×768 60 fps) |               |               |               |                    |               |               | -             |                                                                                | 4 x                                                                                     | data la        |                   | Gbps (                             | each (u       | p to          |               |                |               | -                |               |               |               |               |               |

| LVDS<br>display                         | -                                                    |               |               |               |                    |               |               |               |                                                                                | Dual-l                                                                                  | ink of 4<br>(u |                   | lanes 1<br>36p60)                  |               | s each        |               |                |               |                  |               |               |               |               |               |

|                                          | STM32MP157 line STM32MP153 line STM32M |               |               |               |                    |               |               | P151 li              | ne                                            | STM32MP257 line STM32MP255 line STM32MP253 line |               |               |                                                         |               | 3 line        | ne STM32MP251 line |               |               |               |               |               |               |               |               |

|------------------------------------------|----------------------------------------|---------------|---------------|---------------|--------------------|---------------|---------------|----------------------|-----------------------------------------------|-------------------------------------------------|---------------|---------------|---------------------------------------------------------|---------------|---------------|--------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Products                                 | STM32MP157xAD                          | STM32MP157xAB | STM32MP157xAC | STM32MP157xAA | STM32STM32MP153XAD | STM32MP153XAB | STM32MP153XAC | STM32MP153XAA        | STM32MP151XAD                                 | STM32MP151XAB                                   | STM32MP151XAC | STM32MP151XAA | STM32MP257xAL                                           | STM32MP257xAK | STM32MP257xAI | STM32MP255xAL      | STM32MP255xAK | STM32MP255xAI | STM32MP253xAL | STM32MP253xAK | STM32MP253xAI | STM32MP251xAL | STM32MP251xAK | STM32MP251xAI |

| DMA                                      |                                        |               |               | 3 insta       | ances,             | 48 phys       | ical cha      | annels i             | n total                                       |                                                 |               |               | 3 instances, 48 physical channels in total              |               |               |                    |               |               |               |               |               |               |               |               |

| Cryptograph<br>y                         | h DES/TDES, AES-256 <sup>(5)</sup>     |               |               |               |                    |               |               |                      | DES/TDES, AES-256 <sup>(3)</sup>              |                                                 |               |               |                                                         |               |               |                    |               |               |               |               |               |               |               |               |

| Hash                                     | SHA-256, MD5, HMAC                     |               |               |               |                    |               |               |                      | SHA-1, SHA-2 and SHA-3 (up to 512), MD5, HMAC |                                                 |               |               |                                                         |               |               |                    |               |               |               |               |               |               |               |               |

| True random number generator             | Yes                                    |               |               |               |                    |               |               |                      |                                               | Yes                                             |               |               |                                                         |               |               |                    |               |               |               |               |               |               |               |               |

| Fuses (one-<br>time<br>programma<br>ble) |                                        |               |               |               | 30                 | 072 effe      | ctive bi      | ts                   |                                               |                                                 |               |               |                                                         |               |               |                    | 12            | 288 eff       | ective b      | its           |               |               |               |               |

| Camera inte                              | rface                                  |               |               |               |                    |               |               |                      |                                               |                                                 |               |               |                                                         |               |               |                    |               |               |               |               |               |               |               |               |

| Parallel                                 |                                        |               |               |               | Up to              | 14-bit,       | up to 80      | ) MHz                |                                               |                                                 |               |               | Up to 16-bits, up to 120 MHz. Path shared with CSI      |               |               |                    |               |               |               |               |               |               |               |               |

| CSI-2                                    |                                        |               |               |               |                    | -             |               |                      |                                               |                                                 |               |               | 2 x 4 data lanes 2.5 Gbps each. Path shared with DCMIPP |               |               |                    |               |               |               |               |               |               |               |               |

| ISP                                      |                                        |               |               |               |                    | -             |               |                      |                                               |                                                 |               |               | Yes, basic ISP                                          |               |               |                    |               |               |               |               |               |               |               |               |

| Analog inter                             | faces                                  |               |               |               |                    |               |               |                      |                                               |                                                 |               |               |                                                         |               |               |                    |               |               |               |               |               |               |               |               |