Application note

# Migrating from STM8L and STM8S to STM32C0 MCUs

## Introduction

This application note provides guidelines and a methodology to migrate easily from an application based on the STM8L and STM8S series to the STM32C0 series platform. It groups all of the most important information, and lists the main aspects that must be addressed. It describes a simple procedure using the HAL (hardware abstraction layer), and STM32Cube software, to access a larger portfolio.

The STM32C0 platform is a starting point for simple cost-focused applications. It offers easy further migration within a wide range of STM32 products, depending on the application needs (focused on costs, tailored to ultra low-power consumption, high performance, or for products embedding wireless communication).

This document provides details about the hardware, peripheral, and firmware migration.

In addition, this document gives an overview of the STM32 ecosystem, for example the hardware development and IDE/ compiler available to start using the STM32C0 series.

For a better understanding, the user must be familiar with STM32 microcontrollers.

For additional information, refer to the documents in Reference documents. This does not provide a full list of electrical parameters, for which the device datasheet is the reference document.

# **1** General information

Note:

This document applies to all STM32C0 series devices. All these products are Arm<sup>®</sup>-based microcontrollers. *Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.*

arm

#### **Reference documents**

| [1]            | Application note EMC design guide for STM8, STM32, and legacy MCUs (AN1709)                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| [2]            | Application note STM32 microcontroller system memory boot mode (AN2606)                                                                 |

| [3]            | Application note How to use EEPROM emulation on STM32 MCUs (AN4894)                                                                     |

| [4]            | Application note STM32 microcontroller GPIO hardware settings and low-power consumption (AN4899)                                        |

| [5]            | Application note Introduction to FDCAN peripherals for STM32 product classes (AN5348)                                                   |

| [6]            | Application note Getting started with STM32C0 series hardware development (AN5673)                                                      |

| [7]            | Reference manual STM8L001xx and STM8L101xx microcontroller families (RM0013)                                                            |

| [8]            | Reference manual STM8S series and STM8AF series 8-bit microcontrollers (RM0016)                                                         |

| [9]            | Reference manual STM8L050J3, STM8L051F3, STM8L052C6, STM8L052R8 MCUs and STM8L151/<br>L152, STM8L162, STM8AL31, STM8AL3L lines (RM0031) |

| [10]           | Reference manual STM32C0x1 advanced Arm®-based 32-bit MCUs (RM0490)                                                                     |

| [11]           | Programming manual <i>How to program STM8S and STM8A flash program memory and data EEPROM</i> (PM0051)                                  |

| [12]           | Programming manual STM32 Cortex <sup>®</sup> -M0+ MCUs programming manual (PM0223)                                                      |

| STM32C0 series | All STM32C0 datasheets                                                                                                                  |

|                | All STM32C0 errata sheets                                                                                                               |

| STM8L/S series | All STM8S and STM8L datasheets                                                                                                          |

|                | All STM8S and STM8L errata sheets                                                                                                       |

| STM32CubeProg  | https://www.st.com/stm32cubeprog                                                                                                        |

|                |                                                                                                                                         |

Note:

All documents are available at www.st.com. Contact STMicroelectronics when more information is needed.

# 2 STM32C0 series overview

The STM32C0 series includes all the STM8L/S series standard peripherals such as SPI and UART. (See Table 4 for more details.) It also has a set of peripherals with advanced features and optimized power consumption levels, including:

- 32-bit CPU with maximum CPU frequency of 48 MHz

- DMA

- 12-bit ADC

- I<sup>2</sup>S

- USB FS

- FDCAN

# **3** Hardware migration

## 3.1 Pinout compatibility

STM32C0 devices use a different system of power distribution (single-supply pair), with the merging of  $V_{DDA}$  and  $V_{DD}$  and the absence of VCAP, embedding the capacitance required internally by the regulator. The STM32C0 provides better GPIO density than the STM8L/S series. It needs a 3.3 V supply voltage (compared to the STM8S 5 V supply voltage), with an allowed range of 2 V to 3.6 V.

Due to the significant difference between the STM8L/S series and the STM32C0 series, there is no pin-to-pin compatibility. In the case of a replacement, the PCB routing must be reworked.

| Package pin count | GPIO number in<br>STM32C0 series | GPIO number in<br>STM8S series | GPIO number in<br>STM8L series | Difference I/Os |

|-------------------|----------------------------------|--------------------------------|--------------------------------|-----------------|

| 8                 | 6                                | 5                              | 6                              | 0 to +1         |

| 20                | 18                               | 16                             | 18                             | 0 to +2         |

| 32                | 30                               | 25 to 28                       | 28 to 30                       | 0 to +5         |

| 48                | 45                               | 38                             | 41                             | +4 to +7        |

| 64                | 61                               | 52                             | 54                             | +7 to +9        |

## Table 1. Additional I/Os for STM32C0 vs STM8

#### Table 2. Package type

| Package pins | STM32C0 series | STM8S series     | STM8L series    |

|--------------|----------------|------------------|-----------------|

| 8            | SO8N           | SO8N             | SO8N            |

| 20           | TSSOP/UFQFPN   | TSSOP/UFQFPN/SO  | TSSOP/UFQFPN    |

| 28           | UFQFPN         | -                | UFQPN/CSP       |

| 32           | UFQFPN/LQFP    | UFQFPN/LQFP/SDIP | LQFP/UFQFPN/CSP |

| 44           | -              | LQFP             | -               |

| 48           | UFQFPN/LQFP    | LQFP             | UFQFPN/LQFP     |

| 64           | LQFP/BGA       | LQFP             | LQFP            |

| 80           | (1)            | LQFP             | LQFP            |

1. The STM32G0 series supports this package.

Note:

WLCSP12, WLCSP15, WLCSP19, and WLCSP24 are available on the STM32C0 series

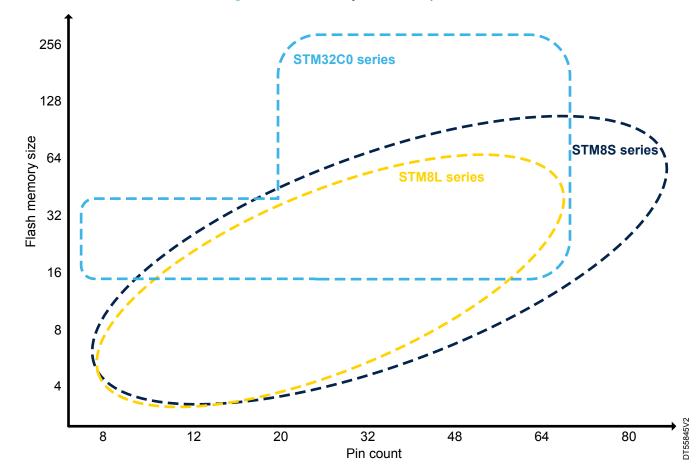

#### Figure 1. Flash memory size versus pin count

## 3.2 Sales type selection

57

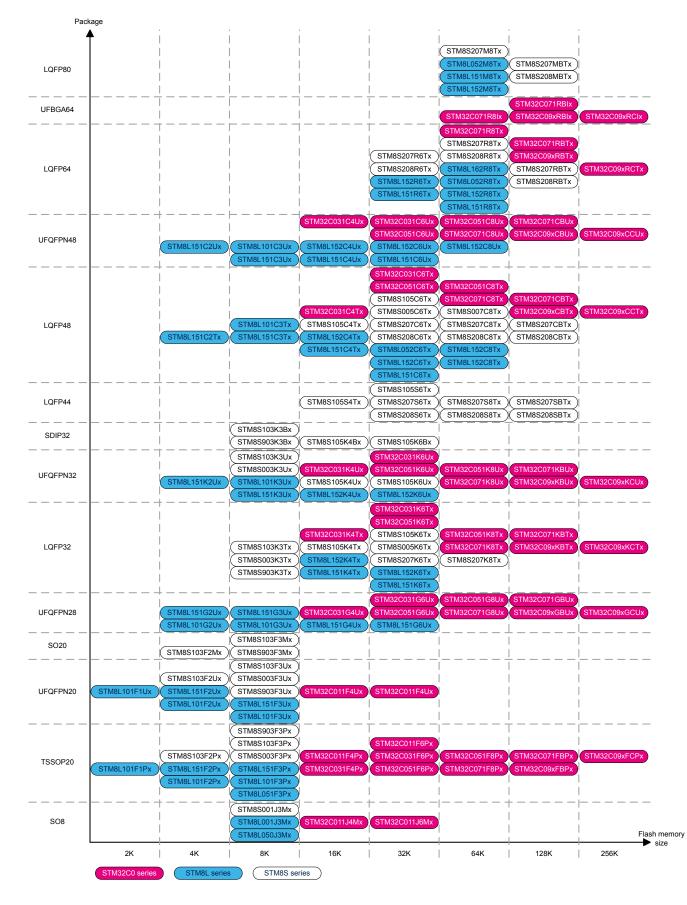

Figure 2 helps the user to find the suitable sales type to migrate from the STM8L/S series to the STM32C0 series, with a flash memory size and package comparison.

WLCSP packages are available on STM32C0 series and STM8L/S series, but as they are unique to each product they are not present in Figure 2.

If the STM32C0 series does not support the desired package or flash memory, the user can check the part available on the STM32G0, STM32L0, and STM32L4 series.

#### Figure 2. Sales type help selection

DT55846V3

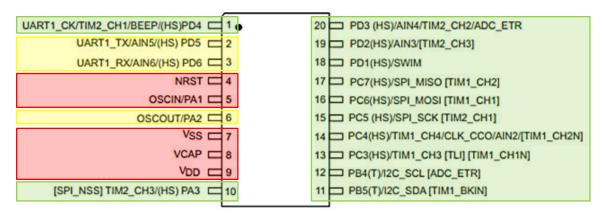

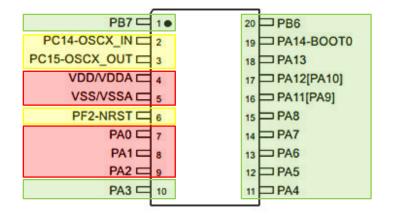

## 3.3 Pinout migration

A comparison between two packages is available to help the customer to evaluate how much the PCB needs to be reworked. The comparison considers only the different position of power pins, reset, and oscillator input/ output. The product datasheets give more details in case the user would like to check timer, communication peripherals, or even ADC channel similarities.

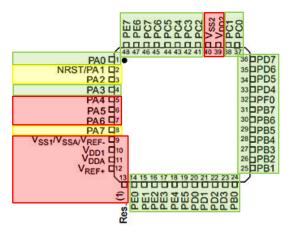

#### Figure 3. TSSOP20 GPIO comparison

STM8S003F3 TSSOP20 PINOUT

STM32C011FxP TSSOP20 PINOUT

Possible to re-route Similar role

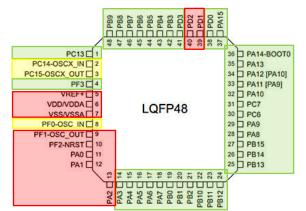

#### Figure 4. LQFP48 GPIO comparison

STM8L151C4, STM8L151C6 LQFP48 PINOUT (WITHOUT LCD)

STM32C031CxT LQFP48 PINOUT

AN5775 - Rev 4

# 4 Boot mode selection

The boot configuration of the STM32C0 is based on the STM32 Cortex<sup>®</sup>-M0+ core products.

In the STM8L/S series, the software can boot only from the flash memory or the system bootloader. The STM32C0 series allows the BOOT vector to be located in the flash memory, the system memory (bootloader), or the RAM based on Table 3. It relocates the boot memory start address if, for example, the user chooses to boot from the main flash memory. This memory area is aliased in the boot memory space (0x0000 0000), but is still accessible from its original memory space (0x0800 0000). It is reciprocal to the other boot area.

A feature to check if the device is virgin is implemented on the STM32C0 series. If the BOOT0 pin defines the main flash memory as the target boot area, and after loading the option byte, the flash memory interface checks if the first location of the main memory is programmed. It returns the result on the FLASH\_ACR register.

|               | Boot mode configuration |           |                                    |   |                             |  |  |  |  |  |

|---------------|-------------------------|-----------|------------------------------------|---|-----------------------------|--|--|--|--|--|

| BOOT_LOCK bit | nBOOT1 bit              | BOOT0 pin | BOOT0 pin nBOOT_SEL bit nBOOT0 bit |   |                             |  |  |  |  |  |

| 0             | Х                       | 0         | 0                                  | Х | Main flash memory           |  |  |  |  |  |

| 0             | 1                       | 1         | 0                                  | Х | System memory               |  |  |  |  |  |

| 0             | 0                       | 1         | 0                                  | Х | Embedded SRAM               |  |  |  |  |  |

| 0             | Х                       | Х         | 1                                  | 1 | Main flash memory           |  |  |  |  |  |

| 0             | 1                       | Х         | 1                                  | 0 | System memory               |  |  |  |  |  |

| 0             | 0                       | Х         | 1                                  | 0 | Embedded SRAM               |  |  |  |  |  |

| 1             | Х                       | х         | x                                  | х | Main flash memory<br>forced |  |  |  |  |  |

#### Table 3. Boot mode configuration

# 5 Peripheral migration

## 5.1 STM32 product cross-compatibility

The peripheral platform shares a common base. There are some differences between STM8 and STM32C0 peripherals due to continuous improvement, and the addition of new functionalities. The comparison below helps the user to identify and use these improvements.

The major difference between the STM8 and the STM32 is the number of register bits: 32 or 16 bits in STM32. Only 8 bits in STM8. Sometimes, register names are similar.

# Figure 5. Register name sharing

| Offset | Register name<br>reset value | 15       | 14       | 13      | 12              | 1            | 10     | 6          | 8      | ,<br>,   | 9   | 5           | 4      | ъ       | 2       | ۰    | 0    |

|--------|------------------------------|----------|----------|---------|-----------------|--------------|--------|------------|--------|----------|-----|-------------|--------|---------|---------|------|------|

| 0x00   | SPIx_CR1                     | BIDIMODE | BIDIOE   | CRCEN   | CRCNEXT         | CRCL         | RXONLY | SSM        | SSI    | LSBFIRST | SPE | в           | BR [2: | 0]      | MSTR    | CPOL | CPHA |

|        | Reset value                  | 0        | 0        | 0       | 0               | 0            | 0      | 0          | 0      | 0        | 0   | 0           | 0      | 0       | 0       | 0    | 0    |

| 0x04   | SPIx_CR2                     | Res.     | LDMA_TX  | LDMA_RX | FRXTH           | DS[3:0]      |        | TXEIE      | RXNEIE | ERRIE    | FRF | <b>NSSP</b> | SSOE   | TXDMAEN | RXDMAEN |      |      |

|        | Reset value                  |          | 0        | 0       | 0               | 0            | 1      | 1          | 1      | 0        | 0   | 0           | 0      | 0       | 0       | 0    | 0    |

| 0x08   | SPIx_SR                      | Res.     | Res.     | Res.    | 101 P. 11 P. 12 | רובעבן ו:יטן |        | FRLVL[1:0] | FRE    | BSY      | OVR | MODF        | CRCERR | UDR     | CHSIDE  | TXE  | RXNE |

|        | Reset value                  |          |          |         | 0               | 0            | 0      | 0          | 0      | 0        | 0   | 0           | 0      | 0       | 0       | 1    | 0    |

| 0x0C   | SPIx_DR                      |          | DR[15:0] |         |                 |              |        |            |        |          |     |             |        |         |         |      |      |

| 0x0C   | Reset value                  | 0        | 0        | 0       | 0               | 0            | 0      | 0          | 0      | 0        | 0   | 0           | þ      | 0       | 0       | 0    | 0    |

## SPI/I2S register map and reset values

STM32C0: SPI register map

SPI register map and reset values

| Address<br>offset | Register<br>name      | 7         | 6            | 5     | 4       | 3    | 2      | 1    | 0    |

|-------------------|-----------------------|-----------|--------------|-------|---------|------|--------|------|------|

| 0x00              | SPI_CR1               | LSB FIRST | SPE          | BR2   | BR1     | BR0  | MSTR   | CPOL | CPHA |

|                   | Reset value           | 0         | 0            | 0     | 0       | 0    | 0      | 0    | 0    |

| 0x01              | SPI_CR2               | BDM       | BDOE         | CRCEN | CRCNEXT | -    | RXONLY | SSM  | SSI  |

|                   | Reset value           | 0         | 0            | 0     | 0       | 0    | 0      | 0    | 0    |

| 0x03              | SPI_SR                | BSY       | OVR          | MODF  | CRCERR  | WKUP | -      | TXE  | RXNE |

|                   | Reset value           | 0         | 0            | 0     | 0       | 0    | 0      | 1    | 0    |

| 0x04              | SPI_DR<br>Reset value |           | DR[7:0]<br>0 |       |         |      |        |      |      |

STM8: SPI register map

DT55847V2

|         | Peripheral                                           | STM32C0 series                                                                                   | STM8S series      | STM8L series           |

|---------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|------------------------|

|         | Power supply                                         |                                                                                                  | See Table 8       |                        |

|         | Core                                                 | Cortex <sup>®</sup> M0+ (32-bit)                                                                 | STM8 core (8-bit) | STM8 core (8-bit)      |

|         | Maximum frequency                                    | 48 MHz                                                                                           | Up to 24 MHz      | 16 MHz                 |

|         | Flash memory                                         | Up to 256 Kbytes                                                                                 | Up to 128 Kbytes  | Up to 64 Kbytes        |

|         | SRAM                                                 | Up to 36 Kbytes                                                                                  | Up to 6 Kbytes    | Up to 4 Kbytes         |

|         | EEPROM                                               | Emulated in the flash memory <sup>(1)</sup>                                                      | Up to 2 Kbytes    | Up to 2 Kbytes         |

|         | General purpose (16-bit)                             | Up to 5                                                                                          | Up to 2           | Up to 3                |

|         | General purpose (32-bit)                             | <b>1</b> <sup>(5)</sup>                                                                          | -                 | -                      |

| TIMER   | Advanced (16-bit)                                    | 1                                                                                                | 1 <sup>(5)</sup>  | 1 <sup>(5)</sup>       |

|         | Basic (8-bit)                                        | 0                                                                                                | 1 <sup>(5)</sup>  | 1 <sup>(5)</sup>       |

|         | ADC                                                  | 1                                                                                                | 1                 | 1                      |

|         | DAC                                                  | (2)(3)(4)                                                                                        | -                 | Up to 2 <sup>(5)</sup> |

| DMA (nu | mber of independently configurable channels request) | Up to 7                                                                                          | -                 | Up to 4                |

|         | USART                                                | Up to 4                                                                                          | Up to 2           | Up to 3                |

|         | SPI                                                  | Up to 2                                                                                          | 1                 | Up to 2                |

|         | l <sup>2</sup> C                                     | Up to 2                                                                                          | Up to 4           | Up to 2                |

|         | I <sup>2</sup> S (Inter-IC-sound)                    | 1                                                                                                | -                 | -                      |

|         | CRC                                                  | Х                                                                                                | -                 | -                      |

|         | RTC                                                  | Х                                                                                                | -                 | X <sup>(5)</sup>       |

|         | WWDG                                                 | Х                                                                                                | Х                 | X <sup>(5)</sup>       |

|         | IWDG                                                 | Х                                                                                                | Х                 | X <sup>(5)</sup>       |

|         | LCD                                                  | _(3)(4)                                                                                          | -                 | X                      |

|         | COMP                                                 | _(2)(3)(4)                                                                                       | -                 | Up to 2                |

|         | CAN                                                  | FDCAN <sup>(5)</sup>                                                                             | beCAN             | beCAN                  |

|         | USB                                                  | X <sup>(5)</sup>                                                                                 | -                 | -                      |

| Boo     | otloader supported peripheral                        | USART / I <sup>2</sup> C / SPI <sup>(5)</sup> /<br>USB DFU <sup>(5)</sup> / FDCAN <sup>(5)</sup> | UART/SPI          | UART/SPI               |

## Table 4. Peripheral summary of STM32C0 series and STM8S and STM8L series

1. Refer to AN4894.

2. The STM32G0 series supports this feature.

3. The STM32L0 series supports this feature.

4. The STM32L4 series supports this feature.

5. Not on all devices.

## 5.2 System architecture

The STM32C0 series implement an Arm<sup>®</sup> 32-bit architecture with Cortex<sup>®</sup>-M0+ core, while the STM8L/S series use the STM8 8-bit proprietary core. The STM32 uses a RISC instruction set, while the STM8 uses a CISC instruction set. This allows the STM32 to be faster, at the price of greater code size, as described below. See in Table 5 the full list of differences.

| Feature                | Cortex <sup>®</sup> -M0+                     | STM8 core     |

|------------------------|----------------------------------------------|---------------|

| Data path              | 32-bit                                       | 8-bit         |

| Architecture           | Von Neumann                                  | Harvard       |

| Pipeline               | Two stages                                   | Three stages  |

| Instruction set        | RISC                                         | CISC          |

| Program bus data width | 32-bit                                       | 32-bit        |

| Prefetch buffer        | 2 x 32-bit                                   | 2 x 32-bit    |

| Debug interface        | 2-wire (SWD)                                 | 1-wire (SWIM) |

| Number of registers    | 15 x 32-bit, 1 x 64-bit, 3 special registers | 11 x 8-bit    |

| Cache instruction      | 16 bytes                                     | NA            |

#### Table 5. Comparison of CPU core

Aligned memory, is an address where an "n-byte" value is stored. It must be divisible by "n". This means:

- Word (32-bit) aligned to an address divisible by 4 [UINT32/INT32].

- Half-word (16-bit) aligned to an address divisible by 2 [UINT16/INT16].

- Byte accesses are always aligned [UINT8/INT8].

The Cortex<sup>®</sup> -M0+ uses the ARM-v6M. This architecture does not permit an unaligned memory access. If attempted, the CPU raises a hard fault exception.

Usually, compilers are aware of the aligned access requirement, so they automatically adjust in several ways:

- Automatically place variables in aligned addresses.

- Use of packed structures to align members.

- Use of byte-by-byte access whenever a variable is unaligned for some reason.

## 5.3 Code density and CoreMark<sup>®</sup>

To help the developer to find the appropriate sales type for their needs, a comparison code size has been made on the CoreMark<sup>®</sup>. It is easily portable between both families. It ensures that compilers cannot precompute the results. Moreover, it provides the user with a benchmark comparison based on the IAR Embedded Workbench<sup>®</sup>, with different code optimization.

For further information about the code density between the libraries available on the STM32C0 series, check the Programming part.

| Optimization | Size  | Balanced | Medium | Speed | Unit  |

|--------------|-------|----------|--------|-------|-------|

| STM32C0      | 16073 | 16921    | 17085  | 20473 | Bytes |

| STM8L        | 15188 | 14752    | 15371  | 18935 | Bytes |

#### Table 6. Code density between STM32C0 series and STM8L series

The code size does not increase excessively. However, it is necessary to accommodate an increase of 6 to 15% in code size.

The CoreMark<sup>®</sup> is not the perfect benchmark to compare both families. This is because one uses 8 bits, and the other uses 32 bits, while the CoreMark<sup>®</sup> uses a 16/32-bit variable. However, it indicates that the Cortex<sup>®</sup>-M0+ is seven times better than the STM8 8-bit core.

## Table 7. CoreMark<sup>®</sup> comparison

| STM32C0 series | STM8L/S series | Unit         |

|----------------|----------------|--------------|

| 2.22           | 0.30           | CoreMark/MHz |

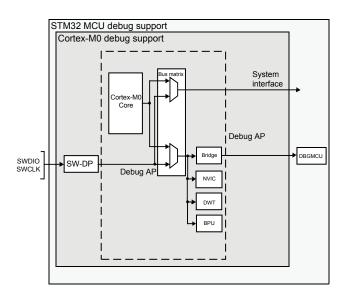

## 5.4 Debug

The STM32 series uses a different debug methodology with respect to the STM8L/S series. The STM32 devices need two wires for debug, while one is needed in STM8 devices (SWIM).

The new debug methodology allows:

- SW-DP: serial wire

- BPU: break point unit

- DWT: data watchpoint trigger

- Flexible debug pinout assignment

- NVIC debug

- MCU debug box (support for low-power modes, control over peripheral clocks, etc.)

## Figure 6. Block diagram of STM32C0 MCU and Cortex<sup>®</sup>-M0 +-level debug support

## 5.5 Power control peripheral

In the STM32C0 series, the PWR controller presents some differences compared to the STM8S/L series. This is especially the case for the STM8S series, which has a 5.0 V supply.

| PWR                     | STM32C0 series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | STM8S series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | STM8L series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Power supplies          | <ul> <li>V<sub>DD</sub>: 2.0 V to 3.6 V<br/>(one pair V<sub>DD</sub>/V<sub>SS</sub>) is<br/>the external power<br/>supply for the internal<br/>regulator and the<br/>system analog such as<br/>reset, power<br/>management, and<br/>internal clocks</li> <li>V<sub>DDA</sub>: is the analog<br/>power supply for the<br/>A/D converter and<br/>shorted to V<sub>DD</sub> due to<br/>the low number of pins</li> <li>V<sub>DDIOX</sub>: is the power<br/>supply for the I/Os to<br/>reduce the number of<br/>supply pin, usually this<br/>power supply is shorten<br/>to V<sub>DD</sub>. However on<br/>some products a<br/>second V<sub>DDIO2</sub> power<br/>supply is available.</li> <li>V<sub>REF+</sub>: 2.0 V to V<sub>DDA</sub> is<br/>the input reference<br/>voltage for the ADC, on<br/>a lower pin-count<br/>package V<sub>REF+</sub> is<br/>shorted to V<sub>DD</sub></li> </ul> | <ul> <li>V<sub>DD</sub>: 2.95 V to 5.5 V<br/>(one pair V<sub>DD</sub>/V<sub>SS</sub>) is<br/>the external power<br/>supply for the main<br/>regulator ballast<br/>transistor supply</li> <li>V<sub>DDIO</sub>: 3.0 V to 5.0 V is<br/>the power supply for<br/>the I/Os and on a lower<br/>pin-count package is<br/>shorted to V<sub>DD</sub>, due to<br/>the low number of pins</li> <li>V<sub>DDA</sub>: 3.0 V to 5.5 V<br/>(one pair of V<sub>DDA</sub>/<br/>V<sub>SSA</sub>) is the analog<br/>power supply for the<br/>A/D converter and on a<br/>lower pin-count<br/>package is shorted to<br/>V<sub>DD</sub>, due to the low<br/>number of pins</li> <li>V<sub>REF+</sub>: 2.0 V to V<sub>DDA</sub> is<br/>the input reference<br/>voltage for the ADC, on<br/>a lower pin-count<br/>package V<sub>REF+</sub> is<br/>shorted to V<sub>DD</sub></li> </ul> | <ul> <li>V<sub>DD</sub>: 1.65 V or 1.8 V to<br/>3.6 V is the external<br/>power supply for the<br/>main regulator</li> <li>V<sub>DDA</sub>: 1.8 V to 3.6 V is<br/>the analog power<br/>supply for the analog<br/>part and on lower pin-<br/>count package is<br/>shorted to V<sub>DD</sub>, due to<br/>the low number of pins</li> <li>V<sub>DDIO</sub>: 1.8 V to 3.6 V is<br/>the power supply for<br/>the I/Os and on lower<br/>pin-count package is<br/>shorted to V<sub>DD</sub>, due to<br/>the low number of pins</li> <li>V<sub>REF+</sub>: If V<sub>DDA</sub> &gt; 2.4 V:<br/>2.4 V to V<sub>DDA</sub> else:<br/>V<sub>REF+</sub> = V<sub>DDA</sub> is the<br/>input reference voltage<br/>for the ADC, on lower<br/>pin-count package<br/>V<sub>REF+</sub> is shorted to<br/>V<sub>DD</sub></li> </ul> |  |  |  |  |  |

| Power supply supervisor | Integrated     POR/PDR/BOR     circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Integrated POR/PDR     circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>Integrated<br/>POR/PDR/BOR<br/>circuitry</li> <li>Programmable voltage<br/>detector (PVD)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

## Table 8. Power control peripheral

## 5.6 Power consumption mode

The STM32C0 series and the STM32 family generally have different low-power modes compared to the STM8L/S series. There are four low-power modes:

- Sleep

- Stop

- Standby

- Shutdown

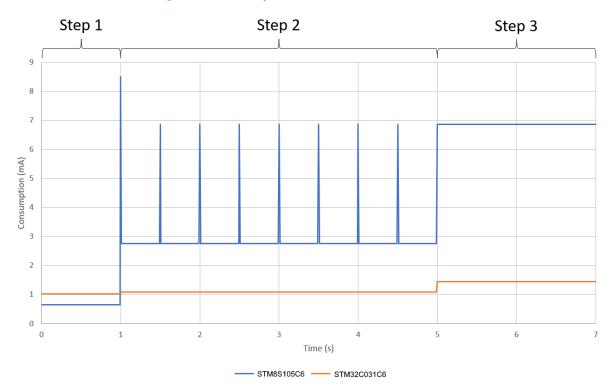

The STM32C0 series has a lower consumption than the STM8L under most conditions. The different consumption modes are described below.

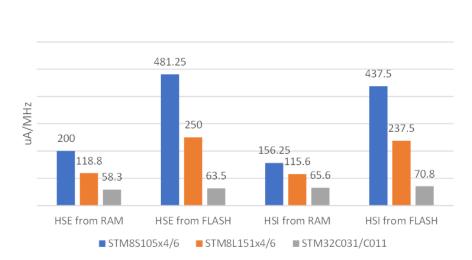

#### Dynamic power consumption

Respective to the STM8, the dynamic consumption of the STM32C0 is lower. Regarding the Figure 7, the STM32C0 series can be up to 7.5 times more efficient than the STM8S series, and up to twice as efficient as the STM8L series.

## Figure 7. STM32C0 versus STM8 dynamic consumption

#### Static power consumption

In the STM32C0 series and the STM8L/S series, the low-power modes have different names. However, the low-power modes have some similarities, so it is possible to compare them.

| Consumption mode   |                      | Clock          | STM32C011/31 | STM8S105C4/6 | STM8L151x4/6 | Unit |

|--------------------|----------------------|----------------|--------------|--------------|--------------|------|

| Wait/sleep<br>mode | From flash<br>memory | HSE 16 MHz     | 0.33         | 1.55         | 1.00         | mA   |

| mode               | From RAM             |                | 0.32         | 1.55         | 0.76         |      |

| Stop/active        | e halt mode          | LSI/LSE        | 80           | 200          | 0.90         | μA   |

| Standby/           | halt mode            | All clocks off | 7.45         | 6.50         | 0.35         | μA   |

| Shutdov            | wn mode              | All clocks off | 19           | NA           | NA           | nA   |

#### Table 9. Low-power consumption comparison

- Sleep mode corresponds to wait mode in the STM8. The CPU is clocked off, but other peripherals and the interrupt controller continue to run.

- Stop mode is like active halt mode. The HSI/HSE clocks are stopped, and the SRAM is retained.

- Standby mode is similar to halt mode. The HSE/HSI clocks are off. The LSI and LSE clocks can be running if the application uses IWDG. The main difference, however, is that the RAM is powered off in the STM32C0.

- Shutdown mode has no equivalent in the STM8. It is the ultimate low-power mode. All clocks and peripherals are off.

## Wake-up source

| PWR                                          | STM32C0 series                                                                                                                                                                                                                                                                                               | STM8S series                                                                                                                                                                                                                                            | STM8L series                                                                                                                                                                                                                                                                              |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-power<br>modes and<br>wake-up<br>sources | Sleep mode<br>Peripheral event/interrupt<br>EXTI interrupt/event<br>NVIC IRQ interrupt<br>IWDG<br>Reset<br>Stop mode<br>Peripheral event/interrupt<br>EXTI interrupt/event<br>NVIC IRQ interrupt<br>IWDG<br>Reset<br>Standby mode<br>Wake-up pins<br>IWDG<br>Reset<br>Shutdown mode<br>Wake-up pins<br>Reset | Wait mode<br>All internal or external<br>interrupts (including auto wake-<br>up)<br>Reset<br>IWDG<br>Active halt mode<br>Auto wake-up<br>External interrupts<br>Reset<br>IWDG<br>Halt mode<br>External interrupts<br>Reset<br>IWDG<br>Halt mode<br>IWDG | Wait mode All internal or external interrupts Wake-up events Reset WDG Low-power run mode Software sequence Reset WDG Low-power wait mode Internal or external event Reset WDG Active halt mode External interrupts RTC interrupts RESet WDG Halt mode External interrupts Reset WDG IWDG |

## Table 10. Wake-up source comparison

## 5.7 Reset and clock controller (RCC) interface

## 5.7.1 Clocks

## Table 11. RCC peripheral STM32C0 series versus STM8S/L series

| RCC                                                   | STM32C0 series                                                                                                                                                                                                                            | STM8S series                                                                 | STM8L series                                                                 |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| HSI48                                                 | 48 MHz high-speed internal RC oscillator                                                                                                                                                                                                  | -                                                                            | -                                                                            |

| HSIUSB48 <sup>(1)</sup>                               | 48 MHz high-precision RC oscillator to the clock USB                                                                                                                                                                                      | -                                                                            | -                                                                            |

| HSI16                                                 | -                                                                                                                                                                                                                                         | 16 MHz high-speed internal RC oscillator                                     | 16 MHz high-speed internal RC oscillator                                     |

| LSI                                                   | 32 kHz low-speed internal RC                                                                                                                                                                                                              | 128 kHz low-speed internal RC                                                | 38 kHz low-speed internal RC                                                 |

| HSE                                                   | 4 to 48 MHz                                                                                                                                                                                                                               | 1 to 24 MHz                                                                  | 1 to 16 MHz                                                                  |

| LSE                                                   | 32.768 kHz                                                                                                                                                                                                                                | -                                                                            | 32.768 kHz                                                                   |

| System clock source                                   | HSI48, HSIUSB48 <sup>(1)</sup> , HSE, LSI, LSE                                                                                                                                                                                            | HSI16, HSE, LSI                                                              | HSI16, HSE, LSI, LSE                                                         |

| System clock<br>frequency                             | <ul> <li>Up to 48 MHz</li> <li>12 MHz after reset based on HSI</li> </ul>                                                                                                                                                                 | <ul> <li>Up to 24 MHz</li> <li>2 MHz after reset<br/>based on HSI</li> </ul> | <ul> <li>Up to 16 MHz</li> <li>2 MHz after reset<br/>based on HSI</li> </ul> |

| APB frequency                                         | Up to 48 MHz                                                                                                                                                                                                                              | -                                                                            | -                                                                            |

| RTC clock source                                      | LSI, LSE, or HSE clocks divided by 32                                                                                                                                                                                                     | -                                                                            | HSI, HSE, LSI, LSE                                                           |

| Clock output                                          | MCO1/2: LSI, LSE, SYSCLK, HSI48,<br>HSIUSB48 <sup>(1)</sup> , HSE<br>LSCO: LSI, LSE available in stop mode                                                                                                                                | CCO: HSE, HSI,<br>HSIDIV, LSI, MASTER,<br>CPU                                | CCO: HSE, HSI, LSI, LSE                                                      |

| Internal oscillator<br>measurement and<br>calibration | <ul> <li>Internal/external clock measurement inputs</li> <li>TIM14 inputs: GPIO, RTC, HSE/32, MCO, MCO2</li> <li>TIM16 inputs: GPIO, LSI, LSE, MCO2</li> <li>TIM17 inputs: GPIO, HSIUSB48/256<sup>(1)</sup>, HSE/32, MCO, MCO2</li> </ul> | -                                                                            | Internal/external clock<br>measurement inputs<br>• TIM2/3: LSE               |

1. Only available on STM32C071xx devices.

#### Table 12. High-speed and low-speed clock internal accuracy comparison

| Clock accuracy         | Temperature | STM32C03/C01   | STM8S105C6 | STM8L101F1  |

|------------------------|-------------|----------------|------------|-------------|

|                        | Full range  | -2.5% to 2%    | ±3%        | -4.5% to 3% |

| HSI factory calibrated | 0°C to 85°C | ±1%            | ±2%        | -2.5% to 2% |

|                        | 30°C        | -0.83% to 0.2% | ±1%        | ±1%         |

| LSI                    | Full range  | ±7%            | ±20%       | -12% to 11% |

The STM32C0 has a better clock accuracy than the STM8. It can clock other peripherals with the MCO output. The HSI can be used for USART communication.

## 5.7.2 Reset

•

The STM32C0 series has several types of reset:

- Power reset: this sets all registers to their reset values. Exiting Standby mode is an exception. In this case the registers outside the VCORE domain (back up registers, IWDG, Standby/Shutdown mode control) are not impacted.

- System reset: this resets all registers to their reset value, except the reset flags, and the RTC registers.

• RTC domain reset: this only affects the RTC domains (LSE oscillator, RTC and RCC\_CSR1 register). The main difference is the addition of the software reset. It is no longer mandatory to use a trick with the WWDG to emulate a software reset, as in the STM8.

| Reset source                    | STM32C0 series      | STM8S series | STM8L series |

|---------------------------------|---------------------|--------------|--------------|

| Power-on Reset/Power-down reset | X <sup>(1)(2)</sup> | x            | X            |

| Brown-out reset                 | X <sup>(1)</sup>    | X            | Х            |

| Power voltage detection (PVD)   | -                   | -            | Х            |

| Exit from Standby mode          | X <sup>(1)</sup>    | -            | -            |

| Exit from Shutdown mode         | X <sup>(1)</sup>    | -            | -            |

| Low level on the NRST pin       | X <sup>(2)</sup>    | X            | Х            |

| WWDG reset                      | X <sup>(2)</sup>    | X            | Х            |

| IWDG reset                      | X <sup>(2)</sup>    | X            | X            |

| Software reset                  | X <sup>(2)</sup>    | -            | -            |

| Low-power mode security reset   | X <sup>(2)</sup>    | -            | -            |

| Option-byte loader reset        | X <sup>(2)</sup>    | -            | -            |

| EMC reset                       | -                   | Х            | -            |

| Illegal opcode reset            | -                   | Х            | Х            |

#### Table 13. Reset source comparison

1. Power reset

2. System reset

## 5.8 Nested vectored interrupt controller (NVIC)

STM32C0 devices do not use the same interrupt system as STM8 devices. They use a nested vectored interrupt controller (NVIC). There are some similarities with the STM8L/S series such as: interrupt vector, priority management, and EXTI. In the STM32C0, each IP has its own vector, so there is no interrupt sharing (as in STM8L151x6/8 STM8L152x6/8).

#### Table 14. Interrupt features comparison

| Parameter                                      | STM32C0 series                               | STM8S series                                              | STM8L series                                                    |

|------------------------------------------------|----------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------|

| Interrupt vectors                              | Up to 32 interrupt vectors (+ 5 system ones) | Up to 32 interrupt vectors                                |                                                                 |

| Interrupt priorities                           | 4 levels<br>lower number = higher priority   | 3 levels                                                  |                                                                 |

| Disable interrupts                             | yes, apart from NMI and HardFault            | Yes                                                       |                                                                 |

| External interrupt channels linked to IO lines |                                              | 5 external interrupts linked to ports                     | 8 external interrupts linked to IO<br>lines + 4 linked to ports |

| Reset vector                                   | 4 bytes (address of the IRQ procedure)       | 4 bytes (0x82 code + 24-bit address of the IRQ procedure) |                                                                 |

|                                                | 16 cycles to save context                    | 9 cycles to save context                                  |                                                                 |

| Interrupt latency                              | 16 cycles to restore context                 | 9 cycles to restore context                               |                                                                 |

|                                                | Tail chaining supported                      | Tail chaining supported                                   |                                                                 |

The Cortex<sup>®</sup>-M0+ has six system interrupts (three more than the STM8). The priority of reset, NMI and HardFault are fixed, in contrast to SVC, PendSV, and SysTick, which are programmable.

## Table 15. System interrupts comparison

| Offset | STM32C0 series                                                                                                                                  | STM8L/S series                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | -                                                                                                                                               | Reset: Address of the application start                                                                                                                    |

| 0x04   | Reset: Address of the application start                                                                                                         | TRAP: Software interrupt                                                                                                                                   |

| 0x08   | NMI: Nonmaskable interrupt connected to SRAM parity error, HSE, and LSE clock security systems (may be slightly different in other STM32 lines) | TLI: Top-level interrupt. (It is assigned to various interrupt sources depending on the family, that is, in STM32L15xx8 it is TIM2 and TIM4 overflow IRQ.) |

| 0x0C   | HardFault: Reports all issues related to bus/memory accesses                                                                                    | -                                                                                                                                                          |

| 0x2C   | SVC: System service call, software interrupt. Used by operating systems                                                                         | -                                                                                                                                                          |

| 0x38   | PendSV: Pendable request for system service software interrupt. Used by operating systems                                                       | -                                                                                                                                                          |

| 0x3C   | SysTick: Interrupt from the built-in 24-bit counter (part of the core), used for delays, timeouts, and operating system timing                  | -                                                                                                                                                          |

There are two ways to handle the interrupts with the help of STM32CubeMX: the hardware abstraction layer (HAL), and the low layer (LL). The first one takes longer, due to the high level, but it is easier to implement the interrupt processing flow.

## Table 16. Interrupt handler comparison

| Features                  | STM32C0 LL library                                                                                | STM32C0 HAL library                                                                                                                                                                                                                                                               | STM8 SPL                                                                                                  |

|---------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Vector table definition   | startup_stm32c0xx.s                                                                               | startup_stm32c0xx.s                                                                                                                                                                                                                                                               | stm8_interrupt_vector.c                                                                                   |

| Interrupt processing flow | startup file with complete IRQ<br>table definition<br>↓<br>Interrupt handler in<br>stm32c0xx_it.c | startup file with complete IRQ<br>table definition<br>↓<br>Interrupt handler in<br>stm32c0xx_it.c<br>↓<br>HAL IRQ handler in<br>stm32c0xx_hal_ppp.c <sup>(1)</sup> to<br>handle flags and status bits<br>↓<br>Final callback overwriting<br>"weak" callback within HAL<br>library | stm8_interrupt_vector.c with<br>complete IRQ table definition<br>↓<br>Interrupt handler in<br>stm8xx_it.c |

1. "ppp" = peripheral name (ADC, UART, RCC etc.)

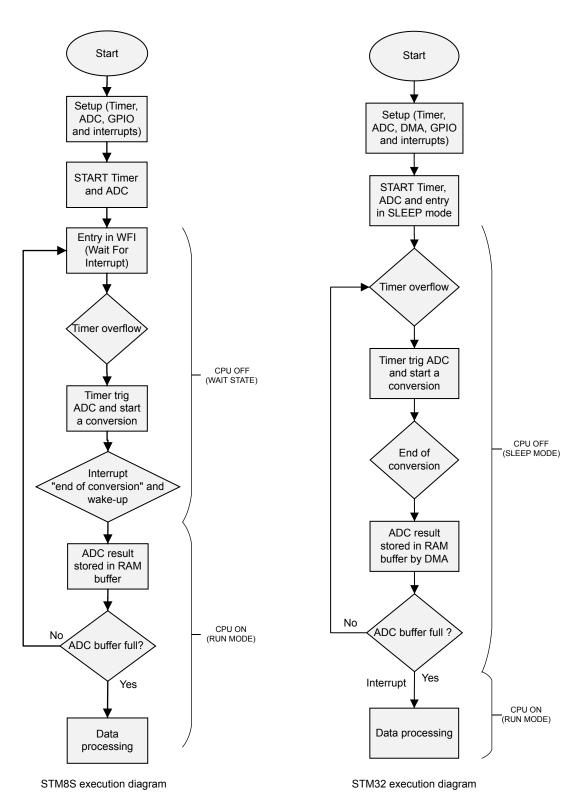

#### 5.9

## DMA

The DMA IP is new in the STM32C0 series, compared to the STM8S series and some STM8L lines. It is clearly a major asset to improve the product consumption when it is possible to make a memory transfer without a CPU.

#### Table 17. DMA peripheral

| Feature                                                                                                                        | STM32C0 series                                      | STM8S<br>series | STM8L series                                                      |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|-------------------------------------------------------------------|

| DMA channel                                                                                                                    | I Up to 7                                           |                 | 4 (only on STM8L05xxx/15xxx,<br>STM8L162xx)                       |

| DMA controller DMAMUX:<br>• The trigger for each channel is either a peripheral request, or any of the four generated requests |                                                     | -               | Up to 3 requests per channel                                      |

| Transfer size                                                                                                                  | Byte, half-word, word                               | -               | Byte, half-word                                                   |

| Transfer type Peripherals to memory, memory to peripherals, memory to memory, and peripherals to peripherals                   |                                                     | -               | Peripherals to memory, memory to peripherals and memory to memory |

| Interrupt request per channel                                                                                                  | Transfer complete, half transfer, or transfer error | -               | Transfer complete or half transfer                                |

| Addressing mode                                                                                                                | Incrementing                                        | -               | Incrementing and decrementing                                     |

## 5.10 GPIO interface

The STM32C0 GPIOs are different to those of the STM8L/S series.

Some new features are available in STM32C0 series devices:

- Internal pull-down resistor

- Output open-drain with pull-up or pull-down capability

- Output push-pull with pull-up or pull-down capability

- Alternate function push-pull with pull-up or pull-down capability

- Alternate function open-drain with pull-up or pull-down capability

- Analog input

- V<sub>IN</sub> is no longer limited by V<sub>DD</sub> + 0.3 V, but by 5.5 V (see Table 19)

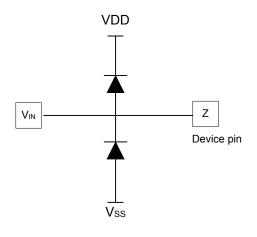

Due to different pin protection architectures, and as for all STM32 devices, positive current injection is not allowed on the STM32C0. (An exception is certain MCUs with switchable diodes.) In fact, there is no clamping diode between the IO and  $V_{DD}$  (due to 5 V tolerant capability). If the user application needs to be protected against positive injection, it is necessary to add external clamping diodes (see Figure 8). For further details about the GPIO (FT) and EMC design, refer to AN4899 and AN1709, respectively.

#### Figure 8. Clamping diodes protection

DT57077V2

The STM32C0 series can share the same pin for reset or GPIO functionality. One specific pin, PF2, is configured with an appropriate value in the option bytes. In the small package, due to the limited number of pins, multiple GPIOs are connected to the I/Os.

The user can also freeze the GPIO control register by applying a specific write sequence. Moreover, each pin of the GPIO can be set as an analog input (Schmitt trigger deactivated) to reduce the power consumption.

| Feature      | STM32C0 series                  | STM8L/S series   |

|--------------|---------------------------------|------------------|

|              | (2 bits $\rightarrow$ 4 speeds) |                  |

|              | 3 MHz                           | 1 bit (2 speeds) |

| Speeds       | 15 MHz                          | 2 MHz            |

|              | 60 MHz                          | 10 MHz           |

|              | 80 MHz                          |                  |

| Pull-up/down | YES                             | Pull-up only     |

## Table 18. GPIO differences between STM32C0 series and STM8L/S series

#### Table 19. GPIO input voltage comparison

| Voltage | STM32C0 series                 | STM8S series                                  | STM8L series                                     |

|---------|--------------------------------|-----------------------------------------------|--------------------------------------------------|

| VIL     | 0 V to 0.3 × V <sub>DD</sub>   | -0.3 V to 0.3 × V_DD                          | $V_{SS}\mbox{-}0.3$ V to 0.3 $\times$ $V_{DD}$   |

| VIH     | 0.7 × V <sub>DD</sub> to 5.5 V | 0.7 × V <sub>DD</sub> to V <sub>DD</sub> +0.3 | $0.7$ × $V_{DD}$ to 5 V (for 5 V tolerant input) |

## 5.11 RTC

The STM8S series does not have an RTC. However, an RTC is present on the STM8L series.

| Peripheral | Feature           | STM32C0 series                                   | STM8L (low-density devices)                | STM8L (medium-<br>density devices) | STM8L (medium+ and<br>high-density devices) |

|------------|-------------------|--------------------------------------------------|--------------------------------------------|------------------------------------|---------------------------------------------|

| RTC        | Number of alarms  | 1                                                | 1 (or wake-up signal)                      |                                    | 1 (or wake-up signal)                       |

| RTC        | Number of outputs | 2 (RTC calibration<br>+ alarm/wake-up<br>signal) | 2 (RTC calibration + alarm/wake-up signal) |                                    | 2 (RTC calibration + alarm/wake-up signal)  |

| Tamper     | Number of events  | 0                                                |                                            | 0                                  | 3                                           |

## Table 20. RTC peripheral

## 5.12 USART

## Table 21. USART peripheral

| Feature                                                         | STM32C0 series                                                                                                                 | STM8S series             | STM8L series                                       |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------|

| Configurable oversampling method                                | 16 or 8                                                                                                                        | -                        | -                                                  |

| Rx/Tx FIFO                                                      | 2 × 8 bytes                                                                                                                    | 2 × 1 byte (TDR/<br>RDR) | 2 × 1 byte (TDR/RDR)                               |

| Common programmable transmit and receive baud rate              | YES                                                                                                                            | -                        | -                                                  |

| Programmable data word length                                   | 7, 8, or 9 bits                                                                                                                | 8 or 9 bits              | 8 or 9 bits                                        |

| Programmable data order with MSB-first or LSB-first shifting    | YES                                                                                                                            | -                        | -                                                  |

| SPI slave transmission underrun error flag                      | YES                                                                                                                            | -                        | -                                                  |

| DMA                                                             | Continuous communications<br>using DMA<br>Received/transmitted bytes are<br>buffered in reserved SRAM using<br>centralized DMA | -                        | Configurable multibuffered communication using DMA |

| Separate signal polarity control for transmission and reception | YES                                                                                                                            | -                        | -                                                  |

| Swappable Tx/Rx pin configuration                               | YES                                                                                                                            | -                        | -                                                  |

| Hardware flow control for modem and RS-485 transceiver          | YES                                                                                                                            | -                        | -                                                  |

| Wake-up from low-power mode                                     | YES                                                                                                                            | -                        | -                                                  |

| Modbus                                                          | YES                                                                                                                            | -                        | -                                                  |

# 5.13 I<sup>2</sup>C

## Table 22. I<sup>2</sup>C configuration

| Feature              | STM32C0 series                                                                             | STM8S series                                                | STM8L series                                                |

|----------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|

| Communication speeds | Standard-mode (up to 100 kHz)<br>Fast-mode (up to 400 kHz)<br>Fast-mode plus (up to 1 MHz) | Standard speed (up to 100 kHz<br>Fast speed (up to 400 kHz) | Standard speed (up to 100 kHz<br>Fast speed (up to 400 kHz) |

| SMBus                | 3.0                                                                                        | -                                                           | 2.0                                                         |

| PMBus                | 1.3                                                                                        | -                                                           | YES                                                         |

| DMA capability       | 1-byte buffer                                                                              | -                                                           | 1-byte buffer                                               |

| Clock selection      | PCLK, SYSCLK, HSIKER                                                                       | -                                                           | -                                                           |

## 5.14 Flash memory

The STM32C0 series has a maximum frequency of 48 MHz, and the flash memory's maximum frequency is 24 MHz. To compensate the flash memory speed, and to be sure to have valid and uncorrupted data, a wait state feature is added. The wait state feature is not implemented on most STM8 products, because the CPU speed does not go above the flash memory speed.

#### Table 23. Flash memory

| Feature                                   | STM32C0 series                                                                                                | STM8S series                                                                            | STM8L series                                                                                                                 |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Page size                                 | • 2 Kbytes                                                                                                    | <ul> <li>64 bytes (low and medium density)</li> <li>128 bytes (high density)</li> </ul> | <ul> <li>64 bytes (low density)</li> <li>128 bytes (medium and medium+ density)</li> <li>256 bytes (high density)</li> </ul> |

| Data width                                | 64-bit                                                                                                        | 32-bit                                                                                  | 32-bit                                                                                                                       |

| Programming granularity                   | 8-byte                                                                                                        | 4-byte                                                                                  | 4-byte                                                                                                                       |

| Flash read protection<br>(RDP)            | <ul> <li>Three levels:</li> <li>No protection</li> <li>Read and write protection</li> <li>No debug</li> </ul> | Two levels:<br>No protection<br>Read and write<br>protection                            | Two levels:<br>• No protection<br>• Read and write protection                                                                |

| Flash writes protection area              | Two configurable areas<br>(WRP)                                                                               | One configurable area (UBC)                                                             | One configurable area (UBC)                                                                                                  |

| Flash proprietary code readout protection | Two configurable areas (PCROP)                                                                                | -                                                                                       | One configurable area (ROP)                                                                                                  |

| "On Time" programmable area               | 1 Kbytes                                                                                                      | -                                                                                       | -                                                                                                                            |

## Table 24. Flash memory characteristics comparison

| Parameter                         | STM32C0 series | STM8S105x6 | STM8L152x6 | Unit    |

|-----------------------------------|----------------|------------|------------|---------|

| Page size                         | 2 k            | 128        | 128        | byte    |

| Programing time for one page      | 21.8           | 6          | 6          | ms      |

| Frogramming time for one page     | 10.6           | 46.9       | 46.9       | µs/byte |

| East programing time for one page | 13.7           | 3          | 3          | ms      |

| Fast programing time for one page | 6.7            | 23.4       | 23.4       | µs/byte |

| Page proce time                   | 22             | 3          | 3          | ms      |

| Page erase time                   | 10.7           | 23.4       | 23.4       | µs/byte |

## 5.15 SRAM

## Table 25. SRAM density, STM32C0 series versus STM8L/S series

| Maximum flash<br>memory density | STM32C0 series                         | STM8S series                                                 | STM8L series           |

|---------------------------------|----------------------------------------|--------------------------------------------------------------|------------------------|

| 4 Kbytes                        | -                                      | STM8S103F2: 1 Kbytes                                         | STM8L151x2: 1 Kbytes   |

| 8 Kbytes                        | -                                      | STM8S103x3/STM8S001J3/<br>STM8S003x3/STM8S903x3: 1<br>Kbytes | STM8L151x3: 1 Kbytes   |

| 16 Kbytes                       | STM32C011x4: 6 Kbytes                  | STM8S105x4: 2 Kbytes                                         | STM8L151x4/STM8L152x4: |

| 10 Kbytes                       | STM32C031x4: 12 Kbytes                 | STINUS TUSA4. 2 Rubyles                                      | 2 Kbytes               |

| 32 Kbytes                       | STM32C011x6: 6 Kbytes                  | STM8S005x6/STM8S105x6: 2<br>Kbytes                           | STM8L151x6/STM8L152x6: |

| 52 Abytes                       | STM32C031x6, STM32C051x6:<br>12 Kbytes | STM8S207x6/STM8S208x6: 6<br>Kbytes                           | 2 Kbytes               |

| 64 Kbytes                       | STM32C051x8: 12 Kbytes                 | STM8S007x8/STM8S207x8/                                       | STM8L151x8/STM8L152x8: |

| 04 Rbytes                       | STM32C071x8: 24 Kbytes                 | STM8S208x8: 6 Kbytes                                         | 4 Kbytes               |

|                                 | STM32C071xB: 24 Kbytes                 |                                                              |                        |

| 128 Kbytes                      | STM32C091xB: 36 Kbytes                 | STM8S207xB/STM8S208xB: 6<br>Kbytes                           | -                      |

|                                 | STM32C092xB: 30 Kbytes                 |                                                              |                        |