# Migrating from STM32L4 and STM32L4+ to STM32U3 MCUs

# Introduction

The designers of STM32 microcontroller applications must have the possibility to easily replace one microcontroller type with another from the same product family or products from a different family. The reasons for migrating an application to a different microcontroller can be, for example:

- To fulfill higher product requirements, extra demands on memory size, or an increased number of I/Os.

- To meet cost reduction constraints that require a switch to smaller components and shrinking the PCB area.

This document details the steps to migrate from an existing design based on the STM32L4 and STM32L4+ MCUs to an application based on one of the STM32U3 MCUs.

This document provides the full set of features available for STM32L4 and STM32L4+ MCUs, and the equivalent features of STM32U3 MCUs. This document also provides guidelines on both hardware and peripheral migration.

To better understand the information inside this application note, the user must be familiar with the STM32 microcontroller family.

This application note is a complement to the STM32L4, STM32L4+, and STM32U3 datasheets and reference manuals.

For additional information, refer to the product datasheets and reference manuals, available from www.st.com.

Note:

# 1 General information

This document applies to Arm<sup>®</sup>-based microcontrollers.

Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

### **Referenced documents**

## Table 1. Referenced documents

| Reference<br>number | Document ID | Document title                                                                                |

|---------------------|-------------|-----------------------------------------------------------------------------------------------|

| [1]                 | RM0394      | STM32L41xxx/42xxx/43xxx/44xxx/45xxx/46xxx Arm <sup>®</sup> -based 32-bit MCUs                 |

| [2]                 | RM0351      | STM32L47xxx, STM32L48xxx, STM32L49xxx, and STM32L4Axxx $\rm Arm^{@}\text{-}based$ 32-bit MCUs |

| [3]                 | RM0432      | STM32L4+ series Arm <sup>®</sup> -based 32-bit MCUs                                           |

| [4]                 | RM0487      | STM32U3 series Arm <sup>®</sup> -based 32-bit MCUs                                            |

| [5]                 | AN2606      | STM32 microcontroller system memory boot mode                                                 |

| [6]                 | PM0264      | STM32 Cortex <sup>®</sup> -M33 MCUs programming manual                                        |

| [7]                 | PM0214      | STM32 Cortex <sup>®</sup> -M4 MCUs and MPUs programming manual                                |

# 2 STM32U3 series overview

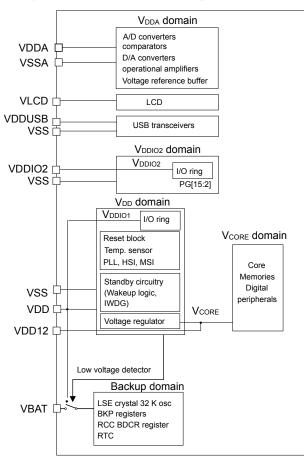

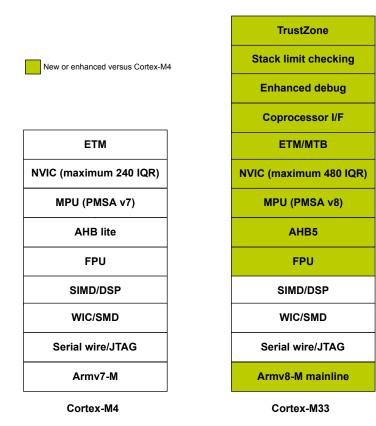

Compared to the STM32L4 and STM32L4+ series, the STM32U3 series use a newer technology to achieve excellence in ultra-low power, increased security, enhanced efficiency, performance, and memory size, such as:

- Improved battery life owing to subtreshold voltage technology: active consumption down to 10 µA/MHz.

- Up to 1 Mbyte of flash memory.

- Up to 256 Kbytes of RAM.

- Ultra-low-power Arm<sup>®</sup>Cortex<sup>®</sup>-M33 32-bit core, with TrustZone<sup>®</sup> for Armv8-M.

- ST instruction cache (ICACHE), supporting both internal and external memories.

- Crypton peripheral embedding AES, SAES, PKA, HASH, and RNG peripherals and accelerators for increased security on the crypto line (available only on STM32U385).

# 2.1 Main features

The STM32U3 MCUs include a similar set of peripherals to the STM32L4 and STM32L4+ MCUs, but with advanced features, such as the ones listed below:

### Security

- Arm<sup>®</sup> TrustZone<sup>®</sup> and securable I/Os, memories, and peripherals.

- RDP and password-protected debug, secure firmware upgrade support, secure firmware installation, secure hide protection, and secure hide protection extension.

- Up to eight configurable SAU regions.

- Additional encryption accelerator engine (available only on STM32U385xx devices):

- HASH hardware accelerator.

- Two advanced encryption hardware accelerators (AES), including one with SCA resistance.

- Public key accelerator (PKA), SCA-resistant.

- Coupling and chaining bridge (CCB).

### Power consumption

- Embedded regulator (LDO).

- SMPS step-down converter:

- Regulators are placed in parallel, making it possible to switch from one to another on the fly.

- Both regulators can provide two different voltages (voltage scaling) and can operate in Stop modes.

- Optimized RTC consumption.

#### Performance

- Frequency up to 96 MHz.

- ICACHE for internal and external memories.

- New peripherals

- Two ultra-low-power 12-bit ADCs with hardware oversampling up to 22 bits.

- Audio digital filter.

- Octo-SPI interface (OCTOSPI).

- Two improved inter-integrated circuits (I3C).

Note: This document only compares the differences between common features in the STM32L4 and STM32L4+ MCUs and the STM32U3 MCUs. The new features of the STM32U3 series, mainly linked to TrustZone<sup>®</sup> support, are not covered. The detailed list of available features and packages for each product is available in the respective product datasheet.

# 2.2 System architecture

The STM32U3 series embed high-speed memories (up to 1 Mbyte of flash memory and up to 256 Kbytes of RAM), an Octo-SPI interface (on packages with less than 64 pins, only quad mode is supported), and an extensive range of enhanced I/Os and peripherals connected to a 32-bit multi-AHB bus matrix, three AHB buses, and three APB buses.

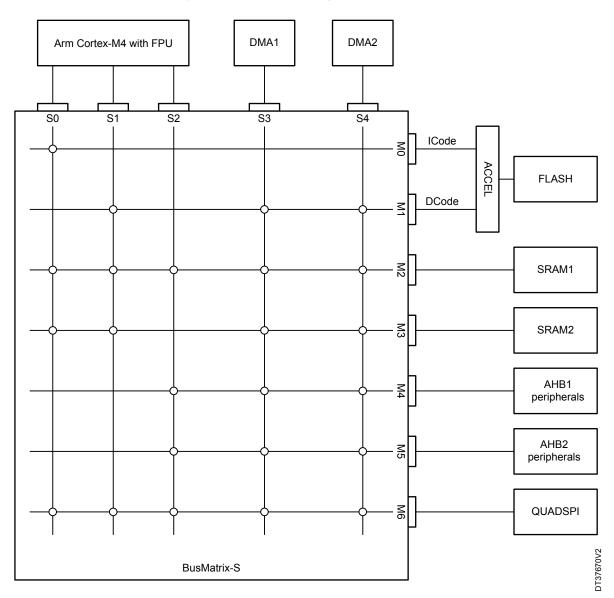

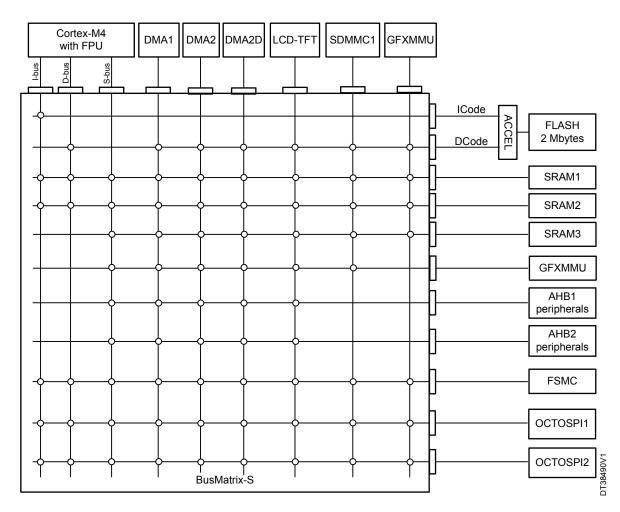

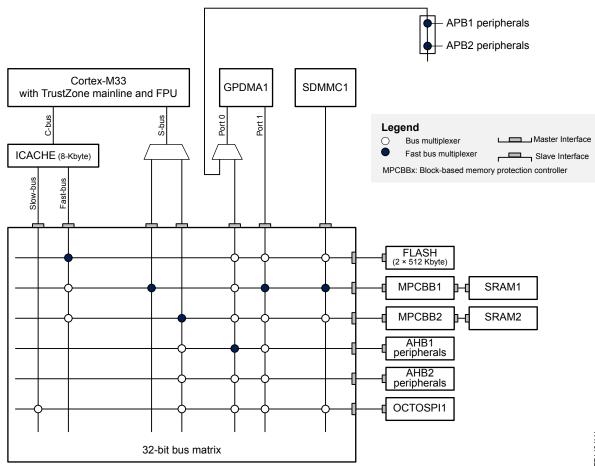

The following table illustrates the bus matrix differences between STM32L4, STM32L4+, and STM32U3 devices.

## Table 2. Bus matrix on STM32L4, STM32L4+, and STM32U3 series

| Bus type                     | STM32L4                                                                                                                                                 | STM32L4+                                                                                                                                                                      | STM32U3                                                                                                                              |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| AHB bus<br>matrix<br>masters | 5 masters:<br>CPU, AHB system,<br>DCode, ICode, DMA1<br>and DMA2 <sup>(1)</sup> .                                                                       | Up to 9 masters:<br>CPU, AHB system, DCode, ICode, DMA1 and<br>DMA2, DMA2D, LCD-TFT controller DMA,<br>SDMMC1, SDMMC2, GFXMMU <sup>(2)</sup> .                                | Up to 7 masters:<br>Fast C-bus, slow C-bus, CPU S-bus for SRAM1,<br>CPU S-bus for other memories <sup>(3)</sup> , GPDMA1,<br>SDMMC1. |

| AHB bus<br>matrix<br>slaves  | Up to 8 slaves:<br>internal flash memory<br>(on ICode and DCode<br>bus), SRAM1, SRAM2,<br>AHB1 (including APB1<br>and APB2), AHB2,<br>FMC, and QUADSPI. | Up to 11 slaves:<br>internal flash memory (on ICode and DCode bus),<br>SRAM1, SRAM2, SRAM3, GFXMMU, AHB1<br>(including APB1 and APB2), AHB2, OCTOSPI1,<br>OCTOSPI2, and FSMC. | Up to 6 slaves:<br>Internal flash memory, SRAM1, SRAM2, AHB1,<br>AHB2, peripherals (including APB1, APB2, and<br>APB3), OCTOSPI1.    |

1. Up to six masters with DMA2D only for STM32L496/4A6xx.

2. SDMMC2 and GFXMMU only available for STM32L4P5/L4Q5xx.

3. Two S-bus masters connected to two internal SRAMs without latency.

The bus matrix provides access from a master to a slave, enabling concurrent access and efficient operation even when several high-speed peripherals work simultaneously.

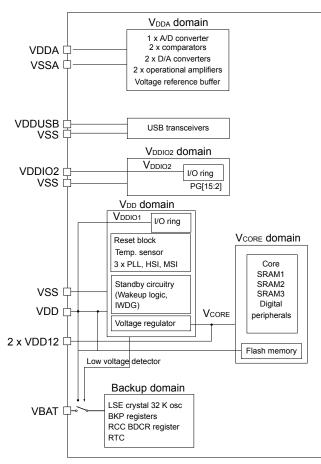

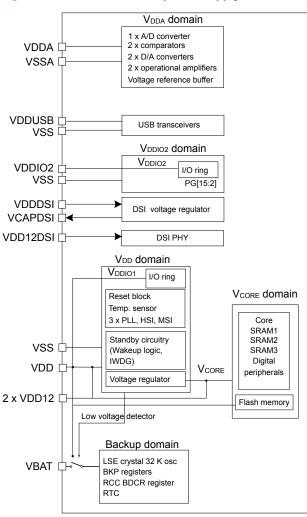

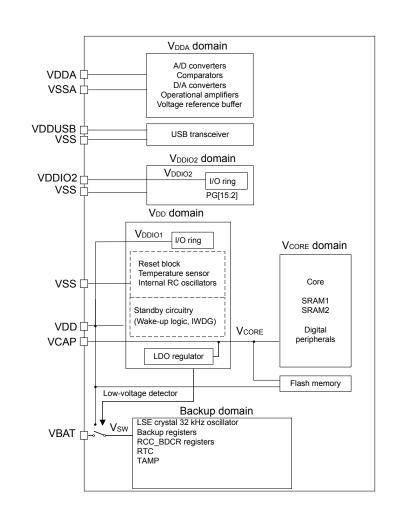

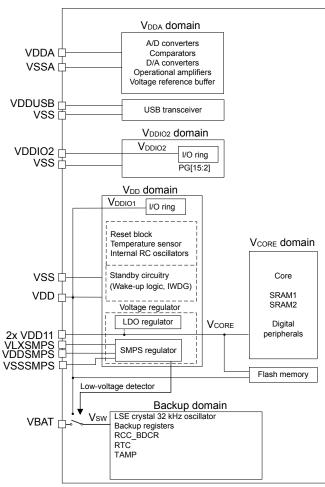

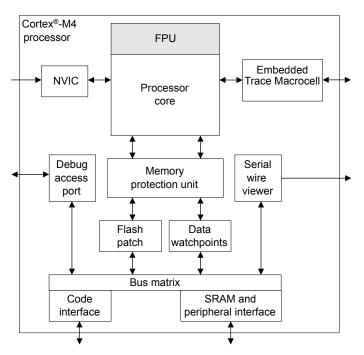

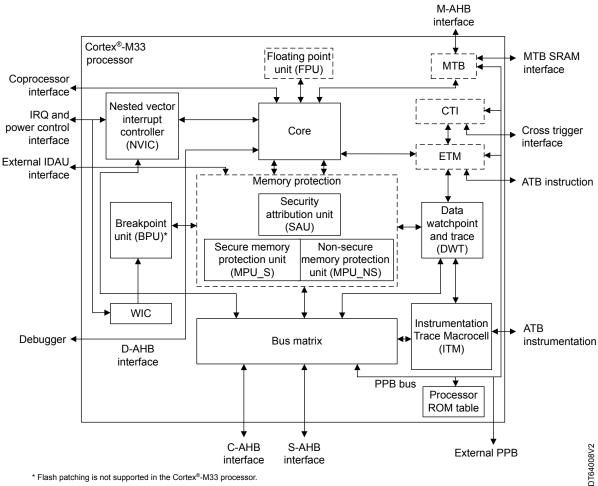

The system architectures of STM32L4, STM32L4+, and STM32U375/385 are shown in the figures below.

# Figure 1. STM32L4 series system architecture

# Figure 2. STM32L4+ series system architecture

# 2.3 Memory availability

The table below summarizes the memory availability for STM32L4, STM32L4+, and STM32U3 MCUs.

# Table 3. Memory availability for STM32L4, STM32L4+, and STM32U3 MCUs

| Product         | Flash memory          |      | RAM size (Kbytes) |             |            | Comment                  |

|-----------------|-----------------------|------|-------------------|-------------|------------|--------------------------|

|                 | Size                  | Bank | SRAM1             | SRAM2       | SRAM3      | Comment                  |

| STM32U375       | 512 Kbytes to 1 Mbyte | Dual | 192 Kbytes        | 64 Khyton   |            | Without hardware crypto. |

| STM32U385       | 1 Mbyte               | Duai | 192 NUYLES        | s 64 Kbytes | -          | With hardware crypto.    |

| STM32L41x/42x   | 128 Kbytes            | -    | 32 Kbytes         | 8 Kbytes    | -          | -                        |

| STM32L43x/44x   | 256 Kbytes            | -    | 48 Kbytes         | 16 Kbytes   | -          | -                        |

| STM32L45x/46x   | 512 Kbytes            | -    | 128 Kbytes        | 32 Kbytes   | -          | -                        |

| STM32L47x/48x   | 1 Mbyte               | -    | 96 Kbytes         | 32 Kbytes   | -          | -                        |

| STM32L49x/L4Ax  | 1 Mbyte               | -    | 256 Kbytes        | 64 Kbytes   | -          | -                        |

| STM32L4P5x/L4Q5 | 1 Mbyte               | -    | 128 Kbytes        | 64 Kbytes   | 128 Kbytes | -                        |

| STM32L4Rx/L4Sx  | 2 Mbytes              | -    | 192 Kbytes        | 64 Kbytes   | 384 Kbytes | -                        |

# 3 Hardware migration

The STM32U3 MCUs offer packages from 32 to 100 pins, and two pinout versions:

- Without internal SMPS: most packages are compatible with STM32L4 and STM32L4+ MCUs.

- With internal SMPS: brand new packages that are not compatible with STM32L4 and STM32L4+ MCUs. For this pinout version, the SMPS step-down converter and the LDO are embedded in parallel to provide the V<sub>CORE</sub> supply.

For more details on the pinout, refer to the product datasheets.

The table below lists the available packages for STM32U3 MCUs compared to those available on STM32L4 and STM32L4+ MCUs, as well as their compatibility. Only the packages that are available in both series are shown. WLCSPxxx packages, which are not available for the STM32L4 and STM32L4+ MCUs, are not listed.

The table does not list the WLCSPx packages for STM32U3 MCUs, because they are dedicated to individual product lines. Refer to the product datasheets for more information.

### Table 4. Packages on STM32U3 MCUs compared to STM32L4 and STM32L4+ MCUs

X = available, N/A = not available

|                              | STM3              | 32L4 <sup>(1)</sup> | STM32U3          |                                                            |                                                      |  |

|------------------------------|-------------------|---------------------|------------------|------------------------------------------------------------|------------------------------------------------------|--|

| Package<br>(Size in mm x mm) | STM32L4           | STM32L4+            | STM32U375/385    | STM32U375/385<br>without SMPS<br>compared<br>toSTM32L4/L4+ | STM32U375/385 with<br>SMPS compared<br>toSTM32L4/L4+ |  |

| UFQFPN32 (5 x 5)             | X <sup>(2)</sup>  | N/A                 | X <sup>(4)</sup> | Compatible <sup>(5)</sup>                                  | N/A                                                  |  |

| LQFP48 (7 x 7)               | X <sup>(7)</sup>  | X <sup>(3)</sup>    | Х                | Compatible <sup>(6)</sup>                                  |                                                      |  |

| UFQFPN48 (7 x 7)             | X <sup>(7)</sup>  | X <sup>(3)</sup>    | X                | Compatible <sup>(6)</sup>                                  |                                                      |  |

| LQFP64 (10 x 10)             | Х                 | X <sup>(3)</sup>    | Х                | Compatible <sup>(6)</sup>                                  | New pinout/ballout                                   |  |

| UFBGA64 (5 x 5)              | X <sup>(7)</sup>  | N/A                 | Х                | Compatible <sup>(6)</sup>                                  |                                                      |  |

| LQFP100 (14 x 14)            | X <sup>(9)</sup>  | Х                   | Х                | Compatible <sup>(6)</sup>                                  |                                                      |  |

| UFBGA100 (7 x 7)             | X <sup>(10)</sup> | N/A                 | X                | Compatible <sup>(6)</sup>                                  |                                                      |  |

1. For more details about the available packages for STM32L4 and STM32L4+, refer to the product datasheet.

- 2. Available only for STM32L47/48/49/4Axxx.

- 3. Available only for STM32L4Q5xx/4P5xx devices.

- 4. Available only for devices without internal SMPS.

- 5. Compatible, except pin PH3 becomes VCAP; BOOT0 functionality moved to PB7.

- 6. Compatible, except PB11 pin becomes VCAP.

- 7. Not available for STM32L47/48/49/4Axxx devices.

- 8. Available only for STM32L49/4Axxx.

- 9. Not available for STM32L41/42xxx devices.

- 10. Available only for STM32L43/44/45/46xxx devices.

When SMPS is supported, a new, dedicated pinout supporting the SMPS step-down converter is available for the STM32U3 series.

When SMPS is not supported, the STM32U3 series devices are pin-to-pin compatible with the STM32L4 and STM32L4+ series devices, except:

- UFQFPN32 package: PH3-BOOT0 pin on STM32L4 is replaced by VCAP on STM32U3, and PB7 becomes PB7-BOOT0 on STM32U3.

- For other packages, the only incompatibility is in the PB11 pin on STM32L4 and STM32L4+, which is replaced by the VCAP pin on STM32U3.

| Package (size in mm xmm) | Different pin/ball position | STM32L4 and STM32L4+ | STM32U3   |  |

|--------------------------|-----------------------------|----------------------|-----------|--|

| UFQFPN32 (5 x 5)         | 31                          | PH3-BOOT0            | VCAP      |  |

| OFQFFN32(3.3.5)          | 30                          | PB7                  | PB7-BOOT0 |  |

| LQFP48 (7 x 7)           | 22                          |                      |           |  |

| UFQFPN48 (7 x 7)         | 22                          |                      |           |  |

| LQFP64 (10 x 10)         | 30                          | PB11                 | VCAP      |  |

| UFBGA64 (5 x 5)          | H7                          | гон                  | VCAP      |  |

| LQFP100 (14 x 14)        | 48                          |                      |           |  |

| UFBGA100 (7 x 7)         | L11                         |                      |           |  |

### Table 5. Different pins and their positions

# 4 Boot mode compatibility

# 4.1 Boot mode selection

For STM32U3, the BOOT0 input pin may come from the PH3-BOOT0 pin or from an option bit, depending on the value of a user option bit to free the GPIO pad if necessary.

Table 6 and Table 7 below present the STM32U3 boot modes, when TrustZone<sup>®</sup> is disabled (Table 6) or enabled (Table 7).

| NBOOT0<br>flash_OPTR[27] | BOOT0<br>pin PH3 | NSWBOOT0<br>flash_<br>OPTR[26] | Boot address option-<br>byte selection | Boot area                                                  | STMicroelectronics programmed default value |

|--------------------------|------------------|--------------------------------|----------------------------------------|------------------------------------------------------------|---------------------------------------------|

| -                        | 0                | 1                              | NSBOOTADD0[24:0]                       | Boot address defined by user option bytes NSBOOTADD0[24:0] | Flash memory: 0x0800 0000                   |

| -                        | 1                | 1                              | NSBOOTADD1[24:0]                       | Boot address defined by user option bytes NSBOOTADD1[24:0] | Bootloader: 0x0BF8 F000                     |

| 1                        | -                | 0                              | NSBOOTADD0[24:0]                       | Boot address defined by user option bytes NSBOOTADD0[24:0] | Flash memory: 0x0800 0000                   |

| 0                        | -                | 0                              | NSBOOTADD1[24:0]                       | Boot address defined by user option bytes NSBOOTADD1[24:0] | Bootloader: 0x0BF8 F000                     |

## Table 6. Boot modes for STM32U3 when TrustZone<sup>®</sup> is disabled (TZEN = 0)

# Table 7. Boot modes for STM32U3 when TrustZone<sup>®</sup> is enabled (TZEN = 1)

| воот_Lоск | NBOOT0<br>flash_OPTR[27] | BOOT0<br>pin<br>PH3 | NSWBOOT0<br>flash_OPTR[26] | RSS<br>command | Boot address<br>option-byte<br>selection | Boot area                                                                   | STMicroelectronics<br>programmed<br>default value |

|-----------|--------------------------|---------------------|----------------------------|----------------|------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

|           | -                        | 0                   | 1                          | 0              | SECBOOTADD0<br>[24:0]                    | Secure boot address<br>defined by user option<br>bytes<br>SECBOOTADD0[24:0] | Flash memory:<br>0x0C00 0000                      |

|           | -                        | 1                   | 1                          | 0              | N/A                                      | RSS                                                                         | RSS: 0x0FF80000                                   |

| 0         | 1                        | -                   | 0                          | 0              | SECBOOTADD0<br>[24:0]                    | Secure boot address<br>defined by user option<br>bytes<br>SECBOOTADD0[24:0] | Flash memory:<br>0x0C00 0000                      |

|           | 0                        | -                   | 0                          | 0              | N/A                                      | RSS                                                                         | RSS: 0x0FF80000                                   |

|           | -                        | -                   | -                          | ≠ 0            | N/A                                      | RSS                                                                         | RSS: 0x0FF80000                                   |

| 1         | -                        | -                   | -                          | -              | SECBOOTADD0<br>[24:0]                    | Secure boot address<br>defined by user option<br>bytes<br>SECBOOTADD0[24:0] | Flash memory:<br>0x0C00 0000                      |

On STM32L4+ and STM32L41/42/43/44/45/46/49/4Axxx, the boot mode is selected with the nBOOT1 option bit and the BOOT0 pin, or the nBOOT0 option bit, depending on the value of the nSWBOOT0 option bit in the flash\_OPTR register (see Table 8 below).

| nBOOT1 flash_<br>OPTR[23] | nBOOT0<br>flash_<br>OPTR [27] | BOOT0 pin<br>PH3 | nSWBOOT0<br>flash_<br>OPTR [26] | Main flash<br>empty <sup>(1)</sup> | Boot memory space alias                 |

|---------------------------|-------------------------------|------------------|---------------------------------|------------------------------------|-----------------------------------------|

| X                         | Х                             | 0                | 1                               | 0                                  | Main flash memory selected as boot area |

| X                         | Х                             | 0                | 1                               | 1                                  | System memory selected as boot area     |

| X                         | 1                             | Х                | 0                               | Х                                  | Main flash memory selected as boot area |

| 0                         | Х                             | 1                | 1                               | Х                                  | Embedded SRAM1 selected as boot area    |

| 0                         | 0                             | Х                | 0                               | Х                                  | Embedded SRAM1 selected as boot area    |

| 1                         | Х                             | 1                | 1                               | Х                                  | System memory selected as boot area     |

| 1                         | 0                             | Х                | 0                               | Х                                  | System memory selected as boot area     |

### Table 8. Boot modes for STM32L4+ and STM32L41/42/43/44/45/46/49/4Axxx

1. For STM32L41/42/43/44/45/46xxx, a flash memory empty check mechanism is implemented to force the boot from system flash memory, if the first flash memory location is not programmed (0xFFF FFFF), and if the boot selection was configured to boot from the main flash memory.

On the other STM32L4 devices (STM32L47/48xxx), the boot mode is selected with one BOOT0 pin and the nBOOT1 option bit located in the user option bytes, at the memory address 0x1FFF 7800 (see Table 9 below).

### Table 9. Boot modes for STM32L47/48xxx

| Selected boot area  | BOOT1            | BOOT0 |

|---------------------|------------------|-------|

| Main flash memory   | X <sup>(1)</sup> | 0     |

| System flash memory | 0                | 1     |

| Embedded SRAM1      | 1                | 1     |

1. X = equivalent to 0 or 1.

# 4.2 Embedded bootloader

The embedded bootloader is located in the system memory and programmed by STMicroelectronics during production. It allows the flash memory to be reprogrammed, using the serial interfaces listed in the table below.

#### Table 10. Bootloader interface on STM32L4, STM32L4+, and STM32U3 MCUs

| Peripheral | Pin              | STM32L4 and STM32L4+ | STM32U3 |

|------------|------------------|----------------------|---------|

| DFU        | USB_DM (PA11)    | Х                    | Х       |

| DFU        | USB_DP (PA12)    | Х                    | X       |

| USART1     | USART1_TX (PA9)  | Х                    | X       |

| USARTI     | USART1_RX (PA10) | Х                    | Х       |

| USART2     | USART2_TX (PA2)  | Х                    | N/A     |

| USARTZ     | USART2_RX (PA3)  | Х                    | N/A     |

| USART3     | USART3_TX (PC10) | Х                    | Х       |

| USARIS     | USART3_RX (PC11) | Х                    | X       |

| I2C1       | I2C1_SCL (PB6)   | Х                    | X       |

| 1201       | I2C1_SDA (PB7)   | Х                    | X       |

| 12C2       | I2C2_SCL (PB10)  | Х                    | X       |

# AN6051 Boot mode compatibility

| Peripheral | Pin              | STM32L4 and STM32L4+ | STM32U3                                        |  |

|------------|------------------|----------------------|------------------------------------------------|--|

| 12C2       | I2C2_SDA (PB11)  | Х                    | Х                                              |  |

| I2C3       | I2C3_SCL (PC0)   | Х                    | X                                              |  |

| 1263       | I2C3_SDA (PC1)   | Х                    | X                                              |  |

| 100.4      | I2C4_SCL (PD12)  | X <sup>(1)</sup>     | N/A                                            |  |

| I2C4       | I2C4_SDA (PD13)  | X <sup>(1)</sup>     | N/A                                            |  |

| 10.04      | I3C1_SCL (PB13)  | N/A                  | X                                              |  |

| I3C1       | I3C1_SDA (PA1)   | N/A                  | X                                              |  |

|            | SPI1_NSS (PA4)   | Х                    | X<br>PG5 instead of PA4 for WLCSP68-G packages |  |

| SPI1       | SPI1_SCK (PA5)   | Х                    | X<br>PG2 instead of PA5 for WLCSP68-G packages |  |

| 5611       | SPI1_MISO (PA6)  | Х                    | X<br>PG3 instead of PA6 for WLCSP68-G packages |  |

|            | SPI1_MOSI (PA7)  | Х                    | X<br>PG4 instead of PA7 for WLCSP68-G packages |  |

|            | SPI2_NSS (PB12)  | Х                    | PD0                                            |  |

| SPI2       | SPI2_SCK (PB13)  | Х                    | PD1                                            |  |

| 5812       | SPI2_MISO (PB14) | Х                    | PD3                                            |  |

|            | SPI2_MOSI (PB15) | Х                    | PD4                                            |  |

|            | SPI3_NSS (PA15)  | N/A                  | X                                              |  |

| SPI3       | SPI3_SCK (PB3)   | N/A                  | X                                              |  |

| 5813       | SPI3_MISO (PB4)  | N/A                  | X                                              |  |

|            | SPI3_MOSI (PB5)  | N/A                  | X                                              |  |

| CANI       | CAN1_RX (PB8)    | X <sup>(2)</sup>     | X <sup>(3)</sup>                               |  |

| CAN1       | CAN1_TX (PB9)    | X <sup>(2)</sup>     | X <sup>(3)</sup>                               |  |

| 0.4.1/0    | CAN2_RX (PB5)    | X <sup>(4)</sup>     | N/A                                            |  |

| CAN2       | CAN2_TX (PB6)    | X <sup>(4)</sup>     | N/A                                            |  |

|            |                  |                      |                                                |  |

1. Available only for STM32L45/46/49/4Axxx.

2. Not available for STM32L41/42xxx.

3. FDCAN1 is available for STM32U3 series.

4. Available only for STM32L49/4Axxx.

For more details on the bootloader, refer to the referenced document [5].

# 5 Peripheral migration

# 5.1 STM32 products cross-compatibility

STM32 microcontrollers embed a set of peripherals that can be classified in the following groups:

- **Group1**: peripherals common to all products by definition. These peripherals are identical, so they have the same structure, registers, and control bits. There is no need to perform any firmware changes to keep the same functionality at application level after migration. The behavior and features remain the same.

- **Group2**: peripherals shared by all products but with minor differences only. In general, they support new features.

The migration from one product to another is very easy and does not require any significant new development efforts.

• **Group3**: peripherals that have considerable changes from one product to another (a new architecture or new features, for example).

For this group of peripherals, the migration requires new developments at application level.

Each GPIO or peripheral, DMA channel, clock configuration register, ICACHE, or small part of flash memory or SRAM can be configured as trusted or untrusted on STM32U3 MCUs.

The following table summarizes the available peripherals on the STM32L4, STM32L4+, and STM32U3 MCUs, as well as their compatibility.

## Table 11. STM32 peripheral compatibility between STM32L4, STM32L4+, and STM32U3 MCUs

| Devi                 |                         | STM32L4                                                |                                                                                  | STM32U3                                                                              |  |

|----------------------|-------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Peripheral           |                         | STM32L4                                                | STM32L4+                                                                         | STM32U375/385                                                                        |  |

| Core                 |                         | Cortex <sup>®</sup> -M4                                |                                                                                  | Cortex <sup>®</sup> -M33                                                             |  |

| Maximum CPU freq     | uency                   | 80 MHz                                                 | 120 MHz                                                                          | 96 MHz                                                                               |  |

| ICACHE               |                         | N/A                                                    | N/A                                                                              |                                                                                      |  |

|                      | Power supply            |                                                        | 1.71 to 3.6 V                                                                    | '                                                                                    |  |

|                      | LDO                     | Available                                              | e for all products/pacl                                                          | kages                                                                                |  |

| PWR/regulators       | LDO + internal<br>DC-DC | N/A                                                    | STM32U3xxxxQ products + DC-<br>DC/LDO on-the-fly selection.                      |                                                                                      |  |

|                      | LDO + external<br>DC-DC | Available through VDD12                                | N/A (no regulator bypass option).                                                |                                                                                      |  |

| Flash memory         | Size                    | Up to 1 Mbyte Up to 2 Mbytes                           |                                                                                  | Up to 1 Mbyte + advanced<br>features (such as secure hide<br>protection).            |  |

|                      | Bank                    | Dual bank                                              | Dual bank                                                                        |                                                                                      |  |

|                      | SRAM1                   | Up to 256 Kbytes                                       | 192 Kbytes                                                                       | 192 Kbytes                                                                           |  |

| SRAMs                | SRAM2                   | Up to 64 Kbytes                                        | 64 Kbytes                                                                        | 64 Kbytes with optional hardware parity                                              |  |

|                      | SRAM3                   | N/A                                                    | 384 Kbytes                                                                       | N/A                                                                                  |  |

| DMA (not compatible) |                         | DMA request line is connected directly to peripherals. | DMA request line<br>is connected to<br>peripherals<br>through DMAMUX<br>+ DMA2D. | GPDMA (12 channels) +<br>advanced features (such as DMA<br>peripheral control mode). |  |

|                                                 |                          | STM32L4                                                                                                                                             |                                     | STM32U3                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Peripheral                                      |                          | STM32L4                                                                                                                                             | STM32L4+                            | STM32U375/385                                                                                                                                                                                                                                                                                                                                                                             |  |

| GTZC (global TrustZone <sup>®</sup> controller) |                          | N/A                                                                                                                                                 |                                     | <ul> <li>3 independent 32-bit AHB interface<br/>for TZSC, TZIC, and MPCBB.</li> <li>TZIC accessible only with secure<br/>transactions.</li> <li>Secure and nonsecure access<br/>supported for the privileged and<br/>unprivileged parts of TZSC.</li> <li>Set of registers to define product<br/>security settings.</li> <li>Privilege mode extended to internal<br/>memories.</li> </ul> |  |

| Anti-tamper detectic                            | n                        | Up to 3 tamper pins                                                                                                                                 |                                     | Up to 5 tampers pins and 9 internal<br>tamper events + new advanced<br>features (such as GTZC and<br>secure peripherals support).                                                                                                                                                                                                                                                         |  |

| CRC                                             |                          | 1                                                                                                                                                   |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                         |  |

| FSMC (external men<br>static memory LCD)        |                          | 1                                                                                                                                                   |                                     | N/A                                                                                                                                                                                                                                                                                                                                                                                       |  |

| High-speed low-volt                             | age mode (HSLV)          | N/A                                                                                                                                                 |                                     | Some I/Os have the capability to increase their speed at low voltage by configuring them in HSLV mode.                                                                                                                                                                                                                                                                                    |  |

|                                                 | Advanced control         | Up to 2 (16-bit)                                                                                                                                    | 2 (16-bit)                          | 1 (16-bit)                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                 | General purpose          | Up to 5 (16-bit) + up to 2 (32-bit)                                                                                                                 | 5 (16-bit) + 2 (32-<br>bit)         | 3 (16-bit) + 3 (32-bit)                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                 | Basic                    | Up to 2 (16-bit)                                                                                                                                    | 2 (16-bit)                          | 2 (16-bit)                                                                                                                                                                                                                                                                                                                                                                                |  |

| Timers                                          | Low-power                | 2 (16-bit)                                                                                                                                          |                                     | 4 (16-bit) + autonomous mode.                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                 | Watchdogs                | 1 IWDG and 1 WWDG                                                                                                                                   |                                     | 1 IWDG and 1 WWDG + early interrupt feature.                                                                                                                                                                                                                                                                                                                                              |  |

|                                                 | RTC                      | Yes                                                                                                                                                 |                                     | Yes + advanced features<br>(TrustZone support).                                                                                                                                                                                                                                                                                                                                           |  |

|                                                 | SysTick                  | 1                                                                                                                                                   |                                     | 2                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                 | SPI                      | Up to 3                                                                                                                                             | 3                                   | 3 + advanced features (such as<br>more configurability) +<br>autonomous mode registers not<br>compatible.                                                                                                                                                                                                                                                                                 |  |

|                                                 | I2C                      | Up to 4                                                                                                                                             | 4                                   | 3                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                 | I3C                      | N/A                                                                                                                                                 |                                     | 2 + autonomous mode.                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                 | USART/UART               | Up to 3/2                                                                                                                                           | 3/2                                 | 2/2 + autonomous mode                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                 | LPUART                   | 1                                                                                                                                                   |                                     | 1 + new features (such as input capture) + autonomous mode                                                                                                                                                                                                                                                                                                                                |  |

| Communication interfaces                        | SAI (audio<br>interface) | 2                                                                                                                                                   |                                     | 1                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                 | CAN                      | Up to 2 bxCAN                                                                                                                                       | 1 bxCAN                             | 1 FDCAN                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                 | USB                      | STM32L4x1 devices: no USB.<br>For other STM32L41/42/43/45/46xxx<br>devices: USB FS device.<br>For otherSTM32L47/48/49/4Axxx<br>devices: USB FS OTG. | USB FS OTG with<br>clock recovery.  | USB FS host/device with clock recovery.                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                 | SDMMC                    | <b>1</b> <sup>(1)</sup>                                                                                                                             |                                     | 1 + compliance with newer<br>SD/MMC specifications.                                                                                                                                                                                                                                                                                                                                       |  |

|                                                 | Camera<br>interfaces     | 1 DCMI <sup>(2)</sup>                                                                                                                               | 1 DCMI and 1<br>PSSI <sup>(3)</sup> | N/A                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                          | la mal                                   | STM32L4                                 |                             | STM32U3                                                                                 |

|--------------------------|------------------------------------------|-----------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------|

| Peripheral -             |                                          | STM32L4                                 | STM32L4+                    | STM32U375/385                                                                           |

| Communication interfaces | OCTOSPI                                  | N/A (Quad-SPI only)                     | 2 + Octo-SPI I/O<br>manager | 1                                                                                       |

|                          | ADC                                      | Up to 3 ADCs (12-bit)                   | 2 ADCs (12-bit)             | 2 ADCs (12-bit) + new features (such as better oversampling).                           |

|                          | DAC                                      | Up to 2 converters (12-bit)             | 2 converters (12-<br>bit)   | 2 converters (12-bit)                                                                   |

| Analog peripherals       | COMP                                     | Up to 2                                 | 2                           | 2 (registers not compatible)                                                            |

|                          | OPAMP                                    | Up to 2                                 | 2                           | 2 + new slew rate configuration.                                                        |

|                          | Voltage reference buffer                 | Yes<br>2 voltage levels                 |                             | Yes<br>4 voltage levels                                                                 |

|                          | AES                                      | Yes <sup>(4)</sup>                      | Yes <sup>(5)</sup>          | Yes <sup>(6)</sup>                                                                      |

|                          | SAES (secure<br>AES)                     | No                                      |                             | Yes <sup>(6)</sup>                                                                      |

|                          | PKA (private key accelerator)            | No                                      | Yes <sup>(7)</sup>          | Yes <sup>(6)</sup> + advanced features (such<br>as SCA resistance).                     |

| Secure peripherals       | HASH                                     | Yes <sup>(8)</sup>                      | Yes <sup>(9)</sup>          | Yes + advanced features (such as support for SHA2-384/512).                             |

|                          | RNG                                      | Yes                                     | Yes                         | Yes + entropy enhancement +<br>advanced features (such as<br>connection with SAES/PKA). |

|                          | CCB (coupling<br>and chaining<br>bridge) | N/A                                     |                             | Yes                                                                                     |

| Signal-processing        | Digital filters                          | Up to 4 filters (DFSDM) <sup>(10)</sup> | 4 filters (DFSDM)           | 1 ADF (1 audio digital filter)                                                          |

|                          | TSC (touch sensing control)              | Up to 24 channels <sup>(11)</sup>       |                             | Up to 21 channels                                                                       |

| coprocessors             | LTDC                                     | N/A                                     | 1                           | N/A                                                                                     |

|                          | DSI                                      | N/A                                     | 1                           | N/A                                                                                     |

1. Not available on STM32L41x/42x/432/442xx devices.

2. Available only for STM32L49/4Axxx devices.

3. PSSI available only for STM32L4P/4Qxxx devices.

4. Available only for STM32L42/44/46/48/4Axxx devices.

5. Available only for STM32L4S/4Qxxx devices.

6. Available only for STM32U385xx devices.

7. Available only for STM32L4Qxxx devices.

8. Available only for STM32L4Axxx devices.

9. Not available for STM32L4Rxxx devices.

10. Not available for STM32L41/42/43/44xxx devices.

11. Depending on the line: for instance, only 12 channels available for STM32L41/42xxx devices.

# 5.2 Memory mapping

As shown in the table below, the peripheral address mapping has been changed in the STM32U3 MCUs, compared to the STM32L4, STM32L4+ MCUs. The secure boundary address is not disclosed in this table, as they cannot be compared to the STM32L4/STM32L4+ products. For further information, refer to the product reference manual.

### Table 12. Peripheral address mapping of STM32L4, STM32L4+, and STM32U3 MCUs

| Peripheral                 | STM32L4/STM32L4+                                                                                                              | STM32U3                    |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Peripheral                 | Boundary address <sup>(1)</sup>                                                                                               | Nonsecure boundary address |

| HASH                       | 0x5006 0400 - 0x5006 07FF                                                                                                     | 0x420C 0400 - 0x420C 07FF  |

| AES                        | 0x5006 0000 - 0x5006 03FF                                                                                                     | 0x420C 0000 - 0x420C 03FF  |

| DCMI                       | 0x5005 0000 - 0x5005 03FF                                                                                                     | N/A                        |

| GPIOI                      | 0x4800 2000 - 0x4800 23FF                                                                                                     | N/A                        |

| OCTOSPIM                   | 0x5006 1C00 - 0x5006 1FFF                                                                                                     | N/A                        |

| DMA2D                      | 0x4002 B000 - 0x4002 BBFF                                                                                                     | N/A                        |

| GFXMMU                     | 0x4002 C000 - 0x4002 EFFF <sup>(2)</sup>                                                                                      | N/A                        |

| DMAMUX1                    | 0x4002 0800 - 0x4002 0BFF                                                                                                     | N/A                        |

| I2C4                       | 0x4000 8400 - 0x4000 87FF                                                                                                     | N/A                        |

| OCTOSPI2                   | 0xA000 1400 - 0xA000 17FF                                                                                                     | N/A                        |

| OCTOSPI1                   | 0xA000 1000 - 0xA000 13FF                                                                                                     | 0x420D 1400 - 0x420D 17FF  |

| FSMC                       | 0xA000 0000 - 0xA000 03FF                                                                                                     | N/A                        |

| DSI                        | 0x4001 6C00 - 0x4001 73FF                                                                                                     | N/A                        |

| LTDC                       | 0x4001 6800 - 0x4001 6BFF                                                                                                     | N/A                        |

| JSB_FS SRAM <sup>(3)</sup> | 0x4000 6C00 - 0x4000 6FFF                                                                                                     | 0x4001 6400 - 0x4001 6BFF  |

| USB_FS <sup>(3)</sup>      | 0x4000 6800 - 0x4000 6BFF                                                                                                     | 0x4001 6000 - 0x4001 63FF  |

| OTG_FS                     | 0x5000 0000 - 0x5003 FFFF                                                                                                     | N/A                        |

| SDMMC1                     | <ul> <li>0x4001 2800 - 0x4001 2BFF (APB2) on<br/>STM32L4</li> <li>0x5006 2400 - 0x5006 27FF (AHB2) on<br/>STM32L4+</li> </ul> | 0x420C 8000 - 0x420C 83FF  |

| SDMMC2                     | 0x5006 2800 - 0x5006 2BFF <sup>(2)</sup>                                                                                      | N/A                        |

| ССВ                        | N/A                                                                                                                           | 0x420C 7C00 - 0x420C 7FFF  |

| РКА                        | 0x5005 E000 - 0x5005 FFFF <sup>(2)</sup>                                                                                      | 0x420C 2000 - 0x420C 3FFF  |

| PSSI                       | 0x5005 0400 - 0x5005 07FF <sup>(2)</sup>                                                                                      | N/A                        |

| RNG                        | 0x5006 0800 - 0x5006 0BFF                                                                                                     | 0x420C 0800 - 0x420C 0BFF  |

| ADC                        | 0x5004 0000 - 0x5004 03FF                                                                                                     | 0x4202 8000 - 0x4202 83FF  |

| GPIOH                      | N/A                                                                                                                           | 0x4202 1C00 - 0x4202 1FFF  |

| GPIOG                      | 0x4800 1800 - 0x4800 1BFF                                                                                                     | 0x4202 1800 - 0x4202 1BFF  |

| GPIOF                      | 0x4800 1400 - 0x4800 17FF                                                                                                     | N/A                        |

| GPIOE                      | 0x4800 1000 - 0x4800 13FF                                                                                                     | 0x4202 1000 - 0x4202 13FF  |

| GPIOD                      | 0x4800 0C00 - 0x4800 0FFF                                                                                                     | 0x4202 0C00 - 0x4202 0FFF  |

| GPIOC                      | 0x4800 0800 - 0x4800 0BFF                                                                                                     | 0x4202 0800 - 0x4202 0BFF  |

| GPIOB                      | 0x4800 0400 - 0x4800 07FF                                                                                                     | 0x4202 0400 - 0x4202 07FF  |

| GPIOA                      | 0x4800 0000 - 0x4800 03FF                                                                                                     | 0x4202 0000 - 0x4202 03FF  |

| Deviate                    | STM32L4/STM32L4+                | STM32U3                    |  |

|----------------------------|---------------------------------|----------------------------|--|

| Peripheral –               | Boundary address <sup>(1)</sup> | Nonsecure boundary address |  |

| GTZC1_TZSC                 |                                 | 0x4003 2400 - 0x4003 27FF  |  |

| GTZC1_TZIC                 |                                 | 0x4003 2800 - 0x4003 2BFF  |  |

| GTZC1_MPCBB1               | N/A                             | 0x4003 2C00 - 0x4003 2FFF  |  |

| GTZC1_MPCBB2               |                                 | 0x4003 3000 - 0x4003 33FF  |  |

| TSC                        | 0x4002 4000 - 0x4002 43FF       | 0x4002 4000 - 0x4002 43FF  |  |

| CRC                        | 0x4002 3000 - 0x4002 33FF       | 0x4002 3000 - 0x4002 33FF  |  |

| Flash registers            | 0x4002 2000 - 0x4002 23FF       | 0x4002 2000 - 0x4002 23FF  |  |

| RCC                        | 0x4002 1000 - 0x4002 13FF       | 0x4003 0C00 - 0x4003 0FFF  |  |

| DMA1                       | 0x4002 0000 - 0x4002 03FF       | N/A                        |  |

| DMA2                       | 0x4002 0400 - 0x4002 07FF       | N/A                        |  |

| GPDMA1                     | N/A                             | 0x4002 0000 - 0x4002 0FFF  |  |

| FIREWALL                   | 0x4001 1C00 - 0x4001 1FFF       | N/A                        |  |

| EXTI                       | 0x4001 0400 - 0x4001 07FF       | 0x4003 2000 - 0x4003 23FF  |  |

| DFSDM1                     | 0x4001 6000 - 0x4001 67FF       | N/A                        |  |

| SAI2                       | 0x4001 5800 - 0x4001 5BFF       | N/A                        |  |

| SAI1                       | 0x4001 5400 - 0x4001 57FF       | 0x4001 5400 - 0x4001 57FF  |  |

| TIM17                      | 0x4001 4800 - 0x4001 4BFF       | 0x4001 4800 - 0x4001 4BFF  |  |

| TIM16                      | 0x4001 4400 - 0x4001 47FF       | 0x4001 4400 - 0x4001 47FF  |  |

| TIM15                      | 0x4001 4000 - 0x4001 43FF       | 0x4001 4000 - 0x4001 43FF  |  |

| USART1                     | 0x4001 3800 - 0x4001 3BFF       | 0x4001 3800 - 0x4001 3BFF  |  |

| TIM8                       | 0x4001 3400 - 0x4001 37FF       | N/A                        |  |

| SPI1                       | 0x4001 3000 - 0x4001 33FF       | 0x4001 3000 - 0x4001 33FF  |  |

| TIM1                       | 0x4001 2C00 - 0x4001 2FFF       | 0x4001 2C00 - 0x4001 2FFF  |  |

| COMP                       | 0x4001 0200 - 0x4001 03FF       | 0x4004 5400 - 0x4004 57FF  |  |

| VREFBUF                    | 0x4001 0030 - 0x4001 01FF       | 0x4000 7400 - 0x4000 77FF  |  |

| SYSCFG                     | 0x4001 0000 - 0x4001 002F       | 0x4004 0400 - 0x4004 07FF  |  |

| FDCAN1 RAM                 |                                 | 0x4000 AC00 - 0x4000 AFFF  |  |

| LPTIM4                     | N/A                             | 0x4004 4C00 - 0x4004 4FFF  |  |

| LPTIM3                     |                                 | 0x4004 4800 - 0x4004 4BFF  |  |

| CAN1/FDCAN1 <sup>(4)</sup> | 0x4000 6400 - 0x4000 67FF       | 0x4000 A400 - 0x4000 A7FF  |  |

| LPTIM2                     | 0x4000 9400 - 0x4000 97FF       | 0x4000 9400 - 0x4000 97FF  |  |

| LPUART1                    | 0x4000 8000 - 0x4000 83FF       | 0x4004 2400 - 0x4004 27FF  |  |

| LPTIM1                     | 0x4000 7C00 - 0x4000 7FFF       | 0x4004 4400 - 0x4004 47FF  |  |

| OPAMP                      | 0x4000 7800 - 0x4000 7BFF       | 0x4000 7000 - 0x4000 73FF  |  |

| DAC <sup>(5)</sup>         | 0x4000 7400 - 0x4000 77FF       | 0x4202 8400 - 0x4202 87FF  |  |

| PWR                        | 0x4000 7000 - 0x4000 73FF       | 0x4003 0800 - 0x4003 0BFF  |  |

| CRS                        | 0x4000 6000 - 0x4000 63FF       | 0x4000 6000 - 0x4000 63FF  |  |

| I2C3                       | 0x4000 5C00 - 0x4000 5FFF       | 0x4004 2800 - 0x4004 2BFF  |  |

| I2C2                       | 0x4000 5800 - 0x4000 5BFF       | 0x4000 5800 - 0x4000 5BFF  |  |

| I2C1                       | 0x4000 5400 - 0x4000 57FF       | 0x4000 5400 - 0x4000 57FF  |  |

| Deviahevel                              | STM32L4/STM32L4+                         | STM32U3<br>Nonsecure boundary address |  |

|-----------------------------------------|------------------------------------------|---------------------------------------|--|

| Peripheral —                            | Boundary address <sup>(1)</sup>          |                                       |  |

| UART5                                   | 0x4000 5000 - 0x4000 53FF                | 0x4000 5000 - 0x4000 53FF             |  |

| UART4                                   | 0x4000 4C00 - 0x4000 4FFF                | 0x4000 4C00 - 0x4000 4FFF             |  |

| USART3                                  | 0x4000 4800 - 0x4000 4BFF                | 0x4000 4800 - 0x4000 4BFF             |  |

| USART2                                  | 0x4000 4400 - 0x4000 47FF                | N/A                                   |  |

| SPI3                                    | 0x4000 3C00 - 0x4000 3FFF                | 0x4000 2000 - 0x4000 23FF             |  |

| SPI2                                    | 0x4000 3800 - 0x4000 3BFF                | 0x4000 3800 - 0x4000 3BFF             |  |

| TAMPER and BKP registers <sup>(6)</sup> | 0x4000 3400 - 0x4000 37FF <sup>(7)</sup> | 0x4000 7C00 - 0x4000 7FFF             |  |

| IWDG                                    | 0x4000 3000 - 0x4000 33FF                | 0x4000 3000 - 0x4000 33FF             |  |

| WWDG                                    | 0x4000 2C00 - 0x4000 2FFF                | 0x4000 2C00 - 0x4000 2FFF             |  |

| RTC                                     | 0x4000 2800 - 0x4000 2BFF                | 0x4000 7800 - 0x4000 7BFF             |  |

| TIM7                                    | 0x4000 1400 - 0x4000 17FF                | 0x4000 1400 - 0x4000 17FF             |  |

| TIM6                                    | 0x4000 1000 - 0x4000 13FF                | 0x4000 1000 - 0x4000 13FF             |  |

| TIM5                                    | 0x4000 0C00 - 0x4000 0FFF                | N/A                                   |  |

| TIM4                                    | 0x4000 0800 - 0x4000 0BFF                | 0x4000 0800 - 0x4000 0BFF             |  |

| TIM3                                    | 0x4000 0400 - 0x4000 07FF                | 0x4000 0400 - 0x4000 07FF             |  |

| TIM2                                    | 0x4000 0000 - 0x4000 03FF                | 0x4000 0000 - 0x4000 03FF             |  |

| ADF1                                    |                                          | 0x4003 4000 - 0x4003 4FFF             |  |

| DLYBOS1                                 |                                          | 0x420C F400 - 0x420C F3FF             |  |

| DLYBSD1                                 | N/A                                      | 0x420C 8400 - 0x420C 87FF             |  |

| SAES                                    | N/A                                      | 0x420C 0C00 - 0x420C 0FFF             |  |

| ICACHE                                  |                                          | 0x4003 0400 - 0x4003 07FF             |  |

| RAMCFG                                  |                                          | 0x4002 6000 - 0x4002 6FFF             |  |

1. If no boundary address, it means the peripheral is not available on all STM32L4/STM32L4+ devices.

2. Available only for STM32L4P5/4Q5xx.

3. USB for STM32U375/385.

4. FDCAN1 for STM32U375/385.

5. DAC1 for STM32L4+.

6. TAMP for STM32U375/385.

7. Available only for STM32L4+.

# 6 Migration of system peripherals

# 6.1 System configuration controller (SYSCFG)

# Table 13. SYSCFG features in STM32L4, STM32L4+, and STM32U3 MCUs

| STM32L4 and STM32L4+                                                                                                                                                                                                                                                                                                                                                                     | STM32U3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Remapping memory areas.</li> <li>Managing the external interrupt line connection to the GPIOs.</li> <li>Managing robustness feature.</li> <li>Setting SRAM2 write protection and software erase.</li> <li>Configuring FPU interrupts.</li> <li>Enabling the firewall.</li> <li>Enabling/disabling the I<sup>2</sup>C fast-mode plus driving capability on some I/Os.</li> </ul> | <ul> <li>Managing robustness feature.</li> <li>Configuring FPU interrupts.</li> <li>Enabling/disabling the I<sup>2</sup>C fast-mode plus driving capability on some I/Os and voltage booster for I/O analog switches.</li> <li>Configuring TrustZone<sup>®</sup> security register access.</li> <li>Tracking the PVT conditions to control the current slew-rate and output impedance in I/O buffer through compensations cells on V<sub>DD</sub> and V<sub>DDIO2</sub> GPIOs.</li> <li>Configuration of IRTIM.</li> </ul> |

The remapping of memory areas was replaced by bank swapping, fixed mapping of SRAMs on C-bus (IBus for Cortex<sup>®</sup>-M4 devices), and a possibility to change the vector table offset in the VTOR of the system control block (part of the private peripheral bus). Refer to the referenced documents Introduction and Introduction for more information.

Configuration of SRAMs (including write protection and software erase settings) is ensured by the RAMCFG peripheral.

# 6.2 Embedded flash memory (FLASH)

# Table 14. Flash memory features in STM32L4, STM32L4+, and STM32U3 MCUs

|                                  | Feature              | STM32L4/STM32L4+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | STM32U3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page size<br>Main/program memory |                      | <ul> <li>0x0800 0000 to up to 0x080F FFFF</li> <li>0x0810 0000 to up to 0x081F FFFF (only for STM32L4+)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Bank1: 0x0800 0000 to 0x0807 FFFF</li> <li>Bank2: 0x0808 0000 to 0x080F FFFF</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |