## Migrating between STM32G0 and STM32U0 MCUs

#### Introduction

For designers of STM32 microcontroller applications, being able to replace one microcontroller type with another from the same product family easily is an important asset. Migrating an application to a different microcontroller is often needed when product requirements grow, putting extra demands on memory size, optimizing power consumption, security, or the number of I/Os. The cost reduction objectives may also be an argument to switch to smaller components and shrink the PCB area.

This application note analyzes the steps required to migrate an existing design between the STM32G0 and STM32U0 series. Three aspects must be considered for the migration: hardware, peripherals, and firmware.

STM32U0 and STM32G0 are based on similar platforms and share the same core, architecture, and peripherals, resulting in easy and fast firmware migration. For hardware migration, a redesign of the PCB is necessary.

This document lists the full set of features available for the STM32G0 series and the equivalent features on the STM32U0 series (some products may have fewer features depending on their part number).

To benefit fully from this application note, the user must be familiar with the STM32 microcontroller documentation available on www.st.com, with a particular focus on the documents listed in Reference documents.

### 1 General information

The STM32U0 and STM32G0 MCUs are 32-bit microcontrollers based on the  $Arm^{\circledR}$  Cortex $^{\circledR}$ -M0+ processor.

Note: Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

#### **Reference documents**

- [1] Datasheet STM32G030x6/x8 (DS12991)

[2] Datasheet STM32G050x6/x8 (DS13514)

[3] Datasheet STM32G070CB/KB/RB (DS12766)

- [4] Datasheet STM32G0B0KE/CE/RE/VE (DS13565)

- [5] Datasheet STM32G031x4/x6/x8 (DS12992)

[6] Datasheet STM32G051x6/x8 (DS13303)

- [7] Datasheet STM32G071x8/xB (DS12232)

- [8] Datasheet STM32G0B1xB/xC/xE (DS13560)

- [9] Datasheet STM32G041x6/x8 (DS12993)

- [10] Datasheet STM32G061x6/x8 (DS13513)

- [11] Datasheet STM32G081xB (DS12231)

- [12] Datasheet STM32G0C1xC/xE (DS13564)

- [13] Datasheet STM32U083xC (DS14463)

- [14] Datasheet STM32U073x8/B/C (DS14548)

- [15] Datasheet *STM32U031x4/6/8* (DS14581)

- [18] Reference Manual STM32G0x1 advanced Arm®-based 32-bit MCUs (RM0444)

- [19] Reference Manual STM32G0x0 advanced Arm®-based 32-bit MCUs (RM0454)

- [20] Reference Manual STM32U0 series advanced Arm®-based 32-bit MCUs (RM0503)

AN6226 - Rev 1 page 2/24

### 2 STM32U0 and STM32G0 overview

STM32U0 and STM32G0 devices share the same technology platform, core, and common IP set. While STM32G0 offers advanced features (such as advanced analog and low-power capabilities) at a low price point, STM32U0 focuses on key functions for further ultra-low-power optimization and embedded security.

In particular, STM32U0 series devices offer the additional low-power mode Stop 2. The STM32U0 series features an Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor at 56 MHz, versus a Cortex<sup>®</sup>-M0+ processor at 64 MHz featured on the STM32G0 series. STM32U0 devices also feature optimized flash memory access through the adaptive real-time memory accelerator (ART accelerator).

STM32U0 series MCUs increase the low-power efficiency in dynamic mode (µA/MHz), and reach a very low level of static power consumption in the various available low-power modes.

The detailed list of available features and packages for each product is available in the respective datasheets. STM32U0 series devices include a larger set of peripherals with advanced features than the STM32G0 series, such as:

- Low-power universal asynchronous receiver transmitter (LPUART)

- Low-power timer (LPTIM)

- Liquid-crystal display (LCD)

- Enhanced security features

STM32U0 does not embed controller area network (CAN) or USB Power Delivery (USB PD) interfaces.

The STM32G0 series is available in two variants: the Access line and the Value line.

The Access line is the most advanced variant, with a full set of peripherals, option bytes, and temperature range, and a wide range of package flavours.

The Value line focuses on key features, and offers one temperature range and a more limited set of packages, to enhance cost efficiency.

The STM32U0 series is available only in an equivalent form of the Access line.

AN6226 - Rev 1 page 3/24

# 3 Migrating between the STM32U0 and STM32G0

All STM32U0 and STM32G0 devices use the same technological platform, making software migration between the two series a straightforward process.

However, the pinouts are different for both series, so a PCB redesign is mandatory when migrating between products. Some GPIO pins are also absent in case of a migration from STM32G0 to STM32U0 in the same package.

AN6226 - Rev 1 page 4/24

### 4 Hardware migration

### 4.1 Pinout compatibility

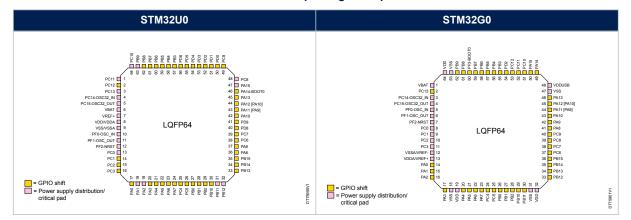

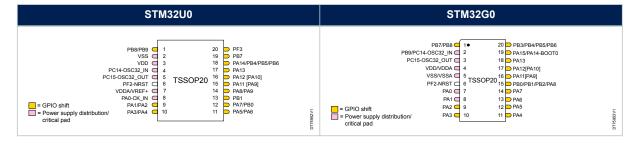

The STM32U0 and STM32G0 series do not share the same pinout. There is a different number of supply pairs on the package, as the STM32G0 series distributes the supply over the chip inside the package. Consequently, there are less GPIOs on the STM32U0 series and they are shifted by one or more pins on the same packages. When both series offer the same peripherals, the digital alternate functions and additional functions are preserved on the same GPIO where possible.

When designing the PCB, the user must consider different requirements for power supply distribution, as well as the position of critical pads, like oscillators and GPIO pins, as indicated by the pink rectangles in the figures below. The yellow rectangles indicate GPIO shifts.

Table 1. LQFP64 package comparison

### 4.2 Package availability

Some packages are available for both the STM32G0 and STM32U0, as illustrated in Table 3. However, each product has its own WLCSP package. Since WLCSP is unique for each product, these packages are listed separately in Table 4.

AN6226 - Rev 1 page 5/24

Table 3. Package availability for STM32U0 and STM32G0

|                        | STM       | 32U0                   | STM32G0                             |                                                    |                                                    |                                                    |

|------------------------|-----------|------------------------|-------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Package                | STM32U031 | STM32U073<br>STM32U083 | STM32G030<br>STM32G031<br>STM32G041 | STM32G050 <sup>(1)</sup><br>STM32G051<br>STM32G061 | STM32G070 <sup>(1)</sup><br>STM32G071<br>STM32G081 | STM32G0B0 <sup>(1)</sup><br>STM32G0B1<br>STM32G0C1 |

| SO8N (4.9 × 6 mm)      | -         | -                      | Х                                   | -                                                  | -                                                  | -                                                  |

| TSSOP20 (6.5 × 4.4 mm) | Х         | -                      | Х                                   | Х                                                  | -                                                  | -                                                  |

| UFQFPN28 (4 × 4 mm)    | -         | -                      | X                                   | Х                                                  | Х                                                  | -                                                  |

| LQFP32 (7 × 7 mm)      | -         | -                      | Х                                   | X                                                  | Х                                                  | Х                                                  |

| UFQFPN32 (5 × 5 mm)    | Х         | X                      | Х                                   | Х                                                  | Х                                                  | X                                                  |

| LQFP48 (7 × 7 mm)      | Х         | X                      | X                                   | Х                                                  | Х                                                  | Х                                                  |

| UFQFPN48 (7 × 7 mm)    | X         | X                      | Х                                   | Х                                                  | Х                                                  | X                                                  |

| LQFP64 (10 × 10 mm)    | Х         | X                      | -                                   | -                                                  | Х                                                  | X                                                  |

| UFBGA64 (5 × 5 mm)     | X         | X                      | -                                   | -                                                  | Х                                                  | X                                                  |

| LQFP80 (12 × 12 mm)    | -         | ×                      | -                                   | -                                                  | -                                                  | X                                                  |

| LQFP100 (14 × 14 mm)   | -         | -                      | -                                   | -                                                  | -                                                  | X                                                  |

| UFGBA100 (7 × 7 mm)    | -         | -                      | -                                   | -                                                  | -                                                  | Х                                                  |

<sup>1.</sup> On STM32G0x0 devices (Value line), only SOxN and LQFP packages are available.

Table 4. WLCSP package availability for STM32U0 and STM32G0

| Product                | WLCSP package and size   |

|------------------------|--------------------------|

| STM32U031              | WLCSP27 (2.55 x 2.34 mm) |

| STM32U073<br>STM32U083 | WLCSP42 (2.82 × 2.93 mm) |

| STM32G031<br>STM32G041 | WLCSP18 (1.86 × 2.14 mm) |

| STM32C071              | WLCSP19 (2.52 × 1.67 mm) |

| STM32G051<br>STM32G061 | WLCSP20 (1.94 × 2.40 mm) |

| STM32C091<br>STM32C092 | WLCSP24 (2.61 × 1.73 mm) |

| STM32G071<br>STM32G081 | WLCSP25 (2.3 × 2.5 mm)   |

| STM32G0B1<br>STM32G0C1 | WLCSP52 (3.09 × 3.15 mm) |

AN6226 - Rev 1 page 6/24

The STM32U0 and STM32G0 series share the same peripheral platform with the same register basis. The sections below show only the differences between the two series.

Table 5. Peripheral summary of STM32U0 and STM32G0

| STM32U0            |                                                           |           |                        |           | STM32G0                |           |                        |           |                        |           |                        |

|--------------------|-----------------------------------------------------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|

| Fea                | ture                                                      | STM32U031 | STM32U073<br>STM32U083 | STM32G030 | STM32G031<br>STM32G041 | STM32G050 | STM32G051<br>STM32G061 | STM32G070 | STM32G071<br>STM32G081 | STM32G0B0 | STM32G0B1<br>STM32G0C1 |

| Flash memo         | ry (in Kbytes)                                            | Up to 32  | Up to 256              |           | Up t                   | o 64      |                        | Up to     | 128                    | Up to     | 512                    |

| SRAM (ii           | n Kbytes)                                                 | 12        | 40                     |           | 3                      | 1         | 18                     | 3         | 6                      | 14        | 14                     |

| ART Ac             | celerator                                                 | Ye        | es                     |           |                        |           | N                      | lo        |                        |           |                        |

| V <sub>DD</sub> m  | inimum                                                    | 1.        | .7                     | 2         | 1.7                    | 2         | 1.7                    | 2         | 1.7                    | 2         | 1.7                    |

| V <sub>DD</sub> ma | aximum                                                    |           |                        |           |                        | 3         | 3.6                    |           |                        |           |                        |

| Maximu             | m speed                                                   | 56 N      | МНz                    |           |                        |           | 64 [                   | MHz       |                        |           |                        |

| ADC c              | hannel                                                    |           |                        |           |                        | 16        | + 3                    |           |                        |           |                        |

| ADC re             | solution                                                  | 12-bit    | 12-bit                 |

| DAC c              | hannel                                                    | •         | 1                      |           | 0                      |           | 2                      | 0         | 2                      | 0         | 2                      |

| CO                 | MP                                                        | 1         | 2                      |           | 0                      |           | 2                      | 0         | 2                      | 0         | 3                      |

| VRE                | FBUF                                                      | No        | Yes                    |

|                    | Advanced<br>16-bit                                        |           |                        |           |                        |           | 1                      |           |                        |           |                        |

|                    | General purpose 1 32-bit  Timer  General purpose 3 16-bit |           | 1                      | 0         | 1                      | 0         | 1                      | 0         | 1                      | 0         | 1                      |

| Timer              |                                                           |           | 4                      |           |                        |           | 5                      | 6         | 7                      |           |                        |

|                    | Low-power                                                 | 2         | 3                      | 0         | 2                      | 0         | 2                      | 0         | 2                      | 0         | 2                      |

|                    | Basic                                                     | 2         | 2                      | (         | )                      |           |                        |           | 2                      |           |                        |

|                    | Watchdog                                                  |           |                        |           |                        |           | 2                      |           |                        |           |                        |

| STM32U0    |            |           |                        | STM32G0   |                        |           |                        |           |                        |           |                        |

|------------|------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|-----------|------------------------|

| Feature    |            | STM32U031 | STM32U073<br>STM32U083 | STM32G030 | STM32G031<br>STM32G041 | STM32G050 | STM32G051<br>STM32G061 | STM32G070 | STM32G071<br>STM32G081 | STM32G0B0 | STM32G0B1<br>STM32G0C1 |

| DMA cl     | hannel     | 7         | 12                     |           | 5                      |           | 7                      | •         |                        |           | 12                     |

| USART      | Full       | 4         | 1                      |           | 1                      |           |                        |           | 2                      |           | 3                      |

| USART      | Basic      | 1         | 3                      | 2         | 1                      | 2         | 1                      | 4         | 2                      | 6         | 3                      |

| LPU        | ART        | 2         | 3                      | 0         | 1                      | 0         | 1                      | 0         | 1                      | 0         | 2                      |

| SF         | 기          | 2 3       |                        | 2         |                        |           |                        |           |                        |           | 3                      |

| I2C        | Full       | 4         | 1                      | 2         | 1                      | 2         | 1                      | 2         | 1                      | 3         | 2                      |

| 120        | Basic      |           | 0                      |           | 1                      | 0         | 1                      | 0         | 1                      | 0         | 1                      |

| HDMI       | -CEC       | 0         | 0                      | 0         | 0                      | 0         | 0                      | 0         | 1                      | 0         | 1                      |

| AE         | S          | No        | No/Yes                 |

| RN         | IG         | No        | Yes                    | No        | No/Yes                 | No        | No/Yes                 | No        | No/Yes                 | No        | No/Yes                 |

| UC         | PD         |           |                        |           | 0                      |           |                        |           | 2                      | 0         | 2                      |

| US         | SB         | 0         | 1                      |           |                        |           | 0                      |           |                        |           | 1                      |

| FDC        | CAN        |           |                        |           |                        | 0         |                        |           |                        |           | 2                      |

| RT         | C          |           |                        | 1         |                        |           |                        |           |                        |           |                        |

| LC         | D          | No        | Yes                    | 'es No    |                        |           |                        |           |                        |           |                        |

| Minimum te | emperature |           |                        |           |                        | -4        | O°C                    |           |                        |           |                        |

| Maximum te | emperature | Up to     | 125 °C                 | 85 °C     | Up to 125 °C           | 85 °C     | Up to 125 °C           | 85 °C     | Up to 125 °C           | 85 °C     | Up to 125 °C           |

### 5.1 RCC

Table 6, RCC differences between the STM32U0 and STM32G0 series

| Feature             | STM32U0 series                                                                      | STM32G0 series                                                          |  |  |  |

|---------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| PLL                 | Yes                                                                                 |                                                                         |  |  |  |

| HSI clock frequency | 16 MI                                                                               | Hz                                                                      |  |  |  |

| MSI clock frequency | 100 kHz to 48 MHz                                                                   | -                                                                       |  |  |  |

| LSI clock frequency | 32 kH                                                                               | Hz                                                                      |  |  |  |

| f <sub>HCLK</sub>   | Up to 56 MHz                                                                        | Up to 64 MHz                                                            |  |  |  |

| f <sub>PCLK</sub>   | - Op to 30 Wi12                                                                     | Op to 04 WII 12                                                         |  |  |  |

| System clock source | <ul><li>MSI</li><li>HSI16</li><li>HSE</li><li>PLL</li><li>LSE</li><li>LSI</li></ul> | <ul><li>HSI16</li><li>HSE</li><li>PLL</li><li>LSE</li><li>LSI</li></ul> |  |  |  |

### 5.2 Power

The STM32U0 and STM32G0 series share the same power supply scheme:

- V<sub>DD</sub>: This is the external power supply for the internal regulator and the system analog such as reset, power management, and internal clocks. It consists of one pair V<sub>DD</sub>/V<sub>SS</sub>.

- V<sub>DDA</sub>: This is the analog power supply for the A/D converter. It is shorted to V<sub>DD</sub> to reduce the number of power supply pins.

- V<sub>DDIOX</sub>: This is the power supply for the I/Os. It is typically shorted to V<sub>DD</sub> to reduce the number of supply

pins. However, on some products a second V<sub>DDIO2</sub> power supply is available.

- V<sub>DDUSB</sub>: This is the power supply for the USB drivers. It can be shorted to V<sub>DD</sub> to reduce the number of supply pins.

- V<sub>REF+</sub>: This is the input reference voltage for the ADC. In lower pin-count packages, V<sub>REF+</sub> is shorted to V<sub>DDA</sub>.

Table 7, PWR differences between STM32U0 and STM32G0

| Feature                  | STM32U0 series                                                                                                                                                                          | STM32G0x1 devices                                                                                                                                                       | STM32G0x0 devices                                                                                                                                     |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DD</sub> range    | 1.7                                                                                                                                                                                     | 2.0 to 3.6 V                                                                                                                                                            |                                                                                                                                                       |  |  |  |

| V <sub>DDIO2</sub> range | N/A                                                                                                                                                                                     | 1.65 to 3.6 V                                                                                                                                                           | N/A                                                                                                                                                   |  |  |  |

| VREFBUF                  |                                                                                                                                                                                         | Yes                                                                                                                                                                     | No                                                                                                                                                    |  |  |  |

| VBAT pin and RTC domain  |                                                                                                                                                                                         | Yes                                                                                                                                                                     |                                                                                                                                                       |  |  |  |

| Dynamic voltage scaling  | Yes (2 ranges)                                                                                                                                                                          |                                                                                                                                                                         |                                                                                                                                                       |  |  |  |

| Low-power regulator      | Yes                                                                                                                                                                                     |                                                                                                                                                                         |                                                                                                                                                       |  |  |  |

| Low-power modes          | <ul> <li>Run</li> <li>Low-power run</li> <li>Sleep</li> <li>Low-power sleep</li> <li>Stop 0</li> <li>Stop 1</li> <li>Stop 2</li> <li>Standby</li> <li>Shutdown</li> <li>VBAT</li> </ul> | <ul> <li>Run</li> <li>Low-power run</li> <li>Sleep</li> <li>Low-power sleep</li> <li>Stop 0</li> <li>Stop 1</li> <li>Standby</li> <li>Shutdown</li> <li>VBAT</li> </ul> | <ul> <li>Run</li> <li>Low-power run</li> <li>Sleep</li> <li>Low-power sleep</li> <li>Stop 0</li> <li>Stop 1</li> <li>Standby</li> <li>VBAT</li> </ul> |  |  |  |

AN6226 - Rev 1 page 9/24

| Feature                         | STM32U0 series | STM32G0x1 devices | STM32G0x0 devices |

|---------------------------------|----------------|-------------------|-------------------|

| Ultralow power enable (ENB_ULP) | Ye             | No                |                   |

|                                 | POR            |                   |                   |

| Power supply supervisor         | ВС             | POR/PDR           |                   |

|                                 | P\             |                   |                   |

The STM32U0 series has an additional Stop mode compared to the STM32G0 series. To help calculate the new power budget and ease the comparison between the low-power modes, the user can refer to the power consumption calculator included in STM32CubeMX.

Table 8. STM32U0 series low-power modes

| Mode            | Regulator           | CPU | Flash<br>memory | SRAM                   | Clock              | Peripheral                                              | Consumption <sup>(1)</sup><br>(STM32U073) | Wake-up<br>time  |

|-----------------|---------------------|-----|-----------------|------------------------|--------------------|---------------------------------------------------------|-------------------------------------------|------------------|

| Run             | Main<br>regulator   |     | On              |                        | Any                | All available                                           | 78 µA/MHz at<br>48 MHz                    | N/A              |

| Low-power run   | Low-power regulator |     | On              |                        | Any                | All available                                           | 80 μA/MHz at 2 MHz                        | 5 µs             |

| Sleep           | Main regulator      | Off | C               | <b>)</b> n             | Any                | All available                                           | 1.25 mA at 48 MHz                         | 11 CPU<br>cycles |

| Low-power sleep | Low-power regulator | Off | C               | <b>)</b> n             | Any                | All available                                           | 60 μA at 2 MHz                            | 11 CPU<br>cycles |

| Stop 0          | Main<br>regulator   | Off | On              | Retained               | HSI16, LSE,<br>LSI | RTC/TAMP,<br>USART, I <sup>2</sup> C,<br>LPTIM,<br>COMP | 105 μΑ                                    | 2 µs             |

| Stop 1          | Low-power regulator | Off | On              | Retained               | HSI16, LSE,<br>LSI | RTC/TAMP,<br>USART, I2C,<br>LPTIM,<br>COMP              | 3.3 µА                                    | 5 µs             |

| Stop 2          | Low-power regulator | Off | On              | Retained               | HSI16, LSE,<br>LSI | RTC/TAMP,<br>USART, I2C,<br>LPTIM,<br>COMP              | 940 nA                                    | 5 µs             |

| Standby         |                     | Off | 1               | Optional               | LSI, LSE           | IWDG, RTC/<br>TAMP                                      | 260 nA                                    | 30 µs            |

| Shutdown        |                     | Off |                 | Off (all content lost) | LSE                | RTC/TAMP                                                | 235 nA                                    | 340 µs           |

<sup>1.</sup> All consumption values are the typical value at  $T_a$  = 25 °C and  $V_{DD}$  = 3.0 V, with RTC enabled.

AN6226 - Rev 1 page 10/24

| Mode                    | Regulator           | СРИ | Flash<br>memory | SRAM                   | Clock              | Peripheral                                              | Consumption <sup>(1)</sup><br>(STM32G071) | Wake-up<br>time  |

|-------------------------|---------------------|-----|-----------------|------------------------|--------------------|---------------------------------------------------------|-------------------------------------------|------------------|

| Run                     | Main regulator      | On  | On              | On                     | Any                | All available                                           | 91 µA/MHz at<br>64 MHz                    | N/A              |

| Low-power run           | Low-power regulator | On  | On              | On                     | Any                | All available                                           | 198 µA/MHz at<br>2 MHz                    | 5 µs             |

| Sleep                   | Main regulator      | Off | On              | On                     | Any                | All available                                           | 1.8 mA at 64 MHz                          | 11 CPU<br>cycles |

| Low-power sleep         | Low-power regulator | Off | On              | On                     | Any                | All available                                           | 60 μA at 2 MHz                            | 11 CPU<br>cycles |

| Stop 0                  | Main<br>regulator   | Off | On              | Retained               | HSI16, LSE,<br>LSI | RTC/TAMP,<br>USART, I <sup>2</sup> C,<br>LPTIM,<br>COMP | 100 μΑ                                    | 2 µs             |

| Stop 1                  | Low-power regulator | Off | On              | Retained               | HSI16, LSE,<br>LSI | RTC/TAMP,<br>USART, I <sup>2</sup> C,<br>LPTIM,<br>COMP | 7.3 µA                                    | 5 µs             |

| Standby                 | Off                 | Off | Off             | Optional               | LSI, LSE           | IWDG, RTC/<br>TAMP                                      | 200 nA                                    | 30 µs            |

| Shutdown <sup>(2)</sup> | Off                 | Off | Off             | Off (all content lost) | LSE                | RTC/TAMP                                                | 33 nA                                     | 340 µs           |

<sup>1.</sup> All consumption values are the typical value at  $T_a$  = 25 °C and  $V_{DD}$  = 3.0 V.

# 5.3 RTC/TAMP and backup registers

Table 10. RTC differences between the STM32U0 and STM32G0 series

| Feature           | STM32U0 series            | STM32G0 series      |  |  |  |  |

|-------------------|---------------------------|---------------------|--|--|--|--|

| Wake-up timer     | Yes                       |                     |  |  |  |  |

| Number of alarms  | 2                         |                     |  |  |  |  |

| Timestamp feature | Yes                       |                     |  |  |  |  |

| Low-power mode    | All                       | All except Shutdown |  |  |  |  |

| Calendar overflow | Yes                       |                     |  |  |  |  |

| TAMP              | 3 externals + 4 internals |                     |  |  |  |  |

| Backup register   | 9 × 32-bit                | 5 × 32-bit          |  |  |  |  |

AN6226 - Rev 1 page 11/24

<sup>2.</sup> Not available on STM32G0x0 devices.

## 5.4 Embedded bootloader

Table 11. Bootloader interfaces on the STM32U0 and STM32G0 series

|            |                                                                            | STM32U0   |                        | STM32G0                             |                                     |                                     |                                     |  |   |

|------------|----------------------------------------------------------------------------|-----------|------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|--|---|

| Peripheral | Pins                                                                       | STM32U031 | STM32U073<br>STM32U083 | STM32G030<br>STM32G031<br>STM32G041 | STM32G050<br>STM32G051<br>STM32G061 | STM32G070<br>STM32G071<br>STM32G081 | STM32G0B0<br>STM32G0B1<br>STM32G0C1 |  |   |

| USB DFU    | USB_DM (PA11)<br>USB_DP (PA12)                                             | -         | Х                      |                                     | -                                   |                                     | <b>X</b> <sup>(1)</sup>             |  |   |

| USART1     | USART1_RX (PA10)<br>USART1_TX (PA9)                                        |           |                        | Х                                   |                                     |                                     |                                     |  |   |

| USART2     | USART2_RX (PA3)<br>USART2_TX (PA2)                                         |           | ×                      |                                     |                                     |                                     |                                     |  |   |

| USART3     | USART3_RX (PC11)<br>USART3_TX (PC10)                                       |           | x -                    |                                     |                                     | Х                                   |                                     |  |   |

| I2C1       | I2C1_SCL (PB6)<br>I2C1_SDA (PB7)                                           |           | x                      |                                     |                                     |                                     |                                     |  |   |

| I2C2       | I2C1_SCL (PB10) I2C1_SDA (PB11)                                            |           |                        | Х                                   |                                     |                                     |                                     |  |   |

| SPI1       | SPI1_MOSI (PA7) SPI1_MISO (PA6) SPI1_SCK (PA5) SPI1_NSS (PA4)              |           | Х                      |                                     | -                                   |                                     | - X                                 |  | x |

| SPI2       | SPI2_MOSI (PB15)<br>SPI2_MISO (PB14)<br>SPI2_SCK (PB13)<br>SPI2_NSS (PB12) |           | x                      | -                                   |                                     |                                     | х                                   |  |   |

| FDCAN      | FDCAN1_RX (PD0)<br>FDCAN1_TX (PD1)                                         | -         | X                      |                                     | -                                   |                                     | X <sup>(1)</sup>                    |  |   |

<sup>1.</sup> Not available on STM32G0B0 devices.

AN6226 - Rev 1 page 12/24

### 5.5 NVIC

Table 12. Interrupt vector differences between the STM32U0 and STM32G0 series

| Position | STM32U0 series                         | STM32G0 series                          | Address     |

|----------|----------------------------------------|-----------------------------------------|-------------|

| 0        | WWDG/IWDG                              | WWDG                                    | 0x0000 0040 |

| 1        | PVD/PVM                                | PVD/PVM                                 | 0x0000 0044 |

| 2        | RTC/TAMP                               | RTC/TAMP                                | 0x0000 0048 |

| 3        | FLASH                                  | FLASH                                   | 0x0000 004C |

| 4        | RCC/CRS                                | RCC/CRS                                 | 0x0000 0050 |

| 5        | EXTIO_1                                | EXTIO_1                                 | 0x0000 0054 |

| 6        | EXTI2_3                                | EXTI2_3                                 | 0x0000 0058 |

| 7        | EXTI4_15                               | EXTI4_15                                | 0x0000 005C |

| 8        | USB                                    | UCPD1/UCPD2/USB                         | 0x0000 0060 |

| 9        | DMA1_CH1                               | DMA1_CH1                                | 0x0000 0064 |

| 10       | DMA1_CH2_3                             | DMA1_CH2_3                              | 0x0000 0068 |

| 11       | DMAMUX/DMA1_CH4 to 7/<br>DMA2_CH1 to 5 | DMAMUX/DMA1_CH4 to 7/<br>DMA2_CH1 to 5  | 0x0000 006C |

| 12       | ADC/COMP                               | ADC/COMP                                | 0x0000 0070 |

| 13       | TIM1_BRK_UP_TRG_COM                    | TIM1_BRK_UP_TRG_COM                     | 0x0000 0074 |

| 14       | TIM1_CC                                | TIM1_CC                                 | 0x0000 0078 |

| 15       | TIM2                                   | TIM2                                    | 0x0000 007C |

| 16       | TIM3                                   | TIM3/TIM4                               | 0x0000 0080 |

| 17       | TIM6/DAC/LPTIM1                        | TIM6/DAC/LPTIM1                         | 0x0000 0084 |

| 18       | TIM7/LPTIM2                            | TIM7/LPTIM2                             | 0x0000 0088 |

| 19       | TIM14                                  | TIM14                                   | 0x0000 008C |

| 20       | TIM15                                  | TIM15                                   | 0x0000 0090 |

| 21       | TIM16                                  | TIM16/FDCAN_IT0                         | 0x0000 0094 |

| 22       | TIM17                                  | TIM17/FDCAN_IT1                         | 0x0000 0098 |

| 23       | I2C1                                   | I2C1                                    | 0x0000 009C |

| 24       | I2C2/I2C3                              | I2C2/I2C3                               | 0x0000 00A0 |

| 25       | SPI1                                   | SPI1                                    | 0x0000 00A4 |

| 26       | SPI2/SPI3                              | SPI2/SPI3                               | 0x0000 00A8 |

| 27       | USART1                                 | USART1                                  | 0x0000 00AC |

| 28       | USART2/LPUART2                         | USART2/LPUART2                          | 0x0000 00B0 |

| 29       | USART3/LPUART1                         | USART3/USART4/USART5/USART6/<br>LPUART1 | 0x0000 00B4 |

| 30       | USART4/LPUART3                         | CEC                                     | 0x0000 00B8 |

| 31       | AES/RNG                                | AES/RNG                                 | 0x0000 00BC |

Note: As both series embed the same Cortex®-M0+ CPU, they also share the same CPU interrupt structure.

## 5.6 Memory mapping

The STM32U0 and STM32G0 series share the same memory mapping and register addresses for common peripherals.

AN6226 - Rev 1 page 13/24

### 5.7 FLASH

Table 13, FLASH differences between STM32U0 and STM32G0

| Feature               | STM32U0 series                   | STM32G0 series     |  |  |

|-----------------------|----------------------------------|--------------------|--|--|

| ECC                   | Ye                               | es                 |  |  |

| Dual bank             | No                               | Yes <sup>(1)</sup> |  |  |

| Data width            | 72-bit (64-bit data + 8-bit ECC) |                    |  |  |

| Page size             | 2 Kbytes                         |                    |  |  |

| Subpage size          | 512 bytes                        |                    |  |  |

|                       | 3 levels:                        |                    |  |  |

| Number of wait-states | Zero wait-states                 |                    |  |  |

| Number of Walt-States | One wait-state                   |                    |  |  |

|                       | Two wait-states                  |                    |  |  |

<sup>1.</sup> Available only on 256-Kbyte and 512-Kbyte flash memory size devices.

Table 14. Option-byte differences between the STM32U0 and STM32G0 series

| Feature                | STM32U0 series         | STM32G0x1 devices        | STM32G0x0 devices  |  |  |  |

|------------------------|------------------------|--------------------------|--------------------|--|--|--|

|                        | Level 0: No protection |                          |                    |  |  |  |

| RDP level              |                        | Level 1: Read protection |                    |  |  |  |

|                        | Level 2: No debug      |                          |                    |  |  |  |

| WRP                    | Two areas              | Two areas per bank       | Two areas per bank |  |  |  |

| PCROP                  | No                     | Two areas per bank       | No                 |  |  |  |

| Securable memory area  | Yes                    | Yes                      | No                 |  |  |  |

| Boot lock              | Yes                    | Yes                      | No                 |  |  |  |

| IRHEN                  | Yes                    | Yes                      | No                 |  |  |  |

| NRST pin configuration | Yes                    | Yes                      | No                 |  |  |  |

| UID Yes                |                        | Yes                      | No                 |  |  |  |

### 5.8 SRAM

Both series have SRAM with parity check. The data bus width is 36 bits because 4 bits are allocated for the parity check (1 bit per byte). By default, the parity check is disabled. Setting the RAM\_PARITY\_CHECK option bit in the user option byte enables the parity check.

Table 15. SRAM density between the STM32U0 and STM32G0 series

| FLASH size | STM32U0 series SRAM size | STM32G0 series SRAM size<br>(parity check disabled) |  |  |

|------------|--------------------------|-----------------------------------------------------|--|--|

| 16 Khytoo  | STM32U031x6: 12 Kbytes   | STM32G031x4: 8 Kbytes                               |  |  |

| 16 Kbytes  | STM32U0x3x6: 40 Kbytes   |                                                     |  |  |

| 22 Khytoo  | STM32U031x6: 12 Kbytes   | STM32G031x6/STM32G041x6/STM32G030x6: 8 Kbytes       |  |  |

| 32 Kbytes  | STM32U0x3x6: 40 Kbytes   | STM32G051x6/STM32G061x6/STM32G050x6: 18 Kbytes      |  |  |

|            | STM32U031x6: 12 Kbytes   | STM32G031x8/STM32G041x8/STM32G030x8: 8 Kbytes       |  |  |

| 64 Kbytes  | STM32U0x3x6: 40 Kbytes   | STM32G051x8/STM32G061x8/STM32G050x8: 18 Kbytes      |  |  |

|            | STIVISZUUXSXO. 40 KDytes | STM32G071x8/STM32G081x8: 36 Kbytes                  |  |  |

| 128 Kbytes | STM32U0x3xB: 40 Kbytes   | STM32G071xB/STM32G081xB/STM32G070xB: 36 Kbytes      |  |  |

AN6226 - Rev 1 page 14/24

| FLASH size | STM32U0 series SRAM size | STM32G0 series SRAM size<br>(parity check disabled) |

|------------|--------------------------|-----------------------------------------------------|

| 256 Kbytes | STM32U0x3xB: 40 Kbytes   | STM32G0B1xC/STM32G0C1xC: 144 Kbytes                 |

| 512 Kbytes | -                        | STM32G0B1xE/STM32G0C1xE/STM32G0B0xE: 144 Kbytes     |

### **5.9 GPIO**

Table 16. GPIO differences between the STM32U0 and STM32G0 series

| Feature                                                    | STM32U0 series STM32G0 series |     |  |

|------------------------------------------------------------|-------------------------------|-----|--|

| Analog switch booster                                      | Yes                           |     |  |

| Clamping diode                                             | No                            | Yes |  |

| Pin mux protection when multiple pins are bounded together | No                            |     |  |

### 5.10 SYSCFG

The STM32U0 and STM32G0 series implement the same SYSCFG features, except these product-specific features:

#### STM32U0 series:

- TSC-related settings in the SYSCFG\_TSCCR register

- SRAM2:

- Erase in the SYSCFG\_SCR register

- Protection in the SYSCFG\_SKR register

#### STM32G0 series:

• XXX\_CDEN bits in the CFGR2 register: these bits enable or disable the clamping diode.

#### 5.11 ADC

Both the STM32U0 and STM32G0 series share the same 12-bit ADC with a sampling rate of up to 2.5 Msps.

Table 17. ADC channel list comparison for the STM32U0 and STM32G0 series

|        | STM32U0 s | series                 | STM32G0 series                                                             |                                                                            |  |

|--------|-----------|------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| PIN    | STM32U031 | STM32U073<br>STM32U083 | STM32G030<br>STM32G031<br>STM32G041<br>STM32G050<br>STM32G051<br>STM32G061 | STM32G070<br>STM32G071<br>STM32G081<br>STM32G0B0<br>STM32G0B1<br>STM32G0C1 |  |

| PA0    | IN4       |                        | INC                                                                        | )                                                                          |  |

| PA1    | IN5       |                        | IN1                                                                        |                                                                            |  |

| PA2    | IN6       |                        | IN2                                                                        |                                                                            |  |

| PA3    | IN7       |                        | IN3                                                                        |                                                                            |  |

| PA4    | IN8       |                        | IN4                                                                        |                                                                            |  |

| PA5    | IN9       |                        | IN5                                                                        |                                                                            |  |

| PA6    | IN10      |                        | IN6                                                                        |                                                                            |  |

| PA7    | IN14      |                        | IN7                                                                        |                                                                            |  |

| PA8    |           |                        | -                                                                          |                                                                            |  |

| VSENCE |           | I                      | N12                                                                        |                                                                            |  |

AN6226 - Rev 1 page 15/24

|         | STM32U0   | series                 | STM32G0 series                                                             |                                                                            |  |

|---------|-----------|------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| PIN     | STM32U031 | STM32U073<br>STM32U083 | STM32G030<br>STM32G031<br>STM32G041<br>STM32G050<br>STM32G051<br>STM32G061 | STM32G070<br>STM32G071<br>STM32G081<br>STM32G0B0<br>STM32G0B1<br>STM32G0C1 |  |

| VREFINT |           | I                      | N13                                                                        |                                                                            |  |

| VBAT/3  |           | I                      | N14                                                                        |                                                                            |  |

| PA11    | -         |                        | IN15 <sup>(1)</sup>                                                        | -                                                                          |  |

| PA12    | -         |                        | IN16 <sup>(1)</sup>                                                        | -                                                                          |  |

| PA13    | -         |                        | IN17                                                                       | -                                                                          |  |

| PA14    | -         |                        | IN18 -                                                                     |                                                                            |  |

| VDDA    |           |                        | -                                                                          |                                                                            |  |

| VSSA    |           |                        | -                                                                          |                                                                            |  |

| PB0     | IN17      |                        | IN8                                                                        |                                                                            |  |

| PB1     | IN18      |                        | IN9                                                                        |                                                                            |  |

| PB2     | -         |                        | IN10                                                                       |                                                                            |  |

| PB10    | -         |                        | IN11                                                                       |                                                                            |  |

| PB11    | -         |                        | IN15                                                                       |                                                                            |  |

| PB12    | -         |                        | IN16                                                                       |                                                                            |  |

| PC0     | IN0       |                        | -                                                                          |                                                                            |  |

| PC1     | IN1       |                        | -                                                                          |                                                                            |  |

| PC2     | IN2       |                        | -                                                                          |                                                                            |  |

| PC3     | IN3       |                        | -                                                                          |                                                                            |  |

| PC4     | IN15      |                        | - IN17                                                                     |                                                                            |  |

| PC5     | IN16      |                        | - IN18                                                                     |                                                                            |  |

| PB7     | -         |                        | IN11 <sup>(1)</sup>                                                        | -                                                                          |  |

<sup>1.</sup> Only on packages with less than 48 pins.

### **5.11.1** Temperature sensor

Table 18. Temperature sensor comparison for the STM32U0 and STM32G0 series

| Feature          | STM32U0 | STM32G0x1 devices | STM32G0x0 devices |

|------------------|---------|-------------------|-------------------|

| Number of TS_CAL | 2       | 1                 |                   |

| VTS linearity    |         |                   |                   |

### 5.12 TSC

The STM32U0 series supports touch sensing, whereas the STM32G0 series does not.

### 5.13 USB

Both the STM32U0 and STM32G0 series have a compatible USB peripheral.

## 5.14 USART, CRC, CRS, IWDG, and WWDG

Both the STM32U0 and STM32G0 series share the same peripheral and they are fully compatible.

AN6226 - Rev 1 page 16/24

### 5.15 I2C

STM32G0 supports System Management Bus (SMBus) and Power Management Bus (PMBus), which are compatible with I2C. This feature is not embedded in the STM32U0 series.

#### **5.16** FDCAN

The STM32G0 series supports FDCAN, whereas the STM32U0 series does not.

#### 5.17 SPI

Both series share the same peripheral and they are fully compatible. However, due to differences in maximum clock frequency, the maximum speed for the STM32U0 series is 27 MHz ( $f_{PCLK}$  / 2), while for the STM32G0 series it is 32 MHz ( $f_{PCLK}$  / 2).

### 5.18 DMA and DMAMUX

Both series share the same peripheral architecture. When the same peripherals are available on both products, their DMA assignment of multiplexer inputs to resources, trigger inputs to resources, and synchronization inputs to resources are identical.

### **5.19** Timer

The STM32U0 and STM32G0 series share the same timer features and instance names. They are described in Table 19.

Refer to Table 21 to compare the timer instances between both series.

Table 19. Timer feature comparison for the STM32U0 and STM32G0 series

| Timer type       | Timer          | Counter resolution | Counter<br>type      | Prescaler factor         | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary outputs |

|------------------|----------------|--------------------|----------------------|--------------------------|------------------------------|---------------------------------|-----------------------|

| Advanced control | TIM1           | 16-bit             | Up, down,<br>up/down | Integer from 1 to 2 × 16 | Yes                          | 4 + 2<br>internal               | 3                     |

|                  | TIM2           | 32-bit             | Up, down,<br>up/down | Integer from 1 to 2 × 32 | Yes                          | 4                               | -                     |

|                  | TIM3           | 16-bit             | Up, down,<br>up/down | Integer from 1 to 2 × 16 | Yes                          | 4                               | -                     |

| General          | TIM4           | 16-bit             | Up, down,<br>up/down | Integer from 1 to 2 × 16 | Yes                          | 4                               | -                     |

| purpose          | TIM14          | 16-bit             | Up                   | Integer from 1 to 2 × 16 | No                           | 1                               | -                     |

|                  | TIM15          | 16-bit             | Up                   | Integer from 1 to 2 × 16 | Yes                          | 1                               | 1                     |

|                  | TIM16<br>TIM17 | 16-bit             | Up                   | Integer from 1 to 2 × 16 | Yes                          | 1                               | 1                     |

| Basic            | TIM6<br>TIM7   | 16-bit             | Up                   | Integer from 1 to 2 × 16 | Yes                          | -                               | -                     |

The STM32U0 series embeds upgraded LPTIM features compared to the STM32G0 series. It supports up to four capture/compare channels and a repetition counter. Table 20 below lists the low-power timer features of both series.

AN6226 - Rev 1 page 17/24

Table 20. Low-power feature comparison for the STM32U0 and STM32G0 series

| STM32<br>series | Timer                      | Counter resolution | Counter<br>type | Prescaler<br>factor       | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary outputs | Repetition counter |

|-----------------|----------------------------|--------------------|-----------------|---------------------------|------------------------------|---------------------------------|-----------------------|--------------------|

| STM32G0         | LPTIM1<br>LPTIM2           | 16-bit             | Up              | 2 × n where<br>n = 0 to 7 | No                           | N/A                             | -                     | No                 |

| STM32U0         | LPTIM1<br>LPTIM2<br>LPTIM3 | 16-bit             | Up              | 2 × n where<br>n = 0 to 7 | No                           | 424                             | -                     | Yes                |

Table 21. Timer instance comparison between the STM32U0 and STM32G0 series

|                             |                       | STM32U0   |                        | STM32G0                |                                                  |                        |           |                        |           |

|-----------------------------|-----------------------|-----------|------------------------|------------------------|--------------------------------------------------|------------------------|-----------|------------------------|-----------|

| Feature                     | Time instance         | STM32U031 | STM32U073<br>STM32U083 | STM32G031<br>STM32G041 | STM32G051<br>STM32G061<br>STM32G071<br>STM32G081 | STM32G0B1<br>STM32G0C1 | STM32G030 | STM32G050<br>STM32G070 | STM32G0B0 |

| Advance timer (16-bit)      | TIM1                  | :         | x                      |                        | X <sup>(1)</sup>                                 |                        |           | Х                      |           |

| General purpose (32-bit)    | TIM2                  | - ·       |                        |                        |                                                  |                        |           |                        |           |

| General purpose<br>(16-bit) | TIM3, TIM14,<br>TIM16 | X         |                        |                        |                                                  |                        |           |                        |           |

|                             | TIM4                  | - X       |                        |                        | -                                                |                        | Х         |                        |           |

|                             | TIM15                 | -         | X                      | -                      | X                                                | (1)                    | -         |                        | X         |

|                             | TIM17                 |           | -                      | X                      |                                                  |                        |           |                        |           |

| Basic                       | TIM6, TIM7            | -         |                        |                        | X                                                |                        | - X       |                        |           |

| Low power                   | LPTIM1, LPTIM2        | -         |                        | X                      |                                                  | -                      |           |                        |           |

|                             | LPTIM3                | -         | Х                      |                        |                                                  |                        | -         |                        |           |

<sup>1.</sup> Timer with 2 × maximum CPU frequency capable

AN6226 - Rev 1 page 18/24

### 6 Software migration

This section describes how to migrate an application based on the STM32Cube MCU package.

The STM32U0 and STM32G0 series devices are part of the STM32Cube tool suite (which includes, among others, STM32CubeMX, and STM32CubeIDE, STM32CubeProgrammer).

Both series have the same architecture and are CMSIS compliant; they use the same driver naming and the same APIs for all common peripherals. Concerning the software migration, they use the same STM32Cube firmware libraries methodology with HAL and LL, as with all STM32 products. Using the HAL facilitates migration between the series, while the LL can be slightly different, especially for the RCC and PWR libraries.

Software migration can be executed using one of the following two methods:

- Manual library replacement: this method involves manually replacing the libraries.

- Using STM32CubeMX: this method is easier and reduces the risk of compilation errors.

The second method, using STM32CubeMX, is recommended as it simplifies the process and minimizes the risk of errors.

### 6.1 Software migration by replacing the libraries in hardware

To update the application code to run on the STM32U0xx library, follow these steps:

- 1. Update the toolchain startup files:

- a. Project files: device connections and flash memory loader. These files are provided with the latest version of the toolchain that supports STM32U0xx devices. For more information, the users must refer to the toolchain documentation.

- b. Linker configuration and vector table location files: templates of these files, developed following the CMSIS standard, are included in the STM32Cube installation package in the following directory: Drivers\CMSIS\Device\ST\STM32U0xx\Source\Templates.

- 2. Replace STM32U0xx library source files with the application sources:

- a. Replace the STM32G0xx\_conf.h file with STM32U0xx\_conf.h

- b. Replace the existing STM32G0xx\_it.c/STM32G0xx\_it.h files with STM32U0xx\_it.c/ STM32U0xx it.h

However, the RCC and PWR parts must be manually reworked to adapt the software to the new clock tree and power scheme architecture (refer to Section 5.1 and Section 5.2 for more details).

Moreover, in the <code>\_it.c</code> and <code>\_it.h</code> files, the functions must be updated to the new names, which can be found in the startup file.

### 6.2 Software migration by creating a new STM32CubeMX project

- 1. Create a new STM32CubeMX project with the chosen product.

- a. Pinout and configuration: configure the product according to the previous configuration (such as analog channel and USART).

- b. Clock configuration: choose the dedicated clock tree (such as system clock or peripheral clock) following the previous configuration.

- Project manager: in the advanced settings, select the appropriate "Driver selector" based on the driver used in the previous configuration.

- d. Generate the project.

- Open the desired IDE.

- a. Add all functions written in the previous project inside the STM32Cube tag (main.c, main.h, \_it.c, and \_it.h).

- b. Compile and run.

Some compilation errors can appear when a function is available on one product but not on the other. For example, functions linked to unlocking or locking the RTC domain are not available in the STM32U0 series.

AN6226 - Rev 1 page 19/24

## Hardware development boards available

#### Nucleo-64 boards

Nucleo-64 boars are the mainstream boards designed to allow the user to learn about and evaluate the features of an STM32 device.

They use a simple PCB that is common to all Nucleo-64 boards. This includes ST-LINK for chip debugging and to provide an RX-TX link between the computer and the MCU.

To help users with quick prototyping, the Nucleo board typically includes:

- Two buttons (one user button and one reset button).

- Two LEDs (one user LED and one power-up LED).

It is also possible to use add-ons that are compatible with the ARDUINO® Uno and ST morpho connector.

#### **Discovery boards**

Discovery boards are more affordable compared to Nucleo boards. They are relatively simple pieces of hardware designed to test the key features of the product.

#### **Evaluation board**

The STM32 evaluation boards have been designed as a complete demonstration and development platform for STM32 MCUs.

They include external circuitry, such as transceivers, sensors, memory interfaces, displays, and many more. The evaluation boards can be considered as a reference design for application development.

Table 22. Hardware development boards available for the STM32U0 series

| Board     | STM32U031     | STM32U073 | STM32U083     |

|-----------|---------------|-----------|---------------|

| Nucleo    | NUCLEO-U031R8 | -         | NUCLEO-U083RC |

| Discovery | -             | -         | STM32U083C-DK |

Table 23. Hardware development boards available for the STM32G0 series

| Board      | STM32G030<br>STM32G031<br>STM32G041 | STM32G050<br>STM32G051<br>STM32G061 | STM32G070<br>STM32G071<br>STM32G081 | STM32G0B0<br>STM32G0B1<br>STM32G0C1 |

|------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Nucleo     | NUCLEO-G031K8                       | -                                   | NUCLEO-G071RB<br>NUCLEO-G070RB      | NUCLEO-G0B1RE                       |

| Discovery  | STM32G0316-DISCO                    | -                                   | STM32G071B-DISCO                    | -                                   |

| Evaluation | -                                   | -                                   | STM32G081B-EVAL                     | STM32G0C1E-EV                       |

AN6226 - Rev 1 page 20/24

# **Revision history**

Table 24. Document revision history

| Date        | Version | Changes         |

|-------------|---------|-----------------|

| 21-Jan-2025 | 1       | Initial release |

AN6226 - Rev 1 page 21/24

# **Contents**

| 1   | Gene  | eral information                                          | 2  |  |  |  |

|-----|-------|-----------------------------------------------------------|----|--|--|--|

| 2   | STM   | 32U0 and STM32G0 overview                                 | 3  |  |  |  |

| 3   | Migr  | ating between the STM32U0 and STM32G0                     | 4  |  |  |  |

| 4   | Hard  | Hardware migration                                        |    |  |  |  |

|     | 4.1   | Pinout compatibility                                      | 5  |  |  |  |

|     | 4.2   | Package availability                                      | 5  |  |  |  |

| 5   | STM   | 32 product cross-compatibility                            | 7  |  |  |  |

|     | 5.1   | RCC                                                       | 9  |  |  |  |

|     | 5.2   | Power                                                     | 9  |  |  |  |

|     | 5.3   | RTC/TAMP and backup registers                             | 11 |  |  |  |

|     | 5.4   | Embedded bootloader                                       | 12 |  |  |  |

|     | 5.5   | NVIC                                                      | 13 |  |  |  |

|     | 5.6   | Memory mapping                                            | 13 |  |  |  |

|     | 5.7   | FLASH                                                     | 14 |  |  |  |

|     | 5.8   | SRAM                                                      | 14 |  |  |  |

|     | 5.9   | GPIO                                                      | 15 |  |  |  |

|     | 5.10  | SYSCFG                                                    | 15 |  |  |  |

|     | 5.11  | ADC                                                       | 15 |  |  |  |

|     |       | 5.11.1 Temperature sensor                                 | 16 |  |  |  |

|     | 5.12  | TSC                                                       | 16 |  |  |  |

|     | 5.13  | USB                                                       | 16 |  |  |  |

|     | 5.14  | USART, CRC, CRS, IWDG, and WWDG                           | 16 |  |  |  |

|     | 5.15  | I2C                                                       | 17 |  |  |  |

|     | 5.16  | FDCAN                                                     | 17 |  |  |  |

|     | 5.17  | SPI                                                       | 17 |  |  |  |

|     | 5.18  | DMA and DMAMUX                                            | 17 |  |  |  |

|     | 5.19  | Timer                                                     | 17 |  |  |  |

| 6   | Soft  | ware migration                                            | 19 |  |  |  |

|     | 6.1   | Software migration by replacing the libraries in hardware | 19 |  |  |  |

|     | 6.2   | Software migration by creating a new STM32CubeMX project  | 19 |  |  |  |

| 7   | Hard  | lware development boards available                        | 20 |  |  |  |

| Rev | ision | history                                                   | 21 |  |  |  |

|     |       | oles                                                      |    |  |  |  |

# **List of tables**

| Table 1.  | LQFP64 package comparison                                           | . 5 |

|-----------|---------------------------------------------------------------------|-----|

| Table 2.  | TSSOP20 package comparison                                          | . 5 |

| Table 3.  | Package availability for STM32U0 and STM32G0                        | . 6 |

| Table 4.  | WLCSP package availability for STM32U0 and STM32G0                  | . 6 |

| Table 5.  | Peripheral summary of STM32U0 and STM32G0                           | . 7 |

| Table 6.  | RCC differences between the STM32U0 and STM32G0 series              | . 9 |

| Table 7.  | PWR differences between STM32U0 and STM32G0                         | . 9 |

| Table 8.  | STM32U0 series low-power modes                                      | 10  |

| Table 9.  | STM32G0 series low-power modes                                      | 11  |

| Table 10. | RTC differences between the STM32U0 and STM32G0 series              | 11  |

| Table 11. | Bootloader interfaces on the STM32U0 and STM32G0 series             | 12  |

| Table 12. | Interrupt vector differences between the STM32U0 and STM32G0 series | 13  |

| Table 13. | FLASH differences between STM32U0 and STM32G0                       | 14  |

| Table 14. | Option-byte differences between the STM32U0 and STM32G0 series      | 14  |

| Table 15. | SRAM density between the STM32U0 and STM32G0 series                 | 14  |

| Table 16. | GPIO differences between the STM32U0 and STM32G0 series             |     |

| Table 17. | ADC channel list comparison for the STM32U0 and STM32G0 series      | 15  |

| Table 18. | Temperature sensor comparison for the STM32U0 and STM32G0 series    | 16  |

| Table 19. | Timer feature comparison for the STM32U0 and STM32G0 series         | 17  |

| Table 20. | Low-power feature comparison for the STM32U0 and STM32G0 series     | 18  |

| Table 21. | Timer instance comparison between the STM32U0 and STM32G0 series    | 18  |

| Table 22. | Hardware development boards available for the STM32U0 series        |     |

| Table 23. | Hardware development boards available for the STM32G0 series        | 20  |

| Table 24. | Document revision history                                           | 21  |

AN6226 - Rev 1 page 23/24

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6226 - Rev 1 page 24/24