# 6-axis IMU (inertial measurement unit) with high-g accelerometer, embedded AI, and sensor fusion for wearables and sport trackers

LGA-14L (2.5 x 3.0 x 0.83 mm) typ.

#### Product status link

LSM6DSV80X

| Product summary  |                                  |  |

|------------------|----------------------------------|--|

| Order code       | LSM6DSV80XTR                     |  |

| Temp. range [°C] | -40 to +85                       |  |

| Package          | LGA-14L<br>(2.5 x 3.0 x 0.83 mm) |  |

| Packing          | Tape and reel                    |  |

### Product resources

TN0018 (design and soldering)

#### **Features**

- Dedicated and independent gyroscope, low-g and high-g accelerometer channels, and data processing

- Smart FIFO up to 4.5 KB

- Dual accelerometer channels

- Low-g channel ±2/±4/±8/±16 g full scale

- High-g channel ±32/±64/±80 g full scale

- ±250/±500/±1000/±2000/±4000 dps full scale

- SPI / I<sup>2</sup>C & MIPI I3C<sup>®</sup> v1.1 serial interface with main processor data synchronization

- Programmable finite state machine for high-g and low-g accelerometer, gyroscope, and external sensor data processing with high rate @ 960 Hz

- Machine learning core with exportable features and filters for AI applications

- Embedded adaptive self-configuration (ASC)

- Embedded sensor fusion low-power (SFLP) algorithm

- Embedded temperature sensor

- Analog supply voltage: 1.71 V to 3.6 V

- Independent I/O supply (extended voltage range: 1.08 V to 3.6 V)

- Supply current

- 6-axis configuration @ 0.67 mA in combo high-performance mode

- 9-axis configuration @ 0.80 mA in combo high-performance mode

- Compact footprint: 2.5 mm x 3 mm x 0.83 mm

- ECOPACK and RoHS compliant

### **Applications**

- Wearables

- Sport trackers

- High-shock detection

- IoT and connected devices

- Augmented reality (AR) / virtual reality (VR) / mixed reality (MR) applications

### **Description**

The LSM6DSV80X is a breakthrough in the world of wearable technology. Its ability to handle both high and low acceleration values, combined with its energy efficiency and advanced processing capabilities, makes it a sensor for anyone looking to acquire data for in-depth analysis and achieve better performance in high-intensity impact and tracking activities in sports such as volleyball, soccer, tennis, boxing, or explosive jumps, and so forth. This IMU is a comprehensive solution for wearables, high-intensity impact and activity tracking, offering a blend of accuracy, integration, and efficiency.

The LSM6DSV80X is the world's first IMU to combine high-g (80 g) and low-g capabilities in a single package, integrating advanced features (edge processing and sensor fusion) and delivering consistent performance and valuable data for tracking and high-intensity impact detection in sports wearables.

The LSM6DSV80X enables edge AI, leveraging on a finite state machine (FSM) for configurable motion tracking and a machine learning core (MLC) for context awareness with exportable AI features for wearable applications.

The device supports the adaptive self-configuration (ASC) feature, which allows automatically reconfiguring the device in real time based on the detection of a specific motion pattern or based on the output of a specific decision tree configured in the MLC, without any intervention from the host processor.

DB5466 - Rev 1 page 2/14

### 1 Overview

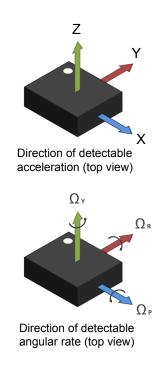

The LSM6DSV80X is a 6-axis system-in-package featuring a high-performance 3-axis digital low-g accelerometer (16 g), a 3-axis digital high-g accelerometer (80 g), and a 3-axis digital gyroscope.

The LSM6DSV80X delivers best-in-class motion sensing that can detect high-intensity impacts in order to empower developers to improve tracking in sports activities by accurately measuring both high and low accelerations efficiently. Whether it is the high-intensity forces in sports or the movements in everyday tracking, the LSM6DSV80X delivers consistent performance and valuable data for analysis.

The event-detection interrupts enable efficient and reliable motion tracking and context awareness, implementing hardware recognition of free-fall events, 6D orientation, click and double-click sensing, activity or inactivity, stationary/motion detection and wake-up events. Machine learning and finite state machine processing allow moving some algorithms from the application processor to the LSM6DSV80X sensor, enabling consistent reduction of power consumption.

The device supports the main OS requirements, offering real, virtual, and batch mode sensors. In particular, the LSM6DSV80X is designed to detect significant motion tracking, stationary/motion states, tilt, pedometer functions, timestamping and to support the data acquisition of external sensors.

The LSM6DSV80X offers hardware flexibility to connect the pins with different mode connections to external sensors to expand functionalities such as adding a sensor hub.

Channel 1 is designed to track motion detection. Data are available on the output of the I<sup>2</sup>C / SPI / I3C for the accelerometer and gyroscope with independent ODR and FS.

Channel 2 is designed for high-g applications with accelerometer processing and independent FS from  $\pm 32~g$  to  $\pm 80~g$ .

Up to 4.5 KB of FIFO with compression and dynamic allocation of significant data (that is, external sensors, timestamp, and so forth) allows overall power saving of the system.

The LSM6DSV80X embeds a sensor fusion low-power (SFLP) algorithm able to provide a 6-axis (accelerometer + gyroscope) game rotation vector represented as a quaternion. The X, Y, Z quaternion components are stored in FIFO.

Like the entire portfolio of MEMS sensor modules, the LSM6DSV80X leverages the robust and mature in-house manufacturing processes already used for the production of micromachined accelerometers and gyroscopes. The various sensing elements are manufactured using specialized micromachining processes, while the IC interfaces are developed using CMOS technology that allows the design of a dedicated circuit, which is trimmed to better match the characteristics of the sensing element.

The device embeds advanced dedicated features like a finite state machine and data filtering for motion processing.

The LSM6DSV80X is available in a small plastic, land grid array (LGA) package of  $2.5 \times 3.0 \times 0.83$  mm to address ultracompact solutions.

DB5466 - Rev 1 page 3/14

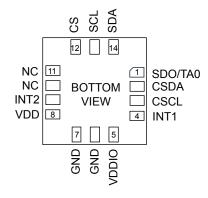

## 2 Pin description

Figure 1. Pin connections

DB5466 - Rev 1 page 4/14

### 2.1 Pin connections

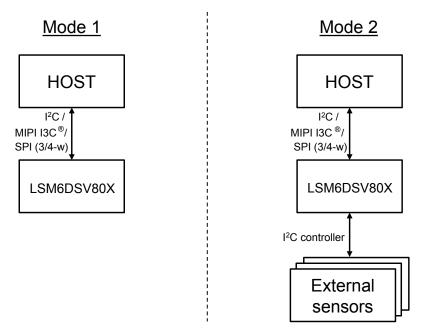

The LSM6DSV80X offers flexibility to connect the pins in order to have three different mode connections and functionalities. In detail:

- Mode 1: I<sup>2</sup>C / MIPI I3C<sup>®</sup> target interface or SPI (3- and 4-wire) serial interface is available.

- Mode 2: I<sup>2</sup>C / MIPI I3C<sup>®</sup> target interface or SPI (3- and 4-wire) serial interface and I<sup>2</sup>C controller interface for external sensor connections are available.

Figure 2. LSM6DSV80X connection modes

DB5466 - Rev 1 page 5/14

In the following table, each mode is described for the pin connections and function.

Table 1. Pin description

| Pin#   | Name                                                                                     | Mode 1 function                                                                | Mode 2 function                                                                     |  |

|--------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| SDO 1  |                                                                                          | SPI 4-wire interface serial data output (SDO)                                  | SPI 4-wire interface serial data output (SDO)                                       |  |

| !      | TA0                                                                                      | I <sup>2</sup> C least significant bit of the device address (TA0)             | I <sup>2</sup> C least significant bit of the device address (TA0)                  |  |

| 2      | CSDA                                                                                     | Connect to VDDIO or GND                                                        | I <sup>2</sup> C controller serial data (CSDA)                                      |  |

| 3      | CSCL                                                                                     | Connect to VDDIO or GND                                                        | I <sup>2</sup> C controller serial clock (CSCL)                                     |  |

| 4      | INT1                                                                                     | Programmable interrupt in I <sup>2</sup> C and SPI                             |                                                                                     |  |

| 5      | VDDIO <sup>(1)</sup>                                                                     | Power supply for I/O pins                                                      |                                                                                     |  |

| 6      | GND                                                                                      | 0 V supply                                                                     |                                                                                     |  |

| 7      | GND                                                                                      | 0 V supply                                                                     |                                                                                     |  |

| 8      | VDD <sup>(1)</sup>                                                                       | Power supply                                                                   |                                                                                     |  |

| 9 INT2 | INITO                                                                                    | Drogrammable interrupt 2 (INIT2)                                               | Programmable interrupt 2 (INT2)                                                     |  |

|        | INTZ                                                                                     | INT2 Programmable interrupt 2 (INT2)                                           | I <sup>2</sup> C controller external synchronization signal (CDRDY)                 |  |

| 10     | NC                                                                                       | Leave unconnected <sup>(2)</sup>                                               | Leave unconnected <sup>(2)</sup>                                                    |  |

| 11     | NC                                                                                       | Leave unconnected <sup>(2)</sup>                                               | Leave unconnected <sup>(2)</sup>                                                    |  |

|        |                                                                                          | I <sup>2</sup> C / MIPI I3C <sup>®</sup> / SPI mode selection                  | I <sup>2</sup> C / MIPI I3C <sup>®</sup> / SPI mode selection                       |  |

| 12     | 12 CS (1: SPI idle mode / I <sup>2</sup> C / MIPI I3C <sup>®</sup> communication enabled |                                                                                | (1: SPI idle mode / I <sup>2</sup> C / MIPI I3C <sup>®</sup> communication enabled; |  |

|        |                                                                                          | 0: SPI communication mode / I <sup>2</sup> C / MIPI I3C <sup>®</sup> disabled) | 0: SPI communication mode / I <sup>2</sup> C / MIPI I3C <sup>®</sup> disabled)      |  |

| 10     | 13 SCL                                                                                   | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial clock (SCL)                    | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial clock (SCL)                         |  |

| 13     |                                                                                          | SPI serial port clock (SPC)                                                    | SPI serial port clock (SPC)                                                         |  |

|        |                                                                                          | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial data (SDA)                     | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial data (SDA)                          |  |

| 14     | SDA                                                                                      | SPI serial data input (SDI)                                                    | SPI serial data input (SDI)                                                         |  |

|        |                                                                                          | 3-wire interface serial data output (SDO)                                      | 3-wire interface serial data output (SDO)                                           |  |

<sup>1.</sup> Recommended 100 nF filter capacitor.

DB5466 - Rev 1 page 6/14

<sup>2.</sup> Leave pin electrically unconnected and soldered to PCB.

### 3 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

### 3.1 LGA-14L package information

Figure 3. LGA-14L 2.5 x 3.0 x 0.83 mm package outline and mechanical data

Dimensions are in millimeters unless otherwise specified. General tolerance is +/-0.1mm unless otherwise specified.

### **OUTER DIMENSIONS**

| ITEM       | DIMENSION [mm] | TOLERANCE [mm] |

|------------|----------------|----------------|

| Length [L] | 2.50           | ±0.05          |

| Width [W]  | 3.00           | ±0.05          |

| Height [H] | 0.83           | ±0.03          |

DM01021587\_2

DB5466 - Rev 1 page 7/14

ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED.

### 3.2 LGA-14L packing information

W

P2 2.00±0.05(I) E1 1.75<u>±</u>0.10 Po 4.00±0.10(II) Ø1.50 0.00 0.30±0.05 D1 Ø1.50 MIN R0.20 TYP SECTION Y-Y SECTION X-X Measured from centreline of sprocket hot to controlline of plocket. Cumulative tolerance of 10 sprocket holes is ± 0.20. Measured from centreline of sprocket hole to centreline of pocket. Other material available. (1) +/- 0.05 Во 3.30 +/- 0.05 (11) Ko 1.00 +/- 0.10 (111) +/- 0.05 +/- 0.10 5.50 8.00 (IV) Forming format : Press form - 17-B

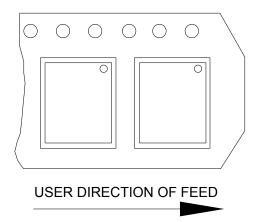

Figure 4. Carrier tape information for LGA-14L package

Figure 5. LGA-14L package orientation in carrier tape

Required length: 170 meter / 22B3 reel

DB5466 - Rev 1 page 8/14

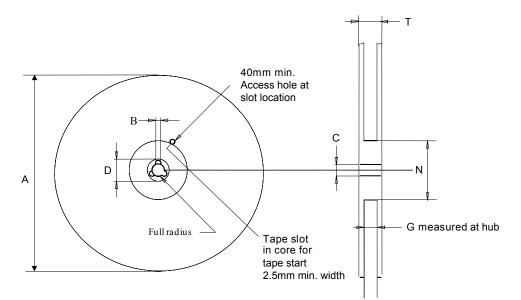

Figure 6. Reel information for carrier tape of LGA-14L package

Table 2. Reel dimensions for carrier tape of LGA-14L package

| Reel dimensions (mm) |            |  |

|----------------------|------------|--|

| A (max)              | 330        |  |

| B (min)              | 1.5        |  |

| С                    | 13 ±0.25   |  |

| D (min)              | 20.2       |  |

| N (min)              | 60         |  |

| G                    | 12.4 +2/-0 |  |

| T (max)              | 18.4       |  |

DB5466 - Rev 1 page 9/14

### **Revision history**

Table 3. Document revision history

| Date        | Version | Changes         |

|-------------|---------|-----------------|

| 22-Jan-2025 | 1       | Initial release |

DB5466 - Rev 1 page 10/14

### **Contents**

| 1    | Ove    | rview                       | 3  |  |

|------|--------|-----------------------------|----|--|

|      |        | Pin description             |    |  |

|      |        | Pin connections             |    |  |

| 3    | Pac    | kage information            | 7  |  |

|      | 3.1    | LGA-14L package information | 7  |  |

|      | 3.2    | LGA-14L packing information | 8  |  |

| Rev  | ision  | history                     | 10 |  |

| List | of ta  | bles                        | 12 |  |

| List | of fig | jures                       | 13 |  |

### **List of tables**

| Table 1. | Pin description                                     | 6 |

|----------|-----------------------------------------------------|---|

| Table 2. | Reel dimensions for carrier tape of LGA-14L package | 9 |

| Table 3. | Document revision history                           | 0 |

DB5466 - Rev 1 page 12/14

# **List of figures**

| Figure 1. Pin | n connections                                                  | 4 |

|---------------|----------------------------------------------------------------|---|

| Figure 2. LSI | SM6DSV80X connection modes                                     | 5 |

| Figure 3. LG  | GA-14L 2.5 x 3.0 x 0.83 mm package outline and mechanical data | 7 |

| Figure 4. Ca  | arrier tape information for LGA-14L package                    | 3 |

| Figure 5. LG  | SA-14L package orientation in carrier tape                     | 3 |

| Figure 6. Re  | eel information for carrier tape of LGA-14L package            | 9 |

DB5466 - Rev 1 page 13/14

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DB5466 - Rev 1 page 14/14