## Rad-hard 5 A step-down converter in plastic package

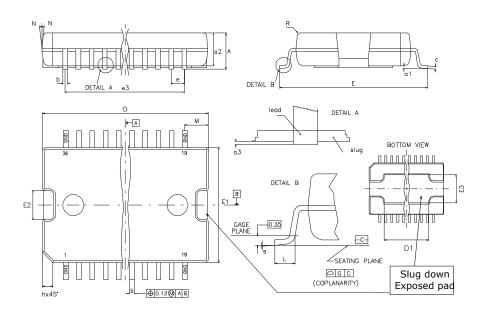

PowerSO-36 Connected slug-down

#### **Maturity status link**

LEOPOL1

#### **Features**

- Operating input voltage from 3 V to 12 V

- Output current @ 5.5 V up to 62 MeV.cm²/mg: 5 A

- Output voltage range: 0.8 V to 0.85 x Vin

- Configurable soft-start

- Current sharing with multiple devices

- Out-of-phase synchronization

- Full protection set: overtemperature, overcurrent, overvoltage

- Undervoltage lockout

- High dissipation PowerSO-36 package: R<sub>thic</sub> < 2 °C/W</li>

- Operating temperature range: -40 to +125 °C

- Compliant with ST's LEO specification, including

- Wisker free Nickel/Palladium/Gold lead finishing

- Gold wires

- Characterized outgassing: RML < 1% CVCM < 0.1%</li>

- Target radiation performance:

- 50 krad(Si) Total Ionizing Dose

- TNID immune at 3.10<sup>11</sup> proton/cm²

- SEL free up to 62 MeV.cm²/mg

## **Applications**

- Power management in satellites for Low Earth Orbit (LEO)

- FPGA, MPU, ASIC, and MCU power supply

- Power management in radiative and other harsh environments

## **Description**

The LEOPOL1 is a single-phase, step-down monolithic switching regulator with high-precision internal voltage reference and integrated power MOSFETs for synchronous conversion able to provide, at ground level (no single effect events), up to 7 A with up to 12-volt power supply, and up to 5 A from a 5.5 volt supply in a radiative environment up to 62 MeV.cm²/mg.

The LEOPOL1 can operate over a large temperature range of -40 °C to +125 °C. Designed using a BCD Silicon-On-Insulator (SOI) technology, it features an intrinsic radiation hardness, further enhanced through hardening by design, optimized to meet the radiation hardness required for Low Earth Orbit space crafts at an effective cost. Its PowerSO-36 package features a slug-down pad allowing a very low thermal resistance for a superior dissipation including in the absence of convection. It uses golden bonding and NiPdAl-lead-finishing to prevent whiskers. It complies with ASTM-E-595 and ESCC-Q-ST-70-02C outgassing standards for parts to be used in a vacuum.

The LEOPOL1 is compliant with the ST LEO generic specification, for space-ready rad-hard plastic products. This AEC-Q100 based specification offers radiation hardness and the capability to support large quantities, together with a trade-off optimized for LEO space crafts between quality assurance and cost of ownership (details on the ST LEO generic specification can be found in TN1432).

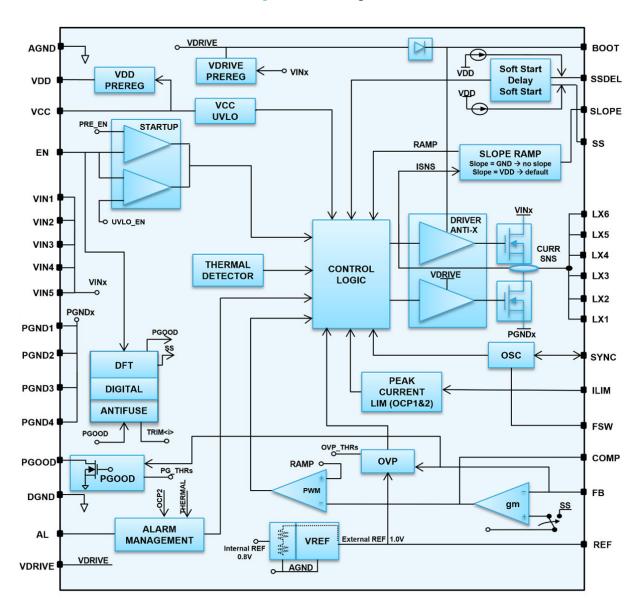

# 1 Diagram

Figure 1. Block diagram

DS14737 - Rev 2 page 2/43

# Pin configuration

Figure 2. Pin out (top view)

EP

36

35

35

34

31

32

30

8

9

10

11

12

13

14

15

16

17

18

EP

22

23

24

22

21

17

18

EP

19

Figure 2. Pin out (top view)

**Table 1. Pin description**

| Pin N°         | Symbol    | Description                                                                                                                                                                                                                                                       |

|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | EP        | Slug down exposed pad. Pin 18, 19, and 36 are also connect to it. The exposed pad should be connected to PGND to maximize disspation.                                                                                                                             |

| 2              | AGND/DGND | Signal ground. This is the ground for IC control loop, bias, and internal voltage reference. Connect to PCB ground plane through multiple vias.                                                                                                                   |

| 3              | VDD       | IC internal supply output. Bypass to GND with a 1 $\mu$ F ceramic capacitor. Maximum load allowed on this pin is 100 $\mu$ A. No current injection is allowed.                                                                                                    |

| 4              | VCC       | Filtered input power for control circuitry. Filter and bypass to GND with 4.7 $\Omega$ - 1 $\mu\text{F}$ R-C network.                                                                                                                                             |

| 5              | EN        | Enable pin, active high.                                                                                                                                                                                                                                          |

| 6, 7, 8, 9, 10 | VIN       | Power supply input. Bypass to PGND close to the IC package with capacitors with a low ESR (MLCC 3 x 47 $\mu$ F + 2 x 10 $\mu$ F is suggested).                                                                                                                    |

| 11, 12, 13, 14 | PGND      | Power ground. This is the reference ground for the internal power MOSFET's driver and VIN input rail. Connect to PCB ground plane through multiple vias.                                                                                                          |

| 15             | PGOOD     | Power Good signal, open drain. Pulled up to VIN or lower rail. This pin goes to a high state if VOUT stays inside +/-10% of target output voltage.                                                                                                                |

| 16             | AL        | Alarm pin. Bypassing to GND with a capacitor provides a timing alarm window proportional to capacitor value.                                                                                                                                                      |

| 17             | VDRIVE    | Internal generated and filtered rail for power MOS driver supply of the low-side and the high-side through bootstrap capacitor. One external capacitor (1 $\mu$ F) is required. Maximum load allowed on this pin is 100 $\mu$ A. No current injection is allowed. |

| 18, 19         | EP        | Slug down exposed pad. Pin 1 and 36 are also connect to it. The exposed pad should be connected to PGND to maximize disspation1                                                                                                                                   |

| 20             | REF       | Control loop voltage reference. Bypass to GND with a ceramic capacitor (1 $\mu$ F). Maximum load allowed on this pin is 100 $\mu$ A. No current injection is allowed.                                                                                             |

| 21             | FB        | Remote sensing input pin. Connect to the central tap of a resistor divider between VOUT and GND in order to program the output voltage level.                                                                                                                     |

DS14737 - Rev 2 page 3/43

| Pin N°                 | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |        | Maximum load/sink allowed on this pin is 1 μA.                                                                                                                                                                                                                                                                                                                                                                               |

| 22                     | COMP   | Loop compensation pin. Connect to GND through an R-C network, for loop compensation.                                                                                                                                                                                                                                                                                                                                         |

| 23                     | FSW    | Switching frequency programming pin. Connect FSW to GND through a resistor RFSW (and optional capacitor < 1 nF for filtering purposes). Connect to GND for slave mode operation (refer to SYNC pin description). Pull up to VDD or higher rail (3.6 V max.) to set default frequency (500 kHz).                                                                                                                              |

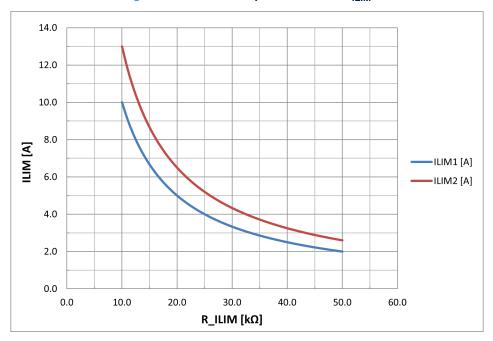

| 24                     | ILIM   | First and second level current limit thresholds programming. ILIM1 and ILIM2 can be adjusted through a single resistor. Connect ILIM to GND through a resistor to program a current limit ILIM1 lower than 10 A and ILIM2 = (1.3* ILIM1). An optional capacitor < 1 nF can be connected for filtering purposes in parallel to resistor. Pull up to VDD or higher rail (3.6 V max.) for ILIM1 = 10 A and ILIM2 = 13 A (typ.). |

| 25                     | SYNC   | Synchronization clock input (slave mode) or output (master mode) for 2 ICs' synchronization. Max. allowed capacitive load (equivalent) for slave devices is 150 pF.                                                                                                                                                                                                                                                          |

| 26, 27, 28, 29, 30, 31 | LX     | Regulator switching node. Connect directly to the inductor.                                                                                                                                                                                                                                                                                                                                                                  |

| 32                     | SS     | Soft-start programming pin. Connect to GND through a ceramic capacitor in order to program the proper turn-on timing.                                                                                                                                                                                                                                                                                                        |

|                        |        | Current sensing additional ramp programming.                                                                                                                                                                                                                                                                                                                                                                                 |

| 33                     | SLOPE  | Connect to GND through a resistor (and capacitor < 1 nF for filtering purposes) for control loop compensation tuning. Pull up to VDD or higher rail (3.6 V max.) to enable the internal default slope compensation.                                                                                                                                                                                                          |

| 34                     | SSDEL  | Soft-start delay programming pin. A capacitor must be connected between this pin and GND to program the switching regulator turn-on delay.                                                                                                                                                                                                                                                                                   |

| 35                     | ВООТ   | Bootstrap pin. It provides a power supply for the floating high-side driver.                                                                                                                                                                                                                                                                                                                                                 |

| 35                     | ВООТ   | Connect to LX through a bootstrap capacitor (100 nF suggested).                                                                                                                                                                                                                                                                                                                                                              |

| 36                     | EP     | Slug down exposed pad. Pin 1, 18 and 19 are also connect to it. The exposed pad should be connected to PGND to maximize dissipation.                                                                                                                                                                                                                                                                                         |

DS14737 - Rev 2 page 4/43

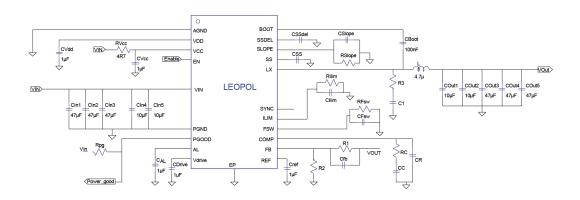

# 3 Application circuit

Figure 3. Typical application diagram

**Table 2. External components**

| Reference                                                | Description                                        | Suggested P/N      |

|----------------------------------------------------------|----------------------------------------------------|--------------------|

| L                                                        | Inductance, 4.7 μH, low DCR                        |                    |

| C <sub>in1</sub> , C <sub>in2</sub> , C <sub>in3</sub> , | Capacitor, 47 μF, 25 V, Ceramic low ESR            | GRM32ER61C476KE15L |

| C <sub>in4</sub> , C <sub>in5</sub>                      | Capacitor, 10 μF, 25 V, Ceramic low ESR            | GRM32ER71H106KA12L |

| Cout1, Cout2                                             | Capacitor, 10 μF, 25 V, Ceramic low ESR            | GRM32ER71H106KA12L |

| Cout3, Cout4, Cout5                                      | Capacitor, 47 μF, 25 V, Ceramic low ESR            | GRM32ER61C476KE15L |

| C <sub>drive</sub> , C <sub>Vdd</sub>                    | Capacitor, 1 µF, 6.3 V, Ceramic low ESR            |                    |

| C <sub>Vcc</sub>                                         | Capacitor, 1 µF, 25 V, Ceramic low ESR             |                    |

| C <sub>SSdel</sub> , C <sub>SS</sub>                     | Capacitor, 10 nF ÷ 1 μF, 6.3 V, Ceramic            |                    |

| C <sub>Slope</sub>                                       | Capacitor, 1 nF or less, 6.3 V, Ceramic (optional) |                    |

| C <sub>Ilim</sub>                                        | Capacitor, 1 nF or less, 6.3 V, Ceramic (optional) |                    |

| C <sub>Fsw</sub>                                         | Capacitor, 1 nF or less, 6.3 V, Ceramic (optional) |                    |

| C <sub>fb</sub>                                          | Capacitor, 100 pF ÷ 10 nF, 25 V, Ceramic           |                    |

| C <sub>ref</sub>                                         | Capacitor, 1 µF, 6.3 V, Ceramic                    |                    |

| C <sub>boot</sub>                                        | Capacitor, 100 F, 6.3 V, Ceramic                   |                    |

| C <sub>C</sub>                                           | Capacitor, 4.7 nF, 6.3 V, Ceramic                  |                    |

| C <sub>R</sub>                                           | Capacitor, 15 pF, 6.3 V, Ceramic                   |                    |

| R <sub>Vcc</sub>                                         | Resistor, 4.7 Ω, ¼ W, 5%,                          |                    |

| R <sub>PG</sub>                                          | Resistor, > 4.7 kΩ, ¼ W, 10%,                      |                    |

| R <sub>SLOPE</sub>                                       | Resistor, 15 kΩ, ¼ W, 5%,                          |                    |

| R <sub>Illim</sub>                                       | Resistor, ¼ W, 5% or less                          |                    |

| R <sub>Fsw</sub>                                         | Resistor, ¼ W, 5% or less                          |                    |

| R <sub>1</sub>                                           | Resistor, ¼ W, 5% or less                          |                    |

| R <sub>2</sub>                                           | Resistor, ¼ W, 5% or less                          |                    |

| R <sub>C</sub>                                           | Resistor, 27 Ω, ¼ W, 5% or less                    |                    |

DS14737 - Rev 2 page 5/43

# 4 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol                                                                                                                                                       | Parameter                             | Value                    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------|------|

| $V_{DD}$                                                                                                                                                     | Internal supply voltage               | AGND - 0.3 to AGND + 3.6 | V    |

| V <sub>IN</sub>                                                                                                                                              | Power supply voltage                  | PGND - 0.3 to PGND + 15  | V    |

| V <sub>CC</sub>                                                                                                                                              | Analog supply voltage                 | AGND - 0.3 to AGND + 15  | V    |

| V <sub>DRIVE</sub>                                                                                                                                           | Power MOS driver supply voltage       | AGND - 0.3 to AGND + 3.6 | V    |

| V <sub>EN</sub> , V <sub>SYNC</sub> , V <sub>SS</sub> , V <sub>SSDEL</sub> ,<br>V <sub>SLOPE</sub> , V <sub>ILIM</sub> , V <sub>COMP</sub> , V <sub>FB</sub> | Signal pins                           | AGND - 0.3 to AGND + 3.6 | V    |

| V <sub>BOOT</sub>                                                                                                                                            | Boot pin voltage (VBOOT-VLX)          | PGND - 0.3 to PGND + 18  | V    |

| $V_{LX}$                                                                                                                                                     | Switching node                        | PGND - 0.3 to VIN + 0.3  | V    |

| V <sub>PG</sub>                                                                                                                                              | Power Good pin voltage                | AGND - 0.3 to VCC + 0.3  | V    |

| V <sub>REF</sub>                                                                                                                                             | Reference voltage                     | AGND - 0.3 to AGND + 3.6 | V    |

| T <sub>JMAX</sub>                                                                                                                                            | Absolute maximum junction temperature | 175                      | °C   |

| V <sub>HBM</sub>                                                                                                                                             | ESD capability, human body model      | 2 K                      | V    |

| T <sub>STG</sub>                                                                                                                                             | Storage temperature range             | -40 to +150              | °C   |

| T <sub>OP</sub>                                                                                                                                              | Operating junction temperature range  | -40 to +125              | °C   |

Table 4. Thermal data

| Symbol            | Parameter                                               | Value | Unit |

|-------------------|---------------------------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case                        | 2     | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient (2s2p Jedec board ) | 25    | °C/W |

Table 5. Recommended operating conditions

| Symbol                            | Parameter                     |      | Unit |                        |       |

|-----------------------------------|-------------------------------|------|------|------------------------|-------|

| Зушио                             | Falallietei                   | Min. | Тур. | Max.                   | Offic |

| V <sub>IN</sub> , V <sub>CC</sub> | Input voltage range           | 3.0  |      | 12 (1)                 | V     |

| V <sub>OUT</sub>                  | Output voltage range          | 0.8  |      | V <sub>CC</sub> x 0.85 | V     |

| $V_{FSW}$                         | Default frequency mode        |      | VDD  |                        | V     |

| VFSW                              | Slave mode                    |      | GND  |                        | V     |

| R <sub>FSW</sub>                  | Programmed frequency mode     | 50   |      | 500                    | kΩ    |

| V <sub>SLOPE</sub>                | Default slope compensation    |      | VDD  |                        | V     |

| P <sub>D</sub>                    | Dissipated power              |      |      | TBD                    | W     |

| I <sub>OUT</sub>                  | Output current                |      |      | 7 (1)                  | А     |

| T <sub>AMB</sub>                  | Operating ambient temperature | -40  |      | 125                    | °C    |

| F <sub>SW</sub>                   | Switching frequency           | 100  |      | 1000                   | kHz   |

1. Check SOA for max. value under SEE.

DS14737 - Rev 2 page 6/43

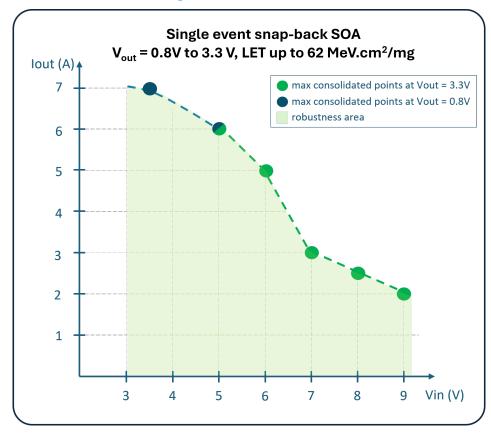

The LEOPOL1 provides up to 7 A and up to 12 V in a non-radiative environment. Figure 4 provides the safe operation area (SOA) of the product operation under 62 MeV.cm²/mg particles.

Figure 4. LEOPOL1 SEL SOA

DS14737 - Rev 2 page 7/43

## 5 Electrical characteristics

Table 6 provides the complete pre-rad electrical characteristics. Unless otherwise reported in Table 7, these pre-rad data fully apply up to 50 krad(Si).

**Conditions:** Unless otherwise specified,  $T_J$  =  $T_A$  = 25 °C,  $V_{IN}$  =  $V_{CC}$  = 5 V,  $V_{OUT}$  = 2.5 V,  $I_{OUT}$  = 3 A,  $F_{SW}$  = 500 kHz,  $C_{IN}$  =  $C_{OUT}$  = 3 x 47  $\mu$ F ceramic low ESR + 2 x 10  $\mu$ F ceramic low ESR, L = 4.7  $\mu$ H, pre-radiation.

Table 6. Electrical characteristics

| Symbol                                        | Parameter                                             | Test conditions                                                          | Min.  | Тур. | Max. | Unit |

|-----------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------|-------|------|------|------|

| Supply collect                                | ion                                                   |                                                                          |       |      |      |      |

|                                               | Feedback voltage                                      |                                                                          |       | 0.8  |      | V    |

| V <sub>FB</sub> <sup>(1)</sup> <sup>(2)</sup> | Initial accuracy                                      |                                                                          | -1    |      | +1   | %    |

|                                               | Temperature drift                                     | -55 °C < T <sub>J</sub> < +125 °C                                        | -1.25 |      | +1   | %    |

| IQ                                            | I <sub>VCC</sub> + I <sub>VIN</sub> quiescent current | EN = 1 V (no switching)                                                  | 2.5   | 3.5  | 4.5  | mA   |

| I <sub>SHDN</sub>                             | IVCC+IVIN shutdown current                            | EN = GND                                                                 | 250   | 400  | 550  | μA   |

|                                               | VCC undervoltage lockout upper threshold              | Rising edge, device disabled below this level                            | 2.65  | 2.85 | 3.05 | V    |

| V <sub>CC_UVLO</sub>                          | VCC undervoltage lockout lower threshold              | Falling edge, device enabled above this level                            | 2.45  | 2.65 | 2.85 | V    |

|                                               | UVLO hysteresis                                       |                                                                          |       | 200  |      | mV   |

| Efficiency                                    | Power efficiency                                      | L = 2.2 μH,<br>DCR = 6 m $\Omega$                                        |       | 92   |      | %    |

| Switching free                                | uency and synchronization                             |                                                                          |       |      |      |      |

| F <sub>SW</sub>                               | Default switching frequency                           | Voltage on F <sub>SW</sub> > 2 V                                         |       | 500  |      | kHz  |

|                                               |                                                       | Initial accuracy                                                         | -10   |      | +10  | %    |

|                                               |                                                       | Temperature drift, -55 $^{\circ}$ C < T <sub>J</sub> < +125 $^{\circ}$ C | -10   |      | +12  |      |

|                                               |                                                       | R <sub>FSW</sub> connected                                               | 100   |      | 1000 | kHz  |

| F <sub>SWP</sub>                              | Programmable switching frequency                      | Initial accuracy, $R_{FSW}$ = 50 k $\Omega$                              | 450   | 500  | 550  | kHz  |

| - SWI                                         | Trogrammable emicriming moquency                      | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C                     | -10   |      | +12  | %    |

| V <sub>FSW</sub>                              | Voltage on FSW pin                                    | R <sub>FSW</sub> connected                                               |       | 1    |      | V    |

| V <sub>SYNC_HI</sub>                          | Sync HIGH input threshold                             | V <sub>FSW</sub> < 0.1 V                                                 | 2.3   |      |      |      |

| V <sub>SYNC_LOW</sub>                         | Sync LOW input threshold                              | (slave configuration)                                                    |       |      | 1    | V    |

|                                               | Sync output voltage high level                        |                                                                          |       | VDD  |      | V    |

| V <sub>SYNC_OUT</sub>                         | Sync output voltage low level                         | R <sub>FSW</sub> connected (master configuration)                        |       |      | 0.4  | V    |

|                                               | Sync output fan-out                                   | comigaration,                                                            |       | 1    |      | mA   |

| On-time                                       |                                                       |                                                                          |       |      |      |      |

| T <sub>ON,MIN</sub>                           | Minimum on-time                                       |                                                                          |       | 120  |      | ns   |

| Internal supply                               | voltages, soft-start                                  | <u>'</u>                                                                 |       |      |      |      |

|                                               |                                                       |                                                                          |       | 1    |      | V    |

| V <sub>REF</sub> (2)(3)                       | Switching regulator reference voltage level           | Initial accuracy                                                         | -1.5  |      | +1.5 | %    |

|                                               | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3               | Temperature drift, -55 $^{\circ}$ C < T <sub>J</sub> < +125 $^{\circ}$ C | -2    |      | +2   | %    |

DS14737 - Rev 2 page 8/43

| Symbol                 | Parameter                                   | Test conditions                                      | Min. | Тур. | Max. | Unit |

|------------------------|---------------------------------------------|------------------------------------------------------|------|------|------|------|

| I <sub>SSDEL</sub>     | Soft-start delay capacitor charging current |                                                      | 90   | 100  | 110  | μA   |

| V <sub>SSDEL_THR</sub> | Soft-start delay voltage threshold          | Delay time starts from EN > 0.7 V                    | 0.9  | 1    | 1.1  | V    |

| I <sub>SS</sub>        | Soft-start capacitor charging current       |                                                      | 45   | 50   | 55   | μA   |

| V <sub>DD</sub> (3)    | Internal supply bus voltage                 |                                                      | 2.6  | 2.7  | 2.8  | V    |

| V <sub>DRIVE</sub> (3) | Power MOS driver supply voltage             |                                                      | 2.85 | 2.95 | 3.1  | V    |

| Current limit          |                                             |                                                      |      |      |      |      |

|                        | Default first level OCP                     | ILIM pin to V <sub>DD</sub>                          |      | 10   |      | Α    |

|                        | Programmed first level OCP                  | Initial accuracy, $R_{ILIM} = 75 \text{ k}\Omega$    | 0.99 | 1.1  | 1.21 | Α    |

| Luci                   |                                             | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C | -20  |      | +18  | %    |

| I <sub>LIM1</sub>      |                                             | Initial accuracy, R <sub>ILIM</sub> = 33 kΩ          | 2.7  | 3    | 3.3  | А    |

|                        |                                             | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C | -5   |      | +5   | %    |

| I <sub>LIM2</sub>      | Default second level OCP                    | $I_{LIM}$ pin to $V_{DD}$ , initial tolerance        |      | 13   |      | А    |

|                        | Programmed second level OCP                 | Initial accuracy, $R_{ILIM} = 75 \ k\Omega$          | 1.21 | 1.43 | 1.70 | А    |

|                        |                                             | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C | -20  |      | +25  | %    |

|                        |                                             | Initial accuracy, $R_{ILIM} = 33 \ k\Omega$          | 3.5  | 3.9  | 4.3  | А    |

|                        |                                             | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C | -5   |      | +5   | %    |

| V <sub>ILIM</sub>      | Voltage on ILIM pin                         | I <sub>LIM</sub> programmed by external resistor     | 0.97 | 1    | 1.03 | V    |

| ligh-side and          | low-side integrated MOSFET                  |                                                      |      |      |      |      |

| $R_{DSon,HS}$          | High-side MOS on-resistance                 | I <sub>OUT</sub> = 1 A                               | 10   | 25   | 30   | mΩ   |

| $R_{DSon,LS}$          | Low-side MOS on-resistance                  | 1001                                                 | 10   | 25   | 30   | mΩ   |

| Overvoltage p          | rotection and Power Good signal             |                                                      |      |      |      |      |

|                        | OVP threshold                               | Initial accuracy, referred to                        | 0.95 | 1    | 1.05 | V    |

| $V_{OVP}$ , $T_{H}$    | OVP reset threshold                         | V <sub>FB</sub> = 0.8 V                              | 0.78 | 0.85 | 0.92 | _ v  |

| A OAb' i H             | OVP threshold                               | Temperature drift, -55 °C < T <sub>J</sub>           | -17  |      | +5   | 0/   |

|                        | OVP reset threshold                         | < +125 °C                                            | -6   |      | +18  | - %  |

|                        | Upper rising threshold                      | Referred to V <sub>FB</sub> = 0.8 V                  | 106  | 110  | 115  | 2,   |

| $V_{PGOOD}$            | Lower falling threshold                     | Iverented to AEB - 0.0 A                             | 88   | 90   | 96   | - %  |

|                        | Output voltage low level                    | Open drain, I <sub>PGOOD</sub> = 5 mA                |      |      | 0.4  | V    |

| Overtemperatu          | ure protection (OVP) (OTP)                  |                                                      |      |      |      | '    |

|                        | Shutdown temperature                        |                                                      |      | 155  |      | 00   |

| T <sub>OTP</sub>       | Hysteresis                                  |                                                      |      | 20   |      | °C   |

| Alarm pin (AL)         |                                             |                                                      |      |      |      |      |

| I <sub>AL</sub>        | Alarm pin source/sink current               | Device in fault condition                            |      | 20   |      | μA   |

DS14737 - Rev 2 page 9/43

| Symbol                 | Parameter                                     | Test conditions                                                   | Min. | Тур. | Max.  | Unit  |

|------------------------|-----------------------------------------------|-------------------------------------------------------------------|------|------|-------|-------|

| Enable and UV          | LO                                            |                                                                   |      |      |       |       |

| PRE_EN                 | Pre-enable rising threshold                   | Device turned ON, but not switching                               | 0.67 | 0.7  | 0.73  |       |

| PRE_EN                 | Pre-enable rising threshold hysteresis        |                                                                   | 0.08 | 0.1  | 0.125 | V     |

| 10/10 FN               | UVLO enable HIGH threshold                    | Device switching                                                  | 1.18 | 1.24 | 1.3   |       |

| UVLO_EN                | UVLO enable hysteresis                        |                                                                   | 0.1  | 0.2  | 0.3   |       |

| Enable and UV          | LO                                            | <u>'</u>                                                          |      |      |       |       |

| PRE_EN                 | Pre-enable rising threshold                   | Device turned ON, but not switching                               | 0.67 | 0.7  | 0.73  |       |

|                        | Pre-enable rising threshold hysteresis        |                                                                   | 0.08 | 0.1  | 0.12  | V     |

| UVII O EN              | UVLO enable HIGH threshold                    | Device switching                                                  | 1.18 | 1.24 | 1.3   |       |

| UVLO_EN                | UVLO enable hysteresis                        |                                                                   | 0.1  | 0.2  | 0.3   |       |

| Slope compens          | sation                                        |                                                                   |      |      |       |       |

| Olava a Olava          | Voltage slope                                 | Initial accuracy, $R_{SLOPE}$ = 12 $k\Omega$ , $F_{SW}$ = 500 kHz | 225  | 250  | 275   | mV/µs |

| Slope_Comp             |                                               | Temperature drift, -55 °C < T <sub>J</sub> < +125 °C              | -18  |      | +32   | %     |

| V <sub>SLOPE</sub>     | Voltage at SLOPE pin                          | Slope programmed by external resistor                             |      | 0.8  |       | V     |

| Error amplifier        | (2)                                           |                                                                   |      |      |       |       |

| V <sub>INOFF</sub>     | Input offset                                  | F <sub>SW</sub> = 500 kHz                                         |      | 0.3  |       | mV    |

| TC <sub>EA</sub>       | Trans-conductance                             | V <sub>COMP</sub> = 1.35 V                                        |      | 0.94 |       | mS    |

| DCG <sub>EA</sub>      | DC gain                                       | V <sub>FB</sub> = 0.8 V                                           |      | 72   |       | dB    |

| I <sub>EA_OUT</sub>    | Output source/sink current                    | V <sub>COMP</sub> = 1.35 V, 100 mV<br>overdrive                   |      | 220  |       | μА    |

| Interleaving           | ,                                             |                                                                   |      |      |       |       |

| I <sub>MATCH</sub> (2) | Current mismatch between master and slave ICs |                                                                   |      |      | 10    | %     |

<sup>1.</sup> The temperature drift refers to the measured value on the sample at  $T_A$  = 25 °C.

DS14737 - Rev 2 page 10/43

<sup>2.</sup> Specified by design and characterization - not tested in production.

<sup>3.</sup> Maximum load allowed on this pin is 100  $\mu$ A. No current injection is allowed.

The post-radiation limit of a few parameters is different from the pre-radiation specification. Table 7 lists these parameters and provides the limits at 50 krad(Si).

$\textbf{Conditions:} \ \ \textbf{Unless otherwise specified,} \ \ \textbf{T_J} = \textbf{T_A} = 25 \ ^{\circ}\textbf{C}, \ \textbf{V_{IN}} = \textbf{V_{CC}} = 5 \ \textbf{V}, \ \textbf{V_{OUT}} = 2.5 \ \textbf{V}, \ \textbf{I_{OUT}} = 3 \ \textbf{A}, \ \textbf{F}_{SW} = 500 \ \textbf{kHz}, \ \textbf{C_{IN}} = \textbf{C}_{OUT} = 3 \ \textbf{x} \ \textbf{47} \ \mu \textbf{F} \ \text{ceramic low ESR} + 2 \ \textbf{x} \ \textbf{10} \ \mu \textbf{F} \ \text{ceramic low ESR}, \ \textbf{L} = 4.7 \ \mu \textbf{H}.$

Table 7. Post radiation electrical characteristics

| Symbol             | Parameter                                    | Test conditions                                                    | Min. | Тур. | Max. | Unit  |  |  |

|--------------------|----------------------------------------------|--------------------------------------------------------------------|------|------|------|-------|--|--|

| Internal suppl     | nternal supply voltages, soft-start          |                                                                    |      |      |      |       |  |  |

| I <sub>SSDEL</sub> | Soft-start delay capacitor charging current  |                                                                    | 90   | 100  | 120  | μА    |  |  |

| I <sub>SS</sub>    | Soft-start capacitor charging current        |                                                                    | 45   | 50   | 60   | μA    |  |  |

| Current limit      | '                                            |                                                                    |      |      |      |       |  |  |

|                    | Default first level OCP                      | ILIM pin to V <sub>DD</sub>                                        |      | 10   |      | Α     |  |  |

| I <sub>LIM1</sub>  | I <sub>LIM1</sub> Programmed first level OCP | Initial accuracy, R <sub>ILIM</sub> = 75 kΩ                        | 0.88 | 1.1  | 1.21 | Α     |  |  |

|                    |                                              | Initial accuracy, R <sub>ILIM</sub> = 33 kΩ                        | 2.7  | 3    | 3.3  | Α     |  |  |

| Slope compensation |                                              |                                                                    |      |      |      |       |  |  |

| Slope_Comp         | Voltage slope                                | Initial accuracy, $R_{SLOPE}$ = 12 k $\Omega$ , $F_{SW}$ = 500 kHz | 225  | 250  | 285  | mV/µs |  |  |

DS14737 - Rev 2 page 11/43

## 6 Radiation

## 6.1 Total ionizing dose

The LEOPOL1 is RHA guaranteed and ELDRS immune up to 50 krad(Si) as per MIL-STD-883 TM 1019 condition D.

The total ionization dose has been characterized in 2 steps:

- High and low dose rate characterization of a preliminary version of the product; in both cases on 5 biased and 5 unbiased pieces. This test has shown that the product is immune to ELDRS and that the worst-case configuration is with biased parts.

- High dose rate characterization on 5 biased parts of the final version of the product. It can be noted that:

- 1. The bipolar section is identical in both versions on the LEOPOL1, allowing to support the low dose rate with the test made on the preliminary one.

- 2. Only the worst-case configuration has been retested in the final version.

Unless otherwise provided in Table 7, the post-irradiation electrical and timing characteristics are the same as the pre-irradiation ones provided in Table 6.

On top of the characterization, each wafer lot is submitted to a wafer lot acceptance with a TID test at a high dose rate on 5 biased parts per wafer lot with an acceptance criterion of 0 fail.

Table 8. Total dose summary table

| Туре | Conditions                                                           | Result                                      |

|------|----------------------------------------------------------------------|---------------------------------------------|

| TID  | Up to 50 krad(Si):  at / 40 krad(Si)/h) (HDR)  at 36 rad(Si)/h (LDR) | RHA guaranted and ELDRS free at 50 krad(Si) |

DS14737 - Rev 2 page 12/43

## 6.2 Total non-ionizing dose

The total non-ionizing dose is tested with 50 MeV protons.

The test is performed during the product characterization and as part of the wafer lot acceptance test on 5 pieces per wafer lot with an acceptance criterion of 0 fail.

Table 9. Total non-ionization dose summary table

| Туре | Conditions                                                      | Result                                           |

|------|-----------------------------------------------------------------|--------------------------------------------------|

| TNID | Up to 3x10 <sup>11</sup> protons.cm <sup>2</sup> 50 MeV protons | Post TNID characteristics compliant with Table 6 |

## 6.3 Single event effect

The LEOPOL1 is characterized under heavy ions up to 62 MeV.cm<sup>2</sup>/mg as summarized below:

- Tests performed: SESB (\*), SET, SEU/SEFI

- Each test is performed on 3 samples of the final silicon in the worst-case conditions.

Table 10. SEE summary table provides the result of these tests.

Table 10. SEE summary table

| Туре | Conditions                                                                                                                | Result                                            |

|------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| SESB | Test up to 62.5 MeV.cm <sup>2</sup> /mg Temperature 25 °C Fluence: 1.10 <sup>7</sup> ion/cm <sup>2</sup> Normal incidence | Immune to SESB up to 62.5 MeV.cm <sup>2</sup> /mg |

| SET  | Temperature 25 °C                                                                                                         | Characterized                                     |

Single event effects are not tested in production.

(\*) While components with bulk substrates may be subject to latch-up under heavy ions (low impedance path between supply and ground triggered by current injection or overvoltage), the physical phenomenon possibly observed on components with SOI substrates such as the LEOPOL1 is snap-back (transistors turned on by an avalanche breakdown or impact ionization). The test set-up to characterize both effects and their effects on components are similar, hence the common confusion between SEL and SESB. However, the worst case condition for the latter is 25 °C, while it is 125 °C for SEL.

DS14737 - Rev 2 page 13/43

## 7 Device functional description

The LEOPOL1 is a radiation hardened high efficiency synchronous step-down monolithic switching regulator capable of delivering up to 7 A continuous output current in the absence of heavy ions (refer to SOA in section 3 for maximum current supply capability with SESB immunity).

The power input voltage ( $V_{IN}$ ), also in the absence of heavy ions, can range from 3 V to 12 V and, thanks to a 0.8 V internal voltage reference, the LEOPOL1 can precisely regulate the output voltage in the range of 0.8 V to 85% of  $V_{IN}$ .

Low R<sub>DSon</sub> N-channel MOSFETs for both HS (high-side) and LS (low-side) and also the boot diode are embedded, for minimum external component requirement. The peak current mode control loop, with a high bandwidth error amplifier and an external compensation, enables a stable operation with a wide range of output filter configurations (including multi-layer ceramic capacitor (MLCC) solutions) ensuring a fast response to load transient. For maximum design flexibility, all the most important features are programmable.

The LEOPOL01 features a full set of protections and output voltage monitoring:

- High accuracy programmable dual level overcurrent protection (internally compensated against temperature variations)

- Overvoltage protection (not latched)

- Overtemperature protection (latched after 16 consecutive fault events)

- Undervoltage lockout on input supply rail

- Power Good open drain output, which provides real-time information about the output voltage.

The SYNC pin allows 2 devices to be synchronized with 180° phase shift switching interleaving, reducing RMS current absorption from the input filter and preventing beating frequency noise, therefore allowing a reduction in the size and cost of the input filter.

The current share configuration allows 2 devices to be easily connected, providing up to 14 A. For higher output current requirement, n devices can be connected by means of an external circuitry providing the proper 360°/n phase shifted signals.

The dedicated enable pin (EN), the programmable soft-start duration, and soft-start delay offer easy control on the power sequencing and inrush current.

The LEOPOL1 is provided in a PowerSO-36 leads plastic package.

#### 7.1 Power section

The LEOPOL1 integrates two low on-resistance N-channel MOSFETs as low-side and high-side switches, optimized for fast switching transition and high efficiency over all the load range. The power stage is designed to deliver a continuous output current up to 7 A (in the absence of heavy ions).

The HS MOSFET drain is connected to the  $V_{IN}$  pins (power input), the LS MOSFET source is connected to the PGND pins (power ground); the HS MOSFET source and LS MOSFET drain are connected to the LX pins (see Figure 1 for details). The driving section is supplied by the  $V_{IN}$  pins through the internal voltage regulator ( $V_{DRIVE}$ ) that assures the proper driving voltage over all the supply range.

Proper design should comply with the recommendations below:

- Bypass V<sub>IN</sub> pins to PGND pins as close as possible to the IC package with high quality MLCC capacitors.

- Connect the bootstrap capacitor (typically a 100 nF ceramic capacitor rated to stand V<sub>IN</sub> voltage) from the BOOT pin to the LX pin to supply the high-side driver.

- Do not connect an external bootstrap diode. The IC already integrates a bootstrap diode to charge the bootstrap capacitor, saving the cost of this external component.

The LEOPOL1 embodies an anti-shoot-through and adaptive deadtime control to minimize the conduction time of the low-side body diode and consequently reduce power losses.

When the voltage at the LX pin drops (to check high-side MOSFET turn-off), the LS MOSFET is suddenly switched on. When the gate driving voltage of the LS drops (to check low-side MOSFET turn-off), the HS MOSFET is suddenly switched on.

The regulation stays active even if the current is negative (full PWM). In fact, if the current flowing in the inductor is negative, the voltage on the LX pin never drops. A watchdog controller is implemented to allow the LS MOSFET to turn on even in this case.

DS14737 - Rev 2 page 14/43

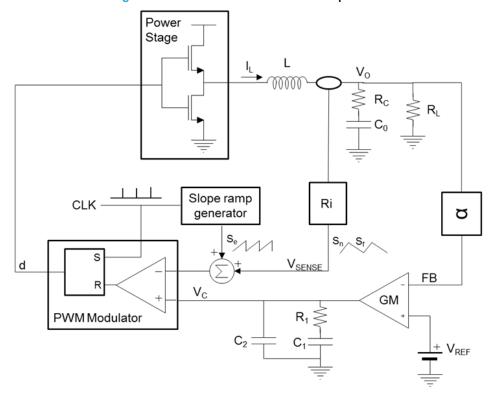

### 7.2 Control loop

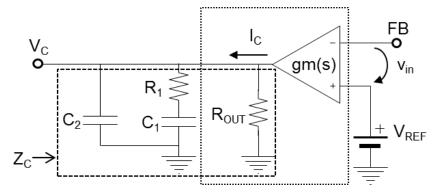

The LEOPOL1 is a constant-frequency, peak current mode switching regulator as shown in Figure 5.

Figure 5. Peak current mode control loop model

It employs two control loops: an external loop to control the output voltage and an inner loop to control the peak current that flows through the coil. The external loop (or voltage loop) compares the feedback voltage  $V_{FB}$  with the internally generated precise reference voltage  $V_{REF}$  at 0.8 V through the error amplifier GM. The error amplifier is a trans-conductance amplifier (OTA) that multiplies the difference of input voltage by a certain gain and generates a current into the output node  $V_{C}$  (pin COMP).

The external compensation circuit, RC network tied between  $V_C$  and ground, converts the current generated by the error amplifier into a voltage. In the inner loop (or current loop), the current sense circuit converts the current flowing through the coil into a sense voltage  $V_{SENSE}$  with gain factor  $R_i$  (0.1  $\Omega$ ). The voltages  $V_C$  and  $V_{SENSE}$  are compared by a PWM comparator and a Pulse Width Modulated (PWM) signal is generated, defining the duty cycle d. The power stage can be seen as a controlled current generator that provides the current  $I_L$  to the power stage output capacitor and load.

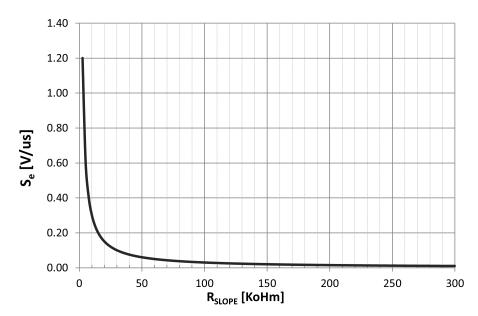

Finally, the voltage ramp  $S_e$ , programmable by the external  $R_{SLOPE}$  resistor, is added to the  $V_{SENSE}$  signal to stabilize the converter in case of duty cycle greater than 50% operation.

The control-to-output equivalent transfer function is described in Equation 1.

$$F(s) = \frac{V_o(s)}{V_c(s)} = \frac{R_L}{R_i} \cdot \frac{(sC_0R_C + 1)}{sC_0(R_C + R_L) + 1} \tag{1}$$

Co and RC are the output capacitance and its equivalent series resistance and Ro represents the output load.

In order to obtain the typical integrative loop transfer function, the signal stage must compensate for the power stage pole (due to the output capacitor and the load) and zero (above the loop bandwidth if ceramic output capacitors are selected). The signal stage transfer function is shown in Equation 2.

$$G(s) = \alpha g_m R_{OUT} \frac{(1 + R_1 C_1 s)}{(1 + R_{OUT} C_1 s)(1 + R_1 C_2 s)}$$

(2)

DS14737 - Rev 2 page 15/43

where:

- g<sub>m</sub> is the small signal gain of the trans-conductance stage

- $\alpha$  is the gain due to the output resistor divider ( $V_{REF} / V_{OUT}$ )

- R<sub>OUT</sub> is the output impedance of the amplifier (R<sub>OUT</sub> ≈ 4 MΩ).

Equation 2 is calculated assuming  $C_1 >> C_2$  and  $R_{OUT} >> R_1$ .

The external compensation network (R<sub>1</sub>, C<sub>1</sub>, and C<sub>2</sub>) must be designed in order to obtain:

One zero, matching the power stage pole (Equation 3)

#### **Equation 3**

$$C_1 R_1 = C_0 (R_L + R_C) \tag{3}$$

- One pole in order to delete the static output voltage error

- One pole, if necessary, matching the high frequency zero due to the output capacitor ESR, R<sub>C</sub> (Equation 4).

#### **Equation 4**

$$C_2 R_1 = C_0 R_C \tag{4}$$

The resulting control loop transfer function is the product of G(s) by F(s):

#### **Equation 5**

$$G_{LOOP}(s) = F(s)G(s) = \alpha g_m R_{OUT} \frac{R_L}{R_i} \frac{(1 + R_1 C_1 s)}{(1 + R_{OUT} C_1 s)(1 + R_1 C_2 s)} \frac{(1 + R_C C_0 s)}{1 + (R_C + R_L) C_0 s}$$

(5)

This model provides good results if the control loop bandwidth is lower than about F<sub>SW</sub>/10.

The error amplifier can be modeled as shown in Figure 6.

Figure 6. Simplified model of the error amplifier

It provides an output current  $I_C$  proportional to the trans-conductance gm and the input differential voltage  $V_{in}$ . The trans-conductance is a function of the frequency.

Its DC gain is given by:

Equation 6

$$A_v = gm \cdot R_{OUT} \tag{6}$$

where  $R_{OUT}$  is the output impedance of the amplifier ( $R_{OUT} \approx 4 \text{ M}\Omega$ ).

Finally, the transfer function of the error amplifier is given by:

#### **Equation 7**

$$\frac{V_C}{V_{in}} = gm(s) \cdot Z_C \tag{7}$$

DS14737 - Rev 2 page 16/43

$Z_{\mathbb{C}}$  is the equivalent impedance at the output of the error amplifier, and it can be displayed as the parallel of the output impedance and the compensation network:

#### **Equation 8**

$$Z_C = \frac{1}{C_2 s} \left\| \left( R_1 + \frac{1}{C_1 s} \right) \right\| R_{OUT} \tag{8}$$

For simplicity, the error amplifier is supposed to have a single pole, single zero at the frequency of  $w_{p1}$  and  $w_{z1}$ . Thus, its trans-conductance can be expressed as:

#### **Equation 9**

$$gm(s) = gm \cdot \frac{1 + s\frac{1}{w_{z1}}}{1 + s\frac{1}{w_{p1}}} \tag{9}$$

The typical values of  $w_{z1}$  and  $w_{p1}$  are  $w_{z1} \approx 2\pi \cdot 350$  k rad/s and  $w_{z1} \approx 2\pi \cdot 1.6$  M rad/s. Accurate modeling of the PWM modulator up to a high frequency is a must for a proper loop stability analysis. The linear time-invariant (LTI) model such as the Ridley model or similar is typically used for these purposes

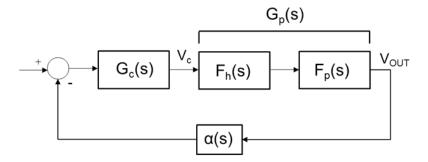

## 7.3 Ridley modeling applied to LEOPOL1

A more accurate model for stability is based on the approach suggested by Ridley for a peak current mode control scheme. It is accurate up to half of the switching frequency and allows us to precisely estimate the phase margin of the complete loop.

According to the Ridley model, an extra gain  $F_h(s)$ , representing the high frequency correction term of the controller transfer function, must be added to the main transfer function. Thanks to this term, the sub-harmonic oscillations that appear for duty cycle values above 50% are taken into account. This extra gain comes from a second order approximation of the continuous time modeling by Ridley and is valid up to half of the switching frequency. The effect of a feedforward capacitor in the feedback net is also taken into account by  $\alpha(s)$ .

Figure 7. Global loop transfer function

Figure 7 shows the global loop transfer function according to Ridley's modeling where:

$$G_{C}(s) = \frac{V_{C}(s)}{V_{FB}(s)} = g_{m}R_{OUT} \frac{1 + R_{1}C_{1}s}{(1 + R_{OUT}C_{1}s)(1 + R_{1}C_{2}s)}$$

(10)

$$\alpha(s) = \alpha(0) \frac{1 + R_{fb1}C_{fb}s}{1 + \alpha(0)R_{fb1}C_{fb}s} \qquad \alpha(0) = \frac{R_{fb2}}{R_{fb1} + R_{fb2}}$$

(11)

$$F_p(s) = \frac{R_L}{R_i} \frac{1}{1 + \frac{R_L T_{SW}}{L} \left[ m_c (1 - D) - 0.5 \right]} \frac{1 + R_C C_0 s}{1 + \frac{s}{\omega_p}}$$

(12)

Equation 13 (valid up to F<sub>SW</sub>/2, high frequency correction term)

DS14737 - Rev 2 page 17/43

$$F_h(s) = \frac{1}{1 + \frac{s}{\omega_n Q_p} + \frac{s^2}{\omega_n^2}} \tag{13}$$

Refer to Figure 8 for  $R_{FB1}/R_{FB2}/C_{FB}$  configuration. The parameters  $m_c$ ,  $\omega_n$ ,  $\omega_p$ , and  $Q_p$  can be calculated as follows:

$$\omega_{p} = \frac{1}{(R_{L} + R_{C})C_{O}} + \frac{T_{SW}}{LC_{O}} \left[ m_{c}(1 - D) - 0.5 \right]; \qquad Q_{p} = \frac{1}{\pi [m_{c}(1 - D) - 0.5]};$$

$$\omega_{n} = \frac{\pi}{T_{SW}} = \pi f_{SW}; \qquad m_{c} = 1 + \frac{S_{e}}{S_{n}} = 1 + \frac{\frac{V_{SLOPE}}{T_{SW}}}{\frac{V_{IN} - V_{OUT}}{L}R_{i}}$$

(14)

Figure 8. Feedback network with feedforward capacitor

The resulting complete open loop gain transfer function, accurate if  $C_1 >> C_2$  and  $R_{OUT} >> R_1$  up to  $F_{SW}/2$ , is:

$$G_{LOOP}(s) = \alpha(s)G_{\mathcal{C}}(s)F_p(s)F_h(s) \tag{15}$$

$$\begin{split} G_{LOOP}(s) &= \alpha(0 \\ ) \frac{1 + R_{fb1}C_{fb}s}{1 + \alpha(0)R_{fb1}C_{fb}s} g_m R_{OUT} \frac{1 + R_1C_1s}{(1 + R_{OUT}C_1s)(1 + R_1C_2s)} \frac{R_L}{R_i} \frac{1}{1 + \frac{R_LT_{SW}}{L}} [m_c(1 - D) - 05] \frac{1 + R_CC_0s}{1 + \frac{s}{\omega_p}} \frac{1}{1 + \frac{s}{\omega_nQ_p} + \frac{s^2}{\omega_n^2}} \\ G_{LOOP}(s) &= G_{LOOP}(0) \frac{1 + R_{fb1}C_{fb}s}{1 + \alpha(0)R_{fb1}C_{fb}s} \frac{1 + R_1C_1s}{(1 + R_{OUT}C_1s)(1 + R_1C_2s)} \frac{1 + R_CC_0s}{1 + \frac{s}{\omega_p}} \frac{1}{1 + \frac{s}{\omega_nQ_p} + \frac{s^2}{\omega_n^2}} \end{split}$$

Where:

$$G_{LOOP}(0) = g_m \alpha(0) \frac{R_{OUT} R_L}{R_i} \frac{1}{1 + \frac{R_L T_{SW}}{L} [m_c(1-D) - 05]}$$

$$\alpha(0) = \frac{R_{fb2}}{R_{fb1} + R_{fb2}}$$

DS14737 - Rev 2 page 18/43

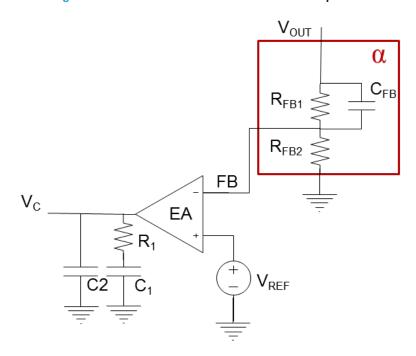

### 7.4 Fast load transient response

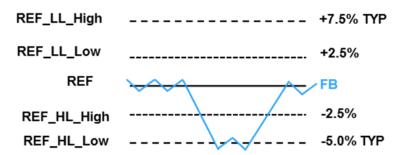

When fast load transient is applied to the output, the device is able to react very quickly in order to limit output voltage overshoot or undershoot. This feature is the combination of a fast error amplifier response and a proper control logic scheme that is driven by the use of two fast comparators, called HL (High Load) and LL (Low Load).

When the FB voltage goes below the REF\_HL, the HL comparator forces the on-time period turning ON the power switch. Typically, REF\_HL level is -5% below the nominal voltage loop reference of 800 mV. HL comparator output is latched to high level voltage until overcurrent protection occurs or the output voltage goes back again to the regulation voltage level. So, a proper voltage hysteresis is implemented: the comparator output goes low when the feedback goes back again to -2.5% of the regulation threshold (Figure 9). If during the ON-phase the current limit is reached, the minimum OFF-time period around 200 ns is applied.

Figure 9. Fast load transient response

Propagation delay time of the comparator has to be minimized to speed up device reaction to a fast step load but, once the ON-phase is triggered, the faster the coil ramp current slope, the lower the output voltage drop. For this reason, the lower inductance coil is suggested, for instance 0.8 µH is advised.

On the contrary, when the load current quickly decreases, the FB voltage can show an overshoot. The LL comparator output goes high when the FB goes above the REF\_LL voltage (typically +7% above the nominal 800 mV reference) and an OFF-time is forced. The OFF-time is kept until the FB voltage goes back again to the hysteresis threshold (typically +2.5%), or the negative inductor current threshold is reached. In fact, the device naturally works in full PWM mode, but when a fast negative step load occurs, the current on the coil can quickly go below zero. Therefore, a zero-crossing comparator, with a typical threshold of -1.5 A, is implemented avoiding the inductor coil going deeply below zero. When the zero-crossing threshold is reached, the switching activity is stopped, and the power stage is forced into an open loop condition (LX is in high impedance).

The two comparators themselves are not enough to speed the loop response, but as mentioned above, also the error amplifier must be able to speed up the transient response. A fast error amplifier with dynamic bias has been designed in order to improve the load-transient response. In practice, the error amplifier must be able to quickly charge or discharge the compensation capacitor (on the COMP pin), changing its output in a non-linear shape at a step change in the input of the error amplifier itself.

So, when one of the two comparators drives the ON or OFF-time phase, bandwidth and the large signal current capability (so the large signal current gain) of the error amplifier are also increased in parallel.

Finally, this solution allows a fast load transient response with lower output capacitance with smaller output voltage drop.

## 7.5 Slope compensation

As well-known and documented in literature, the current mode control can produce sub-harmonic oscillations when the duty cycle  $d \ge 50\%$ . Any perturbation in the inductor current, due to fluctuations in the control loop, can persist if the converter is operating at duty cycle greater than 50%. To overcome this issue, an additional ramp is usually added to the sensed one in order to over-dump the current loop and make the regulator stable. This feature is present in the LEOPOL1 for maximum design flexibility: in order to let the LEOPOL1 control loop work properly in case of  $d \ge 50\%$ , a current slope can be programmed by the user. Adding this current slope to the sensing current ramp also makes the regulator stable in this condition.

The slope compensation ramp is programmed by connecting an external  $R_{SLOPE}$  resistor between the SLOPE pin and GND.

A default internal slope compensation is also implemented, and it can be enabled by pulling up the voltage on the SLOPE pin to VDD by a resistor or simply by a short.

DS14737 - Rev 2 page 19/43

A compact formula can be used to set the slope compensation ramp. If  $V_{SL\_PK}$  is the peak value of the wanted voltage slope at the switching period  $T_{S_i}$ , the external resistor can be set as below:

$$R_{SLOPE} = \frac{3 \cdot 10e3 \cdot T_S[\mu s]}{V_{SL\_PK}[V]} = \frac{3 \cdot 10e3}{S_e \left[\frac{V}{\mu s}\right]}$$

(16)

where  $R_{SLOPE}$ ,  $T_S$ , and the voltage slope  $S_e$  are, respectively, expressed in  $k\Omega$ ,  $\mu s$ , and Volt. Here below, for example, a graph of the voltage slope ramp versus the SLOPE pin resistor is shown, in case of a typical frequency of 500 kHz and duty cycle supposed to be 50%.

Figure 10. Slope compensation ramp vs. R<sub>SLOPE</sub>, 500 kHz, d = 50%

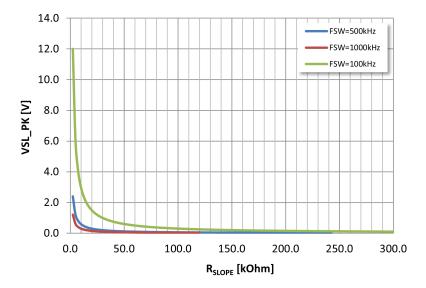

The user can therefore have maximum design flexibility. For instance, the following table summarizes the SLOPE pin programmability through the external resistor if the switching frequency is set from 100 kHz up to 1 MHz.

| Parameter          | Description                           | Condition                 | @ T <sub>ambient</sub> |      | Unit  |

|--------------------|---------------------------------------|---------------------------|------------------------|------|-------|

| Slope              | compensation programming              |                           | Min.                   | Max. |       |

| V_SLOPE            | Programmable slope peak voltage at Ts |                           | 0.1                    | 1.2  | V     |

|                    | External resistor range.              | F <sub>SW</sub> = 100 kHz | 25                     | 300  | kΩ    |

| R <sub>SLOPE</sub> |                                       | F <sub>SW</sub> = 500 kHz | 5                      | 60   |       |

|                    |                                       | F <sub>SW</sub> = 1 MHz   | 2.5                    | 30   |       |

|                    | Programmable slope                    | F <sub>SW</sub> = 100 kHz | 10                     | 120  |       |

| S <sub>e</sub>     |                                       | F <sub>SW</sub> = 500 kHz | 50                     | 600  | mV/μs |

|                    |                                       | F <sub>SW</sub> = 1 MHz   | 100                    | 1200 |       |

Table 11. Slope compensation programmability

Here below, for example, a graph of the voltage slope ramp peak over the SLOPE pin resistor is reported for three typical frequency values and duty cycle supposed to be 50%.

DS14737 - Rev 2 page 20/43

Figure 11. Slope compensation voltage peak vs. R<sub>SLOPE</sub>, d = 50%

Concerning the default ramp, here is a compact formula as a function of the switching frequency.

$$S_{e\ DEFAULT} = V_{SL\ PK} \cdot f_{SW} = 145e + 3$$

(17)

So, in the working case of a lower frequency of 100 kHz and maximum duty cycle, the maximum voltage peak on the ramp voltage due to the extra slope is supposed to be below 1.45 V.

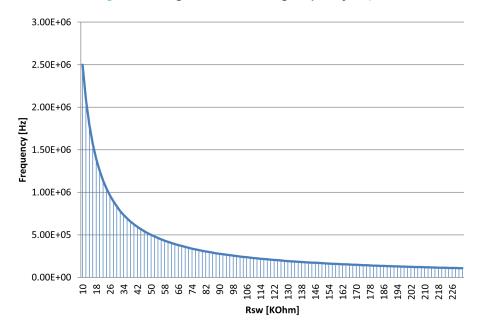

## 7.6 Switching frequency setting

The regulator switching frequency can be programmed by connecting an external resistor between the FSW pin and GND.

A voltage of 1 V is present on the FSW pin, so a current of  $1V/R_{FSW}$  is to be set on the resistor. This current is used to charge an internal capacitor (~20 pF). The switching frequency range of 100 kHz to 1 MHz is summarized in Table 8.  $R_{FSW}$  choice is obtained by using the following equation:

$$f_{FSW}[MHz] = \frac{1}{2*R_{SW}*20pF} = \frac{2.5 \times 10^{10}}{R_{SW}}$$

(18)

If the FSW pin is connected to VDD, the external programmability is turned off and the internal default frequency, tuned at 500 kHz, is enabled.

Table 12. R<sub>FSW</sub> choice

| R <sub>FSW</sub> [kW]  | F <sub>SW</sub> [kHz] |

|------------------------|-----------------------|

| 50 to 500              | 100 to 1000           |

| V <sub>FSW</sub> = VDD | 500                   |

To set "slave mode" configuration, the FSW pin must be shorted to ground (refer to Section 7.9 for details on Master/Slave working mode).

The internal clock is normally present to the SYNC pin with 180° phase shifting. If the device works as "MASTER" this clock is used to synchronize another device working as slave. On the contrary, if the device is set as "SLAVE" (the FSW pin shorted to ground) the SYNC pin is used as the input pin for an external clock signal, coming, for example, from another point of load used as master.

Here below, for example, a graph and the equation of the programmed frequency  $F_{SW}$  over the  $R_{FSW}$  resistor connected between the FSW pin and GND.

DS14737 - Rev 2 page 21/43

Figure 12. Programmed switching frequency R<sub>FSW</sub>

## 7.7 Startup and soft-start

The LEOPOL1 monitors the supply voltage on the VCC pin. Once the  $V_{CC}$  voltage is above the UVLO (undervoltage lockout) rising threshold, the device waits for enable pin (EN) assertion and then begins the soft-start

The LEOPOL1 enable pin has two thresholds in order to add flexibility to turn-on management:

- If the EN pin is kept below the PRE\_EN rising threshold (0.7 V typ. with 100 mV hysteresis), the IC is fully OFF and the current consumption is typically 400 μA.

- If the EN pin is forced above the UVLO\_EN rising threshold (1.24 V typ. with 200 mV hysteresis) the regulator starts switching after the SSDEL time elapses.

- If the EN pin is kept between the two above mentioned thresholds, the regulator's main blocks are turned ON (voltage reference, bias, and programming currents) and the LEOPOL1 is ready to turn on.

The filtering capacitors mounted between the functions programming pins (FSW, ILIM, and SLOPE) and GND, as shown in Figure 4, have a direct impact on the IC wake-up timing.

For this reason, to ensure that the soft-start sequence starts only when the functions programming pin voltage is stable, the soft-start delay has been added.

When the EN pin voltage level is above the PRE\_EN threshold, a DC current (100 µA typ.) is forced in the SSDEL pin, charging the soft-start delay capacitor connected between SSDEL and GND.

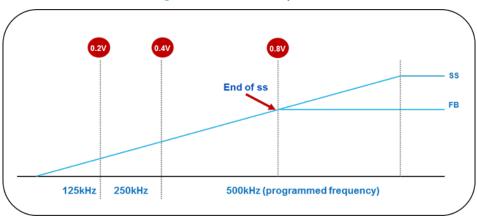

Once the input voltage supply is above the  $V_{CC\_UVLO}$  rising threshold (2.7 V typ.), the EN pin is forced above the UVLO\_EN threshold, and SSDEL has reached the threshold (1 V typ.), the LEOPOL1 can finally start switching. After SSDEL pin voltage reaches 1 V, the soft-start phase begins. According to the capacitor value on the SS pin, the internal loop reference slowly increases until 0.8 V, and capacity the Very voltage reaches the regulation

the internal loop reference slowly increases until 0.8 V, and consequently, the V<sub>OUT</sub> voltage reaches the regulation value.

During the startup phase (to prevent in-rush current when the  $V_{OUT}$  voltage is too low), two switching frequency changes are implemented. As long as the SS voltage value is below 0.2 V, the switching frequency is a quarter of the programmed frequency. When the SS value is between 0.2 V and 0.4 V, the switching frequency is half of the programmed frequency. After SS reaches 0.4 V, the switching frequency nominally reaches the programmed one.

DS14737 - Rev 2 page 22/43

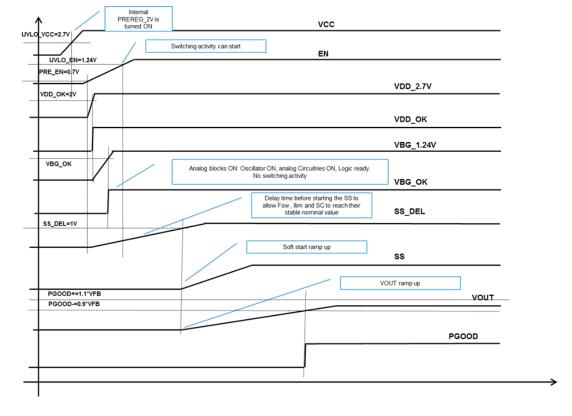

Figure 13. Soft-start sequence

The UVLO\_EN threshold can also be exploited in order to program a higher  $V_{IN}$  turn-on level. This feature is simply implemented by connecting the EN pin to the central tap of a resistor divider between  $V_{IN}$  and GND. When doing so, the programmed  $V_{IN}$  turn-on threshold is given by the UVLO\_EN threshold multiplied by the  $V_{IN}$  divider ratio.

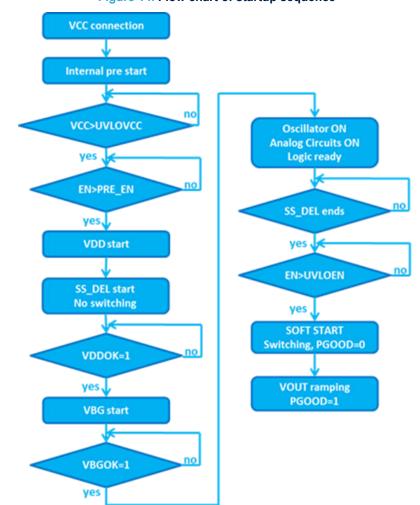

Here below the complete flow chart of the startup sequence.

Figure 14. Flow chart of startup sequence

DS14737 - Rev 2 page 23/43

Figure 15. LEOPOL1 startup sequence

The output soft-start function is achieved by ramping up the SS pin voltage with a constant slew rate dV/dt. When the switching section is enabled, the SS pin charges, at a constant current, the capacitor connected between the SS and GND pins.

The SS voltage is used as a reference of the switching regulator, and the output voltage of the converter follows the ramp of the SS voltage. When the SS pin voltage is higher than 0.8 V typ., the error amplifier switches to the internal 0.8 V reference and regulates the output voltage.

During the SS period and until voltage at pin SS reaches 0.9 V, OVP is masked, PGOOD is asserted low, and a negative current protection on the low-side MOS (LS\_OCP) is turned ON. If a negative current is detected during the soft-start phase or in very low load condition, the LS\_OCP is detecting this and the low-side is forced OFF. This function is also called "zero-crossing detection", because the current in the coil crosses the zero passing from positive (from GND versus the load) to negative (from the load versus GND).

When the feedback voltage enters the  $V_{FB} \pm 10\%$  Power Good window, the PGOOD pin is released (floating, PGOOD = high).

#### 7.8 Turn-off

When the enable signal is forced below the UVLO\_EN falling threshold (1. typ.), the PGOOD signal is pulled low, the device stops switching, and the power MOSFETs are set at high impedance.

The output capacitor is discharged through the output load.

If  $V_{CC}$  goes below the  $V_{CC\ UVLO}$  threshold, the device is switched off.

### 7.9 Synchronization

The LEOPOL1 can work in a two-synchronized ICs' configuration.

The clock synchronization is performed in case one IC is configured as master (FSW pin connected to GND through a switching frequency programming resistor) and the second one configured as slave (FSW pin shorted to GND). The main benefit of this configuration is the reduction of the input capacitor current ripple when the two devices work in an interleaved configuration.

DS14737 - Rev 2 page 24/43

Master

VIN

LEOPOL1

Slave

VIN

LEOPOL1

FSW

SYNC

SYNC

VOUT2

FSW

SYNC

Figure 16. Synchronized ICs

When two LEOPOL1s are synchronized together, they act as follows:

- Master IC

- The SYNC pin is configured as clock output. The device provides, on the SYNC pin, its internal switching clock information with a 180° time shifting.

- Slave IC

- The SYNC pin is configured as clock input. The device uses the clock information received on the SYNC pin to synchronize its internal switching clock.

Care must be taken to properly route the SYNC trace on the application PCB to avoid coupling with the power switching traces (for example, LX) that might generate jitter.

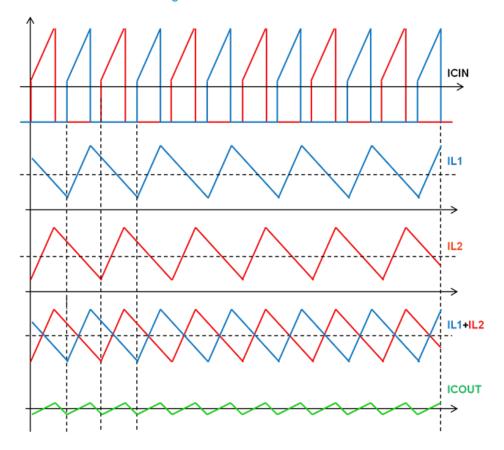

## 7.10 Interleaving

The LEOPOL1 can work in a two-interleaved ICs' configuration, in order to provide up to 14 A maximum load current.

IC interleaving (or parallelization) is performed in case one IC is configured as master (FSW pin connected to GND through a switching frequency programming resistor RFSW) and the second one is configured as slave (FSW pin forced to a voltage lower than 0.1 V). The two SYNC pins must be shorted together and the compensation network must be shared by the two ICs.

The main benefits of this configuration are the doubled available output current and the reduction of the output and input capacitor current ripple.

DS14737 - Rev 2 page 25/43

Master VIN LEOPOL1 **VOUT**  $\overline{m}$ LX **FSW COMP** SYNC **Slave** φ VIN **COMP LEOPOL1** LX  $\varphi$ m**FSW SYNC**

Figure 17. Interleaved ICs

When two LEOPOL1s are interleaved, they act as follows:

- Master IC

- The SYNC pin is configured as clock output. The device provides, on the SYNC pin, its internal switching clock information with a 180° time shifting.

- Slave IC

- The SYNC pin is configured as clock input. The device uses the clock information received on the SYNC pin to synchronize its internal switching clock.

An example of the typical inductor and input/output currents waveforms is shown in Figure 18.

DS14737 - Rev 2 page 26/43

Figure 18. Interleaved ICs current

## 7.11 Fault management

The LEOPOL1 provides the following input and output voltage protections and monitoring features.

### 7.11.1 Power Good (PGOOD)

The Power Good pin (PGOOD) is an open drain output that is left floating if the output voltage is within  $\pm$  10% of the regulation window.

During startup, turn-off, and fault detection the PGOOD pin is forced low.

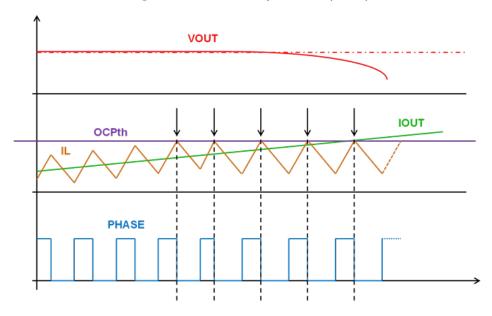

### 7.11.2 Overcurrent protection (OCP)

The LEOPOL1 is able to monitor, cycle-by-cycle, the high-side MOS current. If the measured current reaches the first level overcurrent limit threshold (I<sub>LIM1</sub>), the high-side MOS is immediately turned off and the low-side MOS is turned-on, until a new clock pulse is generated. The PGOOD signal is not affected and it stays in high impedance (high level).

DS14737 - Rev 2 page 27/43

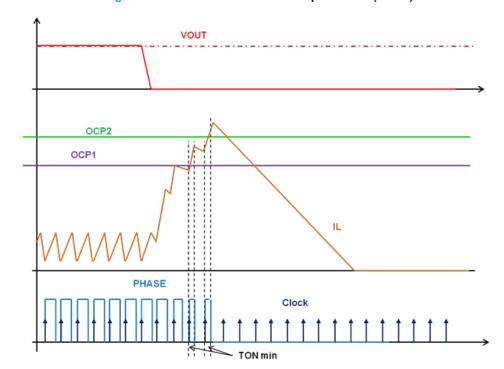

Figure 19. Peak current protection (OCP1)

The peak current protection described above can meet some limitations in the case of an output voltage short versus GND.

In this case, the minimum high-side MOS on-time required for a precise current sensing could lead to a current increase above the OCP1 limit. In fact, since in this case, the output voltage is almost zero, the inductor current cannot decrease during the low-side MOS on-time.

To overcome this problem, the LEOPOL1 implements a second order overcurrent threshold OCP2 (refer to Figure 20). If the sensed high-side MOS current reaches the second level threshold (ILIM2), the switching regulator immediately turns off and the MOSFETs are set at high impedance. The PGOOD pin is asserted low and the SS capacitor is discharged.

Refer to Section 7.14 Alarm description for more details about alarms/faults handling.

Figure 20. Second level overcurrent protection (OCP2)