# STACF01A, STACF01B

# Datasheet

# Active clamp flyback controller

# STACFOIA

| Product statu | s link |

|---------------|--------|

| STACF01       | A      |

| STACF01       | В      |

# **Features**

- Non-complementary control of active clamp flyback converter

- Multimode operation optimizes efficiency over a very wide load range

- Up to 500 kHz operating frequency with programmable deadtime

- Automatic reverse current control for ZVS of low-side switch

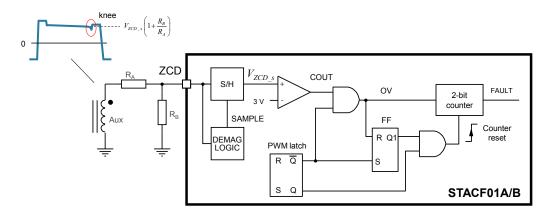

- ZCD circuit for demagnetization instant detection and OVP setting

- Embedded high-voltage startup and active x-cap discharge circuit

- Integrated buck-boost regulator for wide output voltage range

- Very low quiescent current enables ultra-low no-load input power

- Full set of protection features

- Interface with PFC controller

- Dual low-side driver and enable for easy pairing with MasterGaN family, other types of GaN power IC, or half-bridge driver IC

# **Applications**

• High power density and USB PD chargers & adapters based on GaN HEMTS

# **Description**

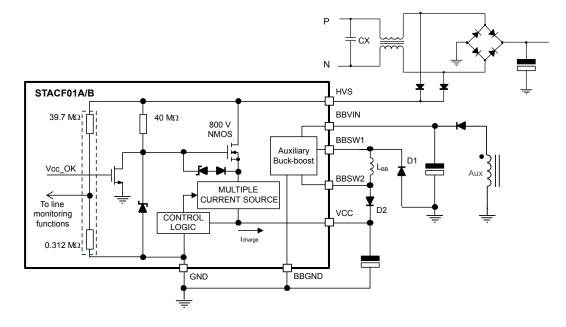

The STACF01A and STACF01B ICs drive and control active clamp flyback converters with non-complementary driving of the active clamp (high-side, HS) switch. It is specifically intended for high performance AC-DC adapters with GaN HEMTS rated up to 100 W and beyond, which are aimed at high efficiency as well as high power density.

The ICs seamlessly change operating mode with loading conditions to optimize efficiency under an extremely wide range of loads: variable frequency with frequency foldback at heavy-medium load, bottom-clamped, load-proportional frequency at light load, burst mode at very light, and no-load.

An automatic adjustment mechanism ensures that the reverse primary current needed to achieve ZVS is properly set for any input/output voltage combination.

This ICs can achieve output voltage regulation from the secondary side via an optocoupler-based feedback.

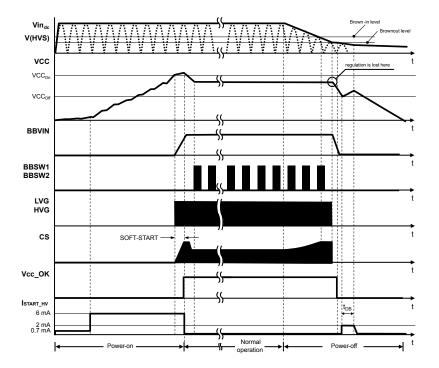

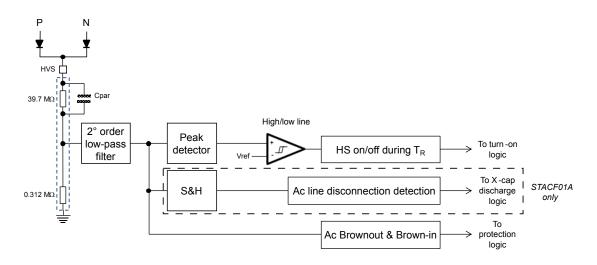

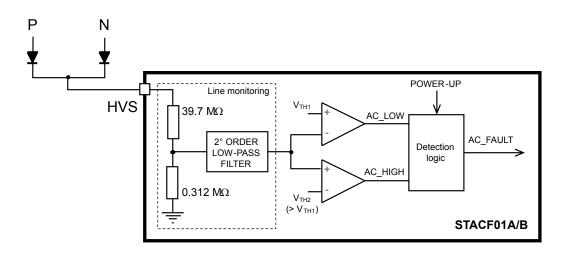

The ICs are provided with an embedded high-voltage startup circuit that also implements the line voltage monitoring system. The STACF01A also discharges the X capacitors when the converter gets disconnected from the AC power line. The STACF01B is intended for use with DC input, like SMPS with PFC in front or supplied by a DC bus.

The ICs incorporate two low-side low-power drivers intended to drive the inputs of an external high-voltage half-bridge driver ICs or an SiP such as one of the MasterGaN families.

It also provides an extensive set of protection features against primary and secondary side faults (two-level overcurrent, overpower, overload, short circuit, brownout, output overvoltage). A general protection input (active low latch type and active high autorestart) helps implement an external OTP, an external input OVP, or a general-purpose protection.

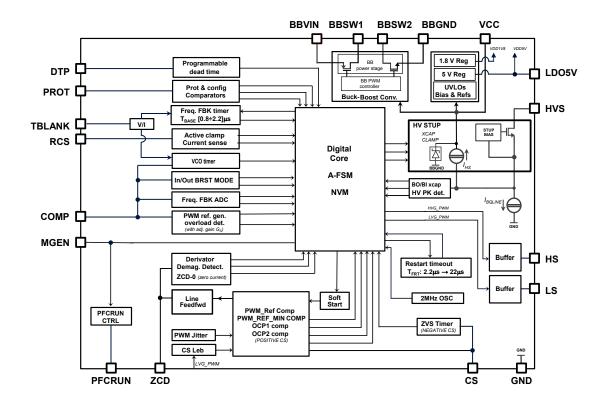

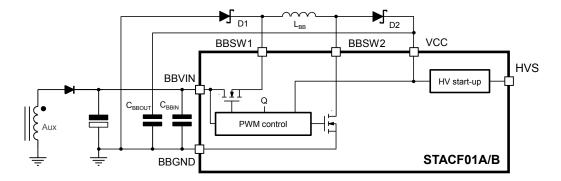

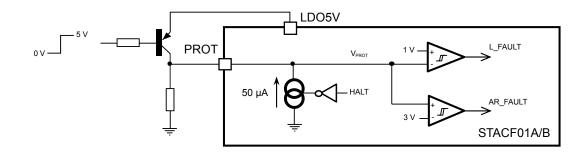

# 1 Block diagram

57

# Figure 1. Block diagram

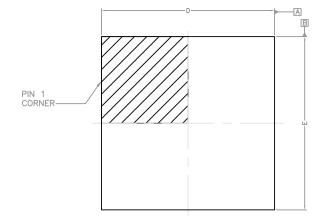

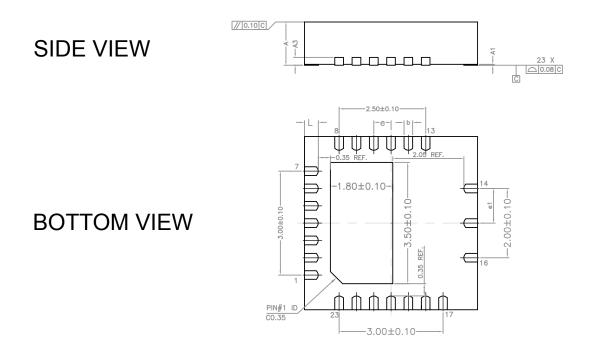

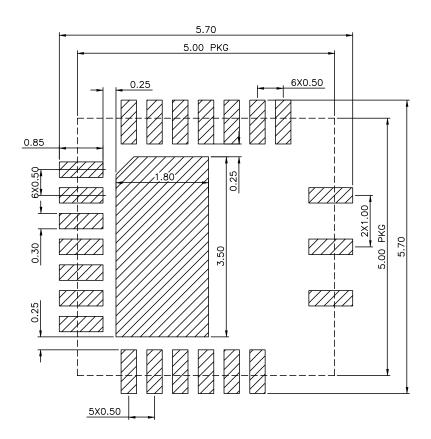

| Table 1. Device information | ation |

|-----------------------------|-------|

|-----------------------------|-------|

| Order code | X-cap discharge | Marking  | Package | Packing       |

|------------|-----------------|----------|---------|---------------|

| STACF01A   | YES             | STACF01A | QFN 5x5 | Tray          |

| STACF01ATR | YES             | STACF01A | QFN 5x5 | Tape and Reel |

| STACF01B   | NO              | STACF01B | QFN 5x5 | Tray          |

| STACF01BTR | NO              | STACF01B | QFN 5x5 | Tape and Reel |

# 2 Max ratings, recommended conditions, ESD immunity levels, thermal data

| Symbol              | Pin               | Parameter                                                         | Min.                    | Max.                                    | Unit |

|---------------------|-------------------|-------------------------------------------------------------------|-------------------------|-----------------------------------------|------|

| V <sub>HVS</sub>    | 15                | High-voltage<br>startup voltage                                   | -0.6 (1)                | 800                                     | V    |

| I <sub>HVS</sub>    | 15                | High-voltage<br>startup source<br>current                         |                         | Self-limited                            | mA   |

| I <sub>VCC</sub>    | 9                 | VCC input current                                                 | 0                       | 25                                      | mA   |

| V <sub>VCC</sub>    | 9                 | IC supply voltage<br>(I <sub>VCC</sub> < 25 mA)                   | -0.3                    | Self-limited                            | V    |

| I <sub>LDO5V</sub>  | 7                 | Regulator output source current                                   | 0                       | Self-limited                            | mA   |

| V <sub>BBVIN</sub>  | 6                 | Buck-boost input voltage                                          | -0.3                    | 30                                      | V    |

| V <sub>BBSW1</sub>  | 5                 | Switching node voltage                                            | -0.8                    | V <sub>BBVIN</sub> + 0.3 <sup>(2)</sup> | V    |

| V <sub>BBSW2</sub>  | 3                 | Switching node voltage                                            | -0.3 (2)                | V <sub>VCC</sub> + 7                    | V    |

| I <sub>ZCD</sub>    | 22                | Zero current<br>detector sink/<br>source current                  | 0                       | 3                                       | mA   |

| V <sub>ZCD</sub>    | 22                | Zero current<br>detector voltage ( <br>I <sub>ZCD</sub>   < 3 mA) | Self-limited            | Self-limited                            | V    |

| V <sub>LS</sub>     | 11                | Low-side PWM<br>drive voltage                                     | -0.3                    | V <sub>LDO5V</sub>                      | V    |

| V <sub>HS</sub>     | 12                | High-side PWM<br>drive voltage                                    | -0.3                    | V <sub>LDO5V</sub>                      | V    |

| V <sub>RCS</sub>    | 20                | Reverse current sensing voltage                                   | V <sub>LDO5V</sub> –7.5 | 3                                       | V    |

|                     | 1, 18, 19, 21, 23 | Analog inputs                                                     | -0.3                    | 3.6                                     | V    |

| V <sub>PFCRUN</sub> | 2                 | Analog output<br>voltage                                          | -0.3                    | V <sub>VCC</sub> + 0.3                  | V    |

| V <sub>MGEN</sub>   | 10                | Analog output<br>voltage                                          | -0.3                    | V <sub>LDO5V</sub> + 0.3                | V    |

| Tj                  |                   | Junction<br>temperature<br>operating range                        | -40                     | 150                                     | °C   |

| T <sub>stg</sub>    |                   | Storage temperature                                               | -55                     | 150                                     | °C   |

# Table 2. Absolute maximum ratings

1. This is a DC value. The application may experience a lower voltage for short pulses at system startup at mains zerocrossing. These undershoots must be limited to a few hundred ns.

2. These are DC values. Pulsed regime must be evaluated during buck-boost operation to analyze impact and set limits for overshoots of tenth of ns. All voltages are referred to GND = BBGND.

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions. Exposure to any of the absolute maximum rating conditions for extended periods may affect device reliability and lifetime. Max ratings, recommended conditions, ESD immunity levels, thermal data

| Symbol              | Pin               | Parameter                                           | Min.                   | Max.                   | Unit |

|---------------------|-------------------|-----------------------------------------------------|------------------------|------------------------|------|

| V <sub>HVS</sub>    | 15                | High-voltage<br>startup voltage                     | -0.6                   | 450                    | V    |

| V <sub>BBVIN</sub>  | 6                 | Buck-boost input voltage                            | 0                      | 27                     | V    |

| I <sub>BB</sub>     | 9                 | Total buck-boost<br>output current (int.<br>+ ext.) | 0                      | 20                     | mA   |

| V <sub>BBSW1</sub>  | 5                 | Switching node voltage                              | -0.5                   | V <sub>BBVIN</sub>     | V    |

| V <sub>BBSW2</sub>  | 3                 | Switching node voltage                              | 0                      | V <sub>VCC</sub> + 0.5 | V    |

| IZCD                | 22                | Zero current<br>detector sink/<br>source current    | 0                      | 2.5                    | mA   |

| V <sub>ZCD</sub>    | 22                | Zero current detector voltage                       | -0.4                   | 4.6                    | V    |

| V <sub>RCS</sub>    | 21                | Reverse current sensing                             | V <sub>LDO5V</sub> – 7 | 2.5                    | V    |

|                     | 1, 18, 19, 21, 23 | Analog inputs                                       | 0                      | 3.3                    | V    |

| V <sub>PFCRUN</sub> | 2                 | Analog output<br>voltage                            | 0                      | V <sub>VCC</sub>       | V    |

| V <sub>MGEN</sub>   | 10                | Analog output<br>voltage                            | 0                      | V <sub>LDO5</sub> V    | V    |

#### Table 3. Recommended operating conditions

Operating within the "recommended operating conditions", ensures performance and electrical parameter degradation remain within device specifications. Unless otherwise specified, these conditions are intended to be continuously applied.

# Table 4. ESD immunity levels

| Mode | Pin               | Reference<br>specification | Value | Unit |

|------|-------------------|----------------------------|-------|------|

| HBM  | 1 to 12, 19 to 24 | According to JS001         | ± 2   | kV   |

| HBM  | 15                | According to JS001         | ± 1   | kV   |

| CDM  | All               | According to JES002        | ± 500 | V    |

# Table 5. Thermal data

| Symbol              | Parameter                                                     | Value | Unit |

|---------------------|---------------------------------------------------------------|-------|------|

| Θ <sub>th j-a</sub> | Thermal resistance, Junction-to-ambient $^{\left( 1\right) }$ | 45    | °C/W |

| Ψ <sub>th j-c</sub> | Thermal resistance, Junction-to-case                          | 3     | °C/W |

1. Obtained from simulations using JEDEC 1S1P (2 layers, 70 um Cu) FR4 PCB with thermal land and vias.

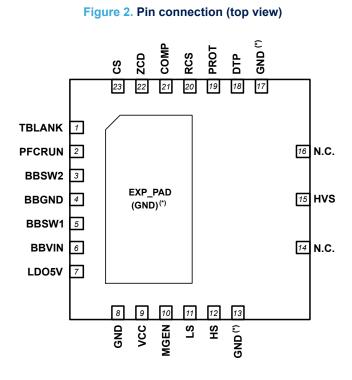

# **3** Pin connections and functions

57

# Table 6. Pin functions

| No. | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TBLANK | Frequency foldback programming input. Frequency foldback is achieved by inserting a blanking time after the turn-off of the LS drive. This blanking time increases as the load is reduced, assuming discrete values that are a multiple of a preset time interval. A resistor connected between this pin and GND sets the duration of this preset time interval in a range that goes from 0.8 to 2.2 $\mu$ s with 0.2 $\mu$ s steps.                                                                                                                                                       |

| 2   | PFCRUN | PFC stage control output. This pin is intended to enable/disable the PFC controller IC in systems comprising a PFC pre-regulator. The pin normally features a high impedance; an internal switch is closed, and the pin is pulled to ground, when the voltage at pin COMP is lower than a threshold (light load), whenever the IC is shut down by a protection function and during UVLO. If not used, the pin is left floating.                                                                                                                                                            |

| 3   | BBSW2  | Drain connection of the low-side switch of the auxiliary buck-boost converter. The anode of the steering diode and one terminal of the buck-boost inductor are connected externally to this pin. A 30 V rated Schottky-type in SOD 123 package or similar is recommended as the steering diode. The buck-boost inductor (10 $\mu$ H inductance is recommended) should have less than 1 W winding resistance to enable the converter to carry sufficient power when its input voltage is at the lowest end.                                                                                 |

| 4   | BBGND  | Auxiliary buck-boost converter ground return. It internally connects the source of the low-<br>side switch of the buck-boost and externally both the anode of the freewheeling diode and<br>the (-) terminal of both the input bypass VBBIN capacitor and the output bypass VCC<br>capacitor. A 30 V rated Schottky-type in SOD 123 package or similar is recommended as<br>the freewheeling diode.<br>This ground connection carries pulsed currents that should be kept separate from any<br>bias current return. No bias component should be tied to the PCB track leading to this pin. |

| 5   | BBSW1  | Source connection of the high-side switch of the auxiliary buck-boost converter. The cathode of the freewheeling diode and the other terminal of the buck-boost inductor are connected externally to this pin.                                                                                                                                                                                                                                                                                                                                                                             |

| No.    | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | BBVIN | Input pin of the auxiliary buck-boost converter. The pin internally connects the drain of the high-side switch and is externally connected to the DC voltage generated by the auxiliary winding of the flyback transformer through a diode and a reservoir capacitor. In addition to this capacitor (most likely an electrolytic one) that is located close to the diode and the winding, a few $\mu$ F ceramic bypass capacitor to BBGND is connected as close as possible to the pins. This is needed to keep the pulsed currents provided by the auxiliary buckboost converter confined within the switching loop of the converter itself. The voltage on the pin is internally monitored and if it is lower than a threshold, the buckboost converter is disabled. Therefore, in applications where the buck-boost converter is unnecessary this pin can simply be tied to BBGND along with BBSW1 and BBSW2, and the auxiliary DC voltage brought directly to the VCC pin.                                                                                                                                                                                                                                                             |

| 7      | LDO5V | This pin is the output of the 5 V internal regulator that supplies the logic circuits of the IC. It requires a typical 47 nF ceramic bypass capacitor to the GND pin. The internal regulator can supply a limited external load current (not exceeding 1 mA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8      | GND   | IC signal ground. Current return for the bias current of the IC. All the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9      | VCC   | Supply voltage of the IC and output of the embedded auxiliary buck-boost converter. A capacitor to GND, whose value depends only on application requirements, serves as an energy buffer to sustain IC operation. A few $\mu$ F ceramic bypass capacitor to BBGND, connected as close as possible to the pins, is needed to keep the pulsed currents provided by the auxiliary buck-boost converter confined within the switching loop of the converter itself. The cathode of the steering diode is connected to this pin too. An internal undervoltage lockout (UVLO) function enables the operation of the control circuit when the voltage on the pin reaches a certain threshold and inhibits the operation when it falls below a lower threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10     | MGEN  | Enable/disable control output. This pin is intended to drive the enable/disable control input of an external high-voltage half-bridge driver IC or SiP such as the MASTERGAN®. While the STACF01A/B are switching, this pin provides a 5 V DC level, while providing a 0 V level whenever the IC is not switching (while in UVLO, after a fault or during the idle periods in burst mode operation). In this way, the quiescent consumption of the external driver or SiP can be reduced to help meet even the most severe light-load or no-load energy efficiency requirements. Note that the pin goes high about 500 us before the IC starts switching from UVLO, and about 16 us before restarting switching when exiting from a fault or while operating in burst mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11     | LS    | PWM output signal is used to control the gate of the low-side switch through an external half-bridge driver or SiP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12     | HS    | PWM output signal is used to control the gate of the high-side switch through an external half-bridge driver or SiP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13,17  | GND   | These pins are connected to the controller's ground plane and substrate. Do not use as signal or power ground return. They can be connected to GND or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14, 16 | N.C.  | High-voltage spacers. These pins are not internally connected to isolate the high-voltage sections and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15     | HVS   | High-voltage startup generator, AC voltage sensing input, X-cap discharger (STACF01A only). The pin, able to withstand 800 V, is to be connected to the AC side of the input bridge via a pair of diodes (1N400x type) to sense the AC input voltage. Their anodes are connected to the line and neutral conductors, while both cathodes are connected to the pin. It is recommended to connect the anodes just at the input of the rectifier bridge. If the voltage on the pin is higher than 15 V, an internal pull-up circuit charges the capacitor connected between the pin VCC and GND. Initially, the current is low for safety in case of a shorted VCC, and then it goes to the normal level as far as the VCC pin reaches the startup threshold. To reduce the hold-up requirement on the VCC cap, the generator is turned off at the end of the soft-start time. The generator is re-enabled when the voltage on the VCC pin falls below the UVLO threshold. In case the IC stops operating after a fault, the VCC cycles between the startup threshold and the UVLO threshold; the current is reduced to keep power dissipation low. The pin is also used to sense the AC voltage, which is used by the AC brownout functions. |

| No. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      | STACF01A only:<br>An internal logic circuit detects that the unit has been disconnected from the power line<br>and activates the high-voltage startup generator to discharge the X-capacitors of the EMI<br>filter to a safe level. This allows the unit to meet safety regulations (such as IEC 62368-1)<br>without using the traditional discharge resistor in parallel to the X-capacitors, thus saving<br>the associated power losses and enabling ultra-low consumption in standby conditions.        |

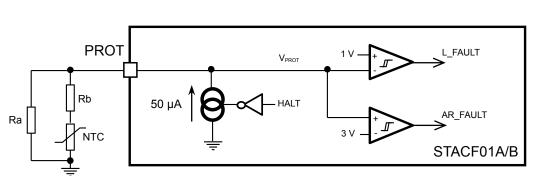

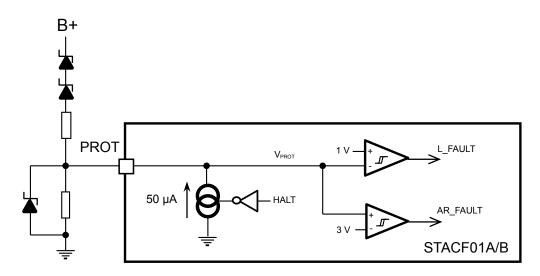

| 18  | DTP  | Deadtime programming. A resistor connected between this pin and GND sets the deadtime from HS drive going low to LS drive going high. It also sets the deadtime from the LS drive going low to the first HS drive going high at half the value of the other transition.                                                                                                                                                                                                                                    |

|     |      | General purpose external protection input. This pin is internally pulled up by a 50 $\mu$ A current generator. For normal operation, the external circuit must keep the voltage on the pin between 1 and 3 V.                                                                                                                                                                                                                                                                                              |

| 19  | PROT | When the voltage on this pin is forced below a set threshold (= 1 V), the controller is latched off. The unit needs to be disconnected from the power line to restart. An NTC thermistor can be connected between this pin to GND for overtemperature protection.                                                                                                                                                                                                                                          |

|     |      | When the voltage is allowed to reach a set threshold (= 3 V), the controller is stopped. It restarts immediately as the voltage falls below the threshold (minus hysteresis), going through a soft-start cycle. Typically, this function can be used to implement an input overvoltage protection.<br>A small bypass capacitor to GND (≤ 330 pF) might be useful to get a clean bias voltage in noisy environments.                                                                                        |

|     |      | General purpose external protection input. This pin is internally pulled up by a 50 $\mu$ A current generator. For normal operation, the external circuit must keep the voltage on the pin between 1 and 3 V.                                                                                                                                                                                                                                                                                              |

| 20  | RCS  | When the voltage on this pin is forced below a set threshold (= 1 V), the controller is latched off. The unit needs to be disconnected from the power line to restart. An NTC thermistor can be connected between this pin to GND for overtemperature protection.                                                                                                                                                                                                                                          |

|     |      | When the voltage is allowed to reach a set threshold (= 3 V), the controller is stopped. It restarts immediately as the voltage falls below the threshold (minus hysteresis), going through a soft-start cycle. Typically, this function can be used to implement an input overvoltage protection.<br>A small bypass capacitor to GND (≤ 330 pF) might be useful to get a clean bias voltage in noisy environments.                                                                                        |

| 21  | COMP | Secondary side feedback input pin. It is used for output voltage regulation. This pin is connected to the transistor of the optocoupler; internally it is pulled up to a voltage reference. It is bypassed by a low value capacitor to GND. The error voltage at this node is also used internally for determining the various operating modes of the IC.                                                                                                                                                  |

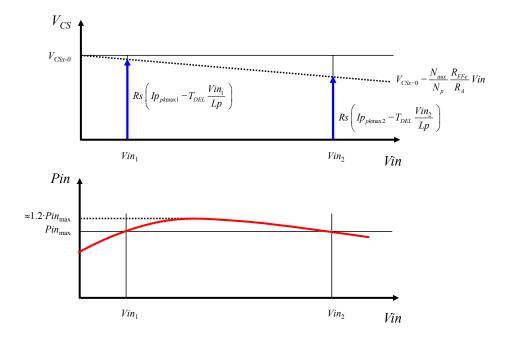

|     |      | Multifunction pin. This pin senses a sample of signal derived from an auxiliary winding used for generating the IC bias power and to perform multiple functions.                                                                                                                                                                                                                                                                                                                                           |

|     |      | The positive signal in flyback mode is sampled and used for changing the PWM gain depending on the output voltage in variable output voltage applications (gain is higher at a high output voltage, lower at a low output voltage). This voltage information is used for overvoltage protection (OVP) too. This protection is an autorecovery type.                                                                                                                                                        |

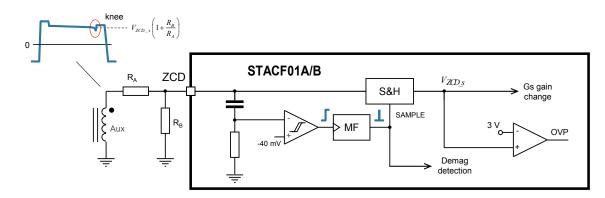

| 22  | ZCD  | The negative signal during the energizing period of the transformer is used to predict the input voltage for internal line feedforward. This signal is used to compensate both the propagation delay at turn-off and adjust the resulting cycle-by-cycle overcurrent setpoint. In both cases the objective is to minimize the dependence of the maximum deliverable power and of the light-load level for burst mode operation on the input voltage.                                                       |

|     |      | The onset of the drain ringing after transformer demagnetization, which determines either the second turn-on of the high-side switch or the start of the blanking period before turning on the high-side switch (frequency foldback), is also detected through this pin. Another important functionality of the ZCD pin is to prevent CCM operation. Though DCM operation is inherent in case of normal operation, it might not be in case of operation under severe overload or short-circuit conditions. |

| 23  | CS   | Current sense pin. The signal Vcs at this pin is compared with the scaled error signal for current mode control operation. An internal leading-edge blanking circuit helps achieve clean operation.                                                                                                                                                                                                                                                                                                        |

| No. | Name             | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                  | A second comparator referred to a fixed level determines the maximum peak current in each switching cycle (overcurrent protection). At startup the overcurrent level reaches the final value starting from zero in 8 equal steps lasting 1 ms each (soft-start).                                                                                                                                                       |

|     |                  | A third comparator referred to a fixed level higher than that of the cycle-by-cycle overcurrent protection shuts down the IC in case of transformer saturation or secondary diode short-circuit. This protection is an autorestart type. A logic circuit improves sensitivity to temporary disturbances.                                                                                                               |

|     |                  | The signal Vcs is also used by the self-adjustment mechanisms that determines the duration of the reverse current conduction (that is, the on-time of the high-side switch at the end of a switching cycle). During this period, the reverse current builds up in the primary winding by drawing energy from the clamp capacitor up to a level adequate to achieve ZVS for the low-side switch at its next turn-on.    |

|     |                  | A resistance connected from this pin to the current sense resistor enables the user to tune the self-adjustment mechanism to achieve ZVS (or get close to it, if preferred) with just the right amount of reverse current.<br>The duration of the on-time of the high-side switch just after the turn-off of the low-side one is set at 50% of the reverse current conduction interval at low line (67% at high line). |

| 24  | EXP_PAD<br>(GND) | Exposed pad. Internally connected to the controller's ground plane and substrate. It must be connected directly to ground and well soldered to an adequate PCB copper area to facilitate heat dissipation.                                                                                                                                                                                                             |

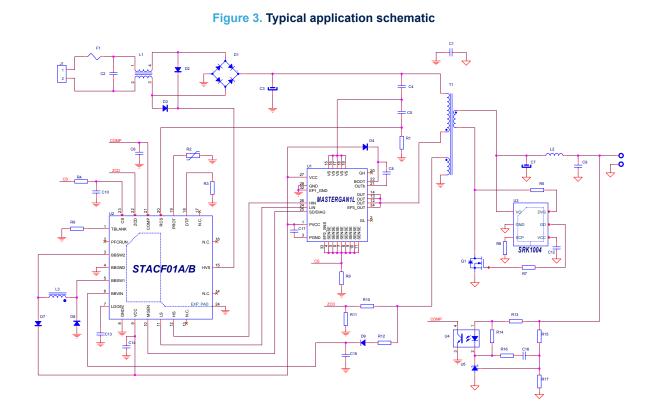

# 4 Typical application schematic

# 5 Electrical characteristics

T<sub>j</sub> = -40 to +125 °C, V<sub>BBVIN</sub> = 12 V, VCC regulated,  $C_{5V\_LDO}$  = 47 nF,  $C_{HS}$  =  $C_{LS}$  = 20 pF, unless otherwise specified.

| Symbol                                           | Parameter                                              | Test condition                                                       | Min.      | Тур. | Max. | Unit    |

|--------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|-----------|------|------|---------|

| supply volta                                     | age (VCC)                                              |                                                                      |           |      |      |         |

| VCC                                              | Operating range                                        | After device<br>turns on,<br>V <sub>BBVIN</sub> = gnd                | 5.25      |      | 6.64 | V       |

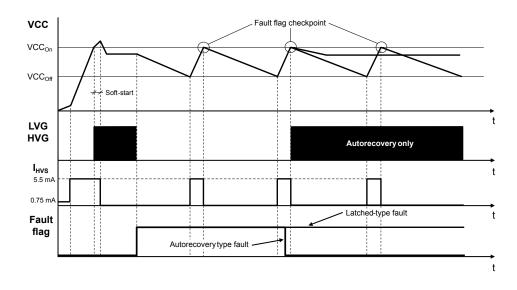

| VCC <sub>On</sub>                                | Turn-on<br>threshold                                   | Voltage rising <sup>(1)</sup>                                        | 6         | 6.3  | 6.9  | V       |

| VCC <sub>Off</sub>                               | Turn-off<br>threshold                                  | Voltage falling <sup>(1)</sup>                                       | 4.6       | 4.9  | 5.2  | V       |

| VCCZ                                             | Zener voltage                                          | I <sub>VCC</sub> = 20 mA                                             | 6.64      | 6.9  | 7.1  | V       |

| upply curren                                     | t (VCC)                                                |                                                                      |           | •    | •    | 1       |

| I <sub>Q_UV</sub>                                | Startup current                                        | Before device<br>turns on, VCC =<br>VCC <sub>On</sub> - 0.2 V        |           | 0.4  |      | mA      |

| I <sub>Q_BURST</sub>                             | Quiescent current                                      | Idle during burst<br>mode, $V_{COMP}$ =<br>1 V, T <sub>j</sub> =25°C |           | 0.85 | 1    | mA      |

| I <sub>Q_OP</sub>                                | Operating current                                      | Device on,<br>switching                                              |           | 3    | TBD  | mA      |

| I <sub>Q_FAULT</sub>                             | Residual consumption                                   | After protection tripping                                            |           | 0.8  |      | mA      |

| uxiliary buck                                    | -boost converter (E                                    | BVIN, BBSW1, BB                                                      | SW2, VCC) |      |      |         |

| V <sub>BBVIN</sub>                               | Operating range                                        | After being enabling                                                 | 2.4       |      | 27   | V       |

| $V_{\text{BBVIN}\_\text{On}}$                    | Enable<br>threshold                                    | Voltage rising <sup>(1)</sup>                                        | 2.4       | 2.5  | 2.6  | V       |

| $V_{\text{BBVIN}_{\text{Off}}}$                  | Disable<br>threshold                                   | Voltage falling <sup>(1)</sup>                                       | 2.2       | 2.3  | 2.4  | V       |

| VCC <sub>reg</sub>                               | Regulated output voltage                               | $I_{VCC}$ = 10 mA,<br>$V_{BBVIN}$ 2.5 V <sup>(1)</sup>               | 6.0       | 6.25 | 6.5  | V       |

| VCC <sub>res</sub>                               | Restart<br>threshold during<br>burst mode<br>operation | (1)                                                                  | 5.15      | 5.4  | 5.7  | V       |

|                                                  | Low-side switch on-resistance                          |                                                                      |           | 2    | 3.5  | Ω       |

| R <sub>DS(on)-HS</sub>                           |                                                        |                                                                      |           | 1.3  | 2.5  | Ω       |

| R <sub>DS(on)-HS</sub><br>R <sub>DS(on)-LS</sub> | Low-side switch on-resistance                          |                                                                      |           | 1.0  |      |         |

|                                                  |                                                        |                                                                      | 0.15      | 0.2  | 0.28 | A       |

| R <sub>DS(on)-LS</sub>                           | on-resistance<br>Peak current                          | V <sub>BBVIN</sub> = 4 V                                             | 0.15      |      | 0.28 | A<br>us |

# Table 7. Electrical characteristics

| Symbol                 | Parameter                                                       | Test condition                                                                                   | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>HVS_BD</sub>    | Breakdown<br>voltage                                            | I <sub>HVS</sub> < 100 μΑ                                                                        | 800  |      |      | V    |

| V <sub>HVS_start</sub> | Start voltage (rising)                                          | VCC can reach<br>VCC <sub>On</sub>                                                               | 10   |      | 21   | V    |

| 1                      | On-state VCC charge current                                     | V <sub>HVS</sub> > V <sub>HVS</sub><br><sub>start,</sub> VCC = 0.5<br>V @ T <sub>j</sub> = 25 °C |      | 0.75 |      | mA   |

| HVS_CHARGE             |                                                                 | V <sub>HVS</sub> > V <sub>HVS</sub><br><sub>start,</sub> VCC = 2.8<br>V @ T <sub>j</sub> = 25 °C |      | 5.5  |      | IIIA |

| I <sub>HVS_SINK</sub>  | Sink current (to GND)                                           | VCC falling during brownout                                                                      | 250  | 360  | 470  | μΑ   |

| I <sub>HVS_OFF</sub>   | Off-state residual current                                      | V <sub>HVS</sub> = 400 V,<br>T <sub>j</sub> = 25 °C                                              |      | 16   |      | μΑ   |

| C-capacitor dis        | charge function (H                                              | IVS) - STACF01A                                                                                  | only |      | 1    | 1    |

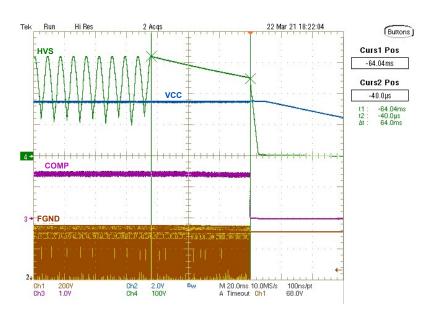

| T <sub>DET</sub>       | Line<br>disconnection<br>detection<br>timeout                   |                                                                                                  |      | 64   |      | ms   |

| V <sub>HVSmin</sub>    | Residual voltage                                                | After discharge is over                                                                          |      |      | 45   | V    |

| I <sub>HVS_DIS</sub>   | Discharge<br>current                                            | V <sub>HVS</sub> > V <sub>HVSmin</sub>                                                           | 4    |      |      | mA   |

| INE monitorin          | g functions (HVS)                                               | · ·                                                                                              |      |      | ,    |      |

| V <sub>HVSpk_BO</sub>  | Brownout<br>threshold                                           | Voltage falling<br>(peak) <sup>(2)</sup>                                                         | 81   | 95   | 110  | V    |

| V <sub>HVSpk_</sub> BI | Brown-in<br>threshold                                           | Voltage rising (peak) <sup>(2)</sup>                                                             | 107  | 116  | 122  | V    |

|                        | Debounce time                                                   | Brown-in                                                                                         |      | 40   |      |      |

| t <sub>DB</sub>        |                                                                 | Brown-in                                                                                         |      | 1    |      | ms   |

| V <sub>HVSpk_HL</sub>  | High line detect threshold                                      | Voltage rising (peak) <sup>(2)</sup>                                                             | 218  | 234  | 248  | V    |

| V <sub>HVSpk_LL</sub>  | High line detect threshold                                      | Voltage falling<br>(peak) <sup>(2)</sup>                                                         | 184  | 200  | 212  | V    |

| Deadtime prog          | ramming (DTP)                                                   | · ,                                                                                              |      |      | ,    |      |

| V <sub>DTP</sub>       | Voltage<br>reference                                            | $R_{DTP} \ge 10 \ k\Omega^{(2)}$                                                                 |      | 0.6  |      | V    |

| T <sub>D</sub>         | Programming range                                               | From LS $\downarrow$ to<br>HS $\uparrow$ and from<br>HS $\downarrow$ to LS $\uparrow$            | 50   |      | 350  | ns   |

| Τ <sub>D</sub>         | Programmed<br>value from LS ↓<br>to HS ↑                        | R <sub>DTP</sub> = 21 kW                                                                         |      | 105  |      | ns   |

| Current sense i        | nput (CS)                                                       |                                                                                                  |      |      |      |      |

| I <sub>CS</sub>        | Bias current                                                    |                                                                                                  |      |      | 1    | μA   |

| t <sub>d(H-L)</sub>    | Delay to output<br>(from Vcs <sub>ref</sub><br>hitting to LS ↓) | No load on LS, $dV_{CS}/dt = 0.4 V/$ µs                                                          |      |      | 80   | ns   |

| T <sub>LEB</sub>       | Leading edge<br>blanking after<br>LS turn-on                    | During soft-start<br>& bursts                                                                    | 120  | 150  | 200  | ns   |

| Symbol                                 | Parameter                                    | Test condition                                                          | Min.  | Тур.  | Max.  | Unit |

|----------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|------|

| T <sub>LEB</sub>                       | Leading edge<br>blanking after<br>LS turn-on | After soft-start<br>end                                                 | 40    | 50    | 75    | ns   |

| V <sub>CSx-0</sub>                     | Cycle-by-cycle<br>OCP level                  | $V_{COMP} =$<br>$V_{COMPhi}, I_{ZCD} =$<br>$0^{(2)}$                    | 0.71  | 0.75  | 0.79  | V    |

|                                        | Overload                                     | SampledV(ZCD<br>)≥ V <sub>ZCD_HGs</sub> <sup>(2)</sup>                  | 0.76  | 0.8   | 0.84  | V    |

| V <sub>CSref_OL</sub>                  | threshold<br>(voltage rising)                | SampledV(ZCD<br>)≤ V <sub>ZCD_LGs</sub> <sup>(2)</sup>                  | 0.475 | 0.5   | 0.525 | V    |

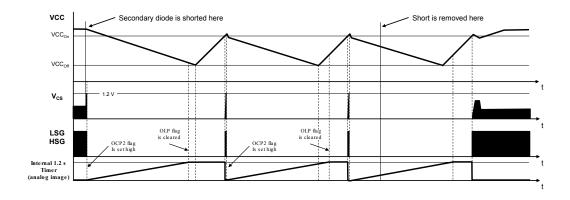

| V <sub>CS_OCP2</sub>                   | 2 <sup>nd</sup> OCP level                    | (2)                                                                     | 1.1   | 1.2   | 1.3   | V    |

| T <sub>Onmax</sub>                     | Maximum on-<br>time                          |                                                                         | 6     | 8     | 10    | μs   |

| WM control vo                          | oltage (COMP)                                |                                                                         |       |       |       |      |

| V <sub>COMPhi</sub>                    | Upper<br>saturation<br>voltage               | I <sub>COMP</sub> = 0                                                   | 2.98  |       |       | V    |

| V <sub>COMPlo</sub>                    | Lower clamp<br>level                         | I <sub>COMP</sub> ≤-1 mA <sup>(2)</sup>                                 |       | 0.95  | 1     | V    |

| I <sub>COMPmax</sub>                   | Maximum source current                       | V <sub>COMP</sub> =<br>V <sub>COMPlo</sub>                              |       | 300   | 370   | μΑ   |

| R <sub>COMP</sub>                      | Dynamic<br>resistance                        | V <sub>COMPlo</sub> <<br>V <sub>COMP</sub> <<br>V <sub>COMPsat_hi</sub> | 11    | 14    | 17    | kΩ   |

|                                        | Gain (ΔVcs/                                  | Sampled<br>V(ZCD) ≥<br>V <sub>ZCD_HGs</sub>                             | 0.377 | 0.386 | 0.4   | V/V  |

| Gs                                     | ΔV <sub>COMP</sub> )                         | Sampled<br>V(ZCD) ≤<br>V <sub>ZCD_LGs</sub>                             | 0.314 | 0.321 | 0.328 | V/V  |

| V <sub>COMP_OFF</sub>                  | Control voltage offset                       | (2)                                                                     | 0.18  | 0.2   | 0.225 | V    |

| ero current de                         | etector (ZCD)                                |                                                                         |       |       |       |      |

| V <sub>ZCDA</sub>                      | ZCD arming voltage                           | Voltage rising <sup>(2)</sup>                                           |       | 75    |       | mV   |

| V <sub>ZCDT</sub>                      | ZCD triggering voltage                       | Voltage falling <sup>(2)</sup>                                          |       | 50    |       | mV   |

| (dV <sub>ZCD</sub> /dt) <sub>min</sub> | Min. detectable slope                        | Voltage falling                                                         | 0.055 | 0.1   | 0.165 | V/µs |

| V <sub>ZCDLC</sub>                     | Lower clamp voltage                          | I <sub>ZCD</sub> = -100 μA<br>to -2.5 mA                                | -0.4  | -0.2  | 0     | V    |

| V <sub>ZCDUC</sub>                     | Upper clamp<br>voltage                       | I <sub>ZCD</sub> = 10 μA to<br>2.5 mA                                   | 4.6   |       |       | V    |

| $V_{ZCD_HGs}$                          | High Gs setting threshold                    | Voltage rising <sup>(2)</sup>                                           | 1.64  | 1.7   | 1.76  | V    |

| V <sub>ZCD_LGs</sub>                   | Low Gs setting threshold                     | Voltage falling <sup>(2)</sup>                                          | 1.59  | 1.65  | 1.71  | V    |

| I <sub>ZCDb</sub>                      | Static input bias current                    | V <sub>ZCD</sub> = 2.5 V                                                |       |       | 1.5   | μA   |

| Symbol                  | Parameter                                              | Test condition                               | Min.                                     | Тур.                 | Max.  | Unit  |  |

|-------------------------|--------------------------------------------------------|----------------------------------------------|------------------------------------------|----------------------|-------|-------|--|

| Tere                    | Forced restart                                         | After soft-start end <sup>(3)</sup>          | 2                                        | 2.2                  | 2.4   |       |  |

| T <sub>FRT</sub>        | timeout                                                | During soft-<br>start <sup>(3)</sup>         | 18                                       |                      | 24    | μA    |  |

| everse currer           | nt self-adjustment                                     | (CS)                                         |                                          |                      |       |       |  |

|                         | Adjustment current, active                             | V <sub>HVSpk</sub> = 120 V                   | 25                                       | 30                   | 40    |       |  |

| Ics <sub>ZVS</sub>      | from HS ↓ to LS                                        | V <sub>HVSpk</sub> = 360 V                   | 75                                       | 90                   | 115   | μA    |  |

| everse currer           | nt sensing (RCS)                                       | II                                           |                                          |                      |       |       |  |

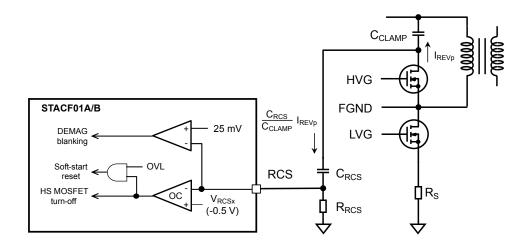

| V <sub>RCSx</sub>       | Overcurrent threshold                                  | (2)                                          | -0.5                                     | -0.46                | -0.44 | V     |  |

| T <sub>RCS</sub>        | Propagation delay                                      | From V <sub>RCSx</sub><br>hitting to HS ↓    |                                          | 90                   | 120   | ns    |  |

| ine feedforwa           | rd function (ZCD)                                      |                                              |                                          |                      |       |       |  |

| R <sub>FFe</sub>        | Feedforwardgai<br>nDV <sub>CSx</sub> /I <sub>ZCD</sub> | I <sub>ZCD</sub> = -100 μA<br>to -2.5 mA     |                                          | 240                  |       | mV/mA |  |

| Soft-start funct        | tion                                                   |                                              |                                          |                      |       |       |  |

| T <sub>SS</sub>         | Soft-start time                                        | (3)                                          | 5.5                                      | 8                    | 11    | ms    |  |

|                         |                                                        | dback function (TBL                          |                                          |                      |       |       |  |

| T <sub>BASE_r</sub>     | Programmable range                                     | Typical value                                | 0.8                                      |                      | 2.2   | μs    |  |

|                         |                                                        | $R_{\text{TBLANK}}$ = 150 kΩ <sup>(3)</sup>  | 0.72                                     | 0.8                  | 0.92  |       |  |

| T <sub>BASE</sub>       | Time base                                              | $R_{\text{TBLANK}} = 71.5$ $k\Omega^{(3)}$   | 1.44                                     | 1.6                  | 1.76  | μs    |  |

|                         |                                                        | $R_{\text{TBLANK}} = 9.1$<br>$k\Omega^{(3)}$ | 1.94                                     | 2.2                  | 2.46  | -     |  |

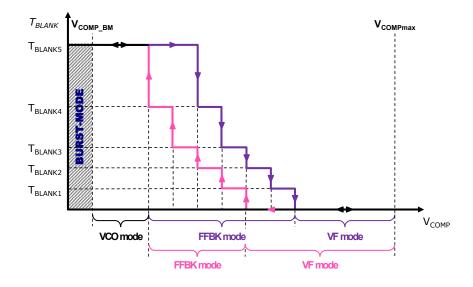

| T <sub>BLANK1</sub>     | 1 <sup>st</sup> blanking<br>time                       |                                              | T <sub>BASE</sub><br>2 T <sub>BASE</sub> |                      |       | μs    |  |

| T <sub>BLANK2</sub>     | 2 <sup>nd</sup> blanking<br>time                       |                                              |                                          |                      |       |       |  |

| T <sub>BLANK3</sub>     | 3 <sup>rd</sup> blanking<br>time                       | From instant of zero current detection       | 4 T <sub>BASE</sub>                      |                      |       |       |  |

| T <sub>BLANK4</sub>     | 4 <sup>th</sup> blanking<br>time                       |                                              | 6 T <sub>BASE</sub>                      |                      |       |       |  |

| T <sub>BLANK5</sub>     | 5 <sup>th</sup> blanking<br>time                       |                                              |                                          | 10 T <sub>BASE</sub> |       | _     |  |

| V <sub>COMP_TB0-1</sub> | No blanking $\rightarrow$<br>T <sub>BLANK1</sub>       | Voltage falling <sup>(2)</sup>               |                                          | 1.4                  |       |       |  |

| V <sub>COMP_TB1-2</sub> | T <sub>BLANK1</sub> →<br>T <sub>BLANK2</sub>           | Voltage falling <sup>(2)</sup>               |                                          | 1.35                 |       |       |  |

| V <sub>COMP_TB2-3</sub> | T <sub>BLANK2</sub> →<br>T <sub>BLANK3</sub>           | Voltage falling <sup>(2)</sup>               |                                          | 1.3                  |       | V     |  |

| V <sub>COMP_TB3-4</sub> | T <sub>BLANK3</sub> →<br>T <sub>BLANK4</sub>           | Voltage falling <sup>(2)</sup>               |                                          | 1.25                 |       | _     |  |

| V <sub>COMP_TB4-5</sub> | T <sub>BLANK4</sub> →<br>T <sub>BLANK5</sub>           | Voltage falling <sup>(2)</sup>               |                                          | 1.2                  |       |       |  |

| Symbol                  | Parameter                                                                   | Test condition                                                                            | Min. | Тур.                        | Max. | Unit |

|-------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----------------------------|------|------|

| V <sub>COMP_TB5-4</sub> | T <sub>BLANK5</sub> →<br>T <sub>BLANK4</sub>                                | Voltage rising <sup>(2)</sup>                                                             |      | 1.7                         |      |      |

| V <sub>COMP_TB4-3</sub> | T <sub>BLANK4</sub> →<br>T <sub>BLANK3</sub>                                | Voltage rising <sup>(2)</sup>                                                             |      | 1.75                        |      |      |

| V <sub>COMP_TB3-2</sub> | T <sub>BLANK3</sub> →<br>T <sub>BLANK2</sub>                                | Voltage rising <sup>(2)</sup>                                                             |      | 1.8                         |      | V    |

| V <sub>COMP_TB2-1</sub> | T <sub>BLANK2</sub> →<br>T <sub>BLANK1</sub>                                | Voltage rising <sup>(2)</sup>                                                             |      | 1.85                        |      |      |

| V <sub>COMP_TB1-0</sub> | $\begin{array}{l} T_{BLANK1} \rightarrow No \\ \text{blanking} \end{array}$ | Voltage rising <sup>(2)</sup>                                                             |      | 2.1                         |      |      |

| /oltage-control         | led oscillator                                                              |                                                                                           |      |                             |      |      |

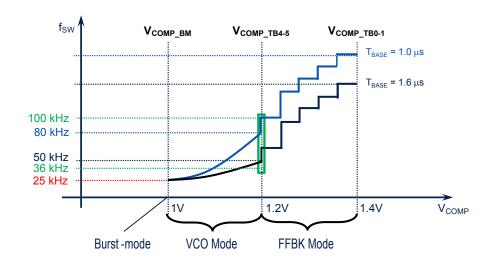

| F <sub>osc1</sub>       | Oscillation<br>frequency                                                    | V <sub>COMP</sub> =<br>V <sub>COMP_TB4-5</sub> <sup>(3)</sup>                             |      | 80 / T <sub>BASE</sub> [us] |      | kHz  |

| F <sub>osc2</sub>       | Oscillation<br>frequency                                                    | V <sub>COMP</sub> =<br>V <sub>COMP_BM</sub> <sup>(3)</sup>                                | 22.5 | 25                          | 27.5 | kHz  |

| Burst mode fun          | ction (COMP)                                                                | I I                                                                                       |      |                             |      |      |

| V <sub>COMP_BM</sub>    | Onset threshold                                                             | Voltage falling <sup>(2)</sup>                                                            | 0.95 | 1                           | 1.05 | V    |

| V <sub>BM_Hys</sub>     | Hysteresis                                                                  | Voltage rising                                                                            |      | 50                          |      | mV   |

| V <sub>COMP_EBM</sub>   | Exit threshold                                                              | Voltage rising <sup>(2)</sup>                                                             | 1.1  | 1.15                        | 1.2  | V    |

| N <sub>CYmin</sub>      | Min. # cycles<br>per burst                                                  |                                                                                           |      | 3                           |      |      |

| N <sub>CYmax</sub>      | Max. # cycles<br>per burst                                                  |                                                                                           |      | 32                          |      |      |

| F <sub>sw_BM</sub>      | Switching frequency                                                         | Within a burst <sup>(3)</sup>                                                             |      | 50                          |      | kHz  |

|                         | Current sense                                                               | Sampled<br>V(ZCD) ≥<br>V <sub>ZCD_HGs</sub> V <sub>COM</sub><br>P < V <sub>COMP_EBM</sub> | 200  | 220                         | 255  |      |

| VCSref_BM               | reference during<br>burst mode                                              | Sampled<br>V(ZCD) ≤<br>V <sub>ZCD_LGs</sub> V <sub>COMP</sub><br>< V <sub>COMP_EBM</sub>  | 130  | 150                         | 180  | – mV |

| Overload/overc          | urrent protection                                                           | timers                                                                                    |      |                             |      |      |

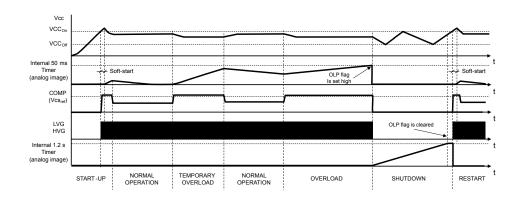

| T <sub>OVL</sub>        | Overload<br>timeout                                                         | V <sub>CSref</sub> ≥<br>V <sub>CSref_OVL</sub> <sup>(3)</sup>                             | 33   | 50                          | 67   | ms   |

| T <sub>RESTART</sub>    | Restart delay after fault                                                   | (3)                                                                                       | 0.8  | 1.2                         | 1.6  | S    |

| OVP function (Z         | CD)                                                                         |                                                                                           |      |                             |      |      |

| V <sub>ZCD_OVP</sub>    | Voltage<br>Reference for<br>sampled V <sub>ZCD</sub>                        | (2)                                                                                       | 2.9  | 3                           | 3.2  | V    |

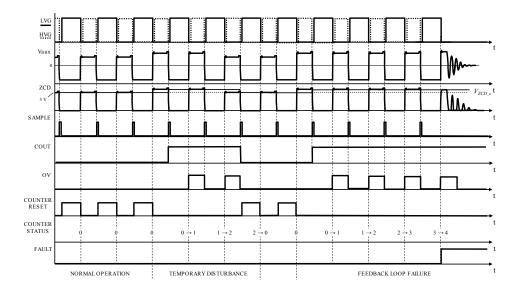

| N <sub>OVP</sub>        | Consecutive<br>cycles for OVP<br>tripping                                   |                                                                                           |      | 4                           |      |      |

| inear regulato          | r output (LDO5V)                                                            |                                                                                           |      |                             |      |      |

| V <sub>LDO5V</sub>      | Regulator setpoint                                                          | I <sub>LDO5V</sub> = 1 mA                                                                 | 4.8  | 5                           | 5.2  | V    |

| Symbol                  | Parameter                      | Test condition                            | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------------------|-------------------------------------------|------|------|------|------|

| I <sub>LDO5V</sub>      | Max source current             | Externally available                      | 1    |      |      | mA   |

| C <sub>LDO5V</sub>      | Allowable cap range            |                                           | 10   |      | 100  | nF   |

| UVLO <sub>LDO5V</sub>   | Undervoltage threshold         |                                           |      | 3.75 |      | V    |

| PFC CONTROL             | FUNCTION (PFC                  | RUN)                                      |      |      |      |      |

| IPFCRUN_high            | High level leakage current     | V <sub>PFCRUN</sub> =<br>V <sub>VCC</sub> |      |      | 1    | μA   |

| VPFCRUN_low             | Low saturation level           | I <sub>PFCRUN</sub> = 1 mA                |      |      | 0.2  | V    |

| ENABLE/DISAE            | BLE output (MGEN               | 1)                                        |      |      |      |      |

| $V_{MGEN\_high}$        | Output high voltage            | I <sub>MGEN</sub> = -6 mA                 | 4.5  | 4.9  |      | V    |

| V <sub>MGEN_low</sub>   | Output low voltage             | I <sub>MGEN</sub> = 6 mA                  |      |      | 0.4  | V    |

| General purpos          | se disable input (P            | ROT)                                      |      |      |      |      |

| V <sub>PROT_TH_L</sub>  | Latch-off<br>threshold         | Voltage falling <sup>(2)</sup>            | 0.94 | 1    | 1.04 | V    |

| V <sub>PROT_Hys-I</sub> | Hysteresis                     | Voltage rising                            |      | 100  |      | mV   |

| V <sub>PROT_</sub> USV  | Upper<br>saturation<br>voltage | Pin open                                  | 3.8  |      |      | V    |

| I <sub>PROT</sub>       | Pull-up current                | V <sub>PROT</sub> = 1.1 V                 | -60  | -50  | -40  | μA   |

| V <sub>PROT_TH_H</sub>  | Autorestart halt threshold     | Voltage rising <sup>(2)</sup>             | 2.88 | 3    | 3.3  | V    |

| V <sub>PROT_Hys-h</sub> | Hysteresis                     | Voltage falling                           |      | 100  |      | mV   |

| PWM outputs (           | LS & HS)                       |                                           |      |      |      |      |

| V <sub>PWMH</sub>       | Output high voltage            | I <sub>source</sub> = -6 mA               | 4.5  | 4.9  |      | V    |

| V <sub>PWML</sub>       | Output low voltage             | I <sub>sink</sub> = 6 mA                  |      |      | 0.4  | V    |

|                         |                                |                                           |      | 1    |      |      |

1. Parameters tracking each other.

2. Parameters tracking each other.

3. Parameters tracking each other.

# 6 Application information

The STACF01A/B ICs are intended to drive and control active clamp flyback (ACF) converters with the noncomplementary approach in high performance AC-DC adapters aimed at high efficiency and high power density.

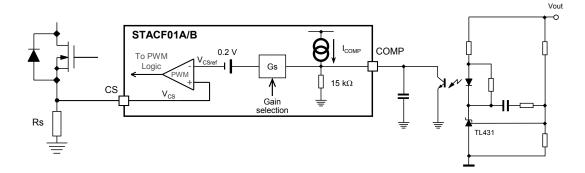

The ICs achieve output voltage regulation using a control signal coming from the secondary side by means of an input pin intended to be driven by an optocoupler.

The device can work in different modes, depending on the converter's load conditions:

- 1. Variable frequency mode (VF mode) at heavy load

- 2. Frequency foldback mode (FFBK mode) at intermediate load

- 3. Voltage-controlled frequency mode (VCO mode) at light load

- 4. Burst mode (BM) at very light or no load.

Seamlessly changing from one mode to another as load conditions dynamically vary over time.

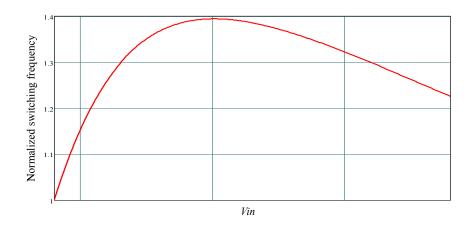

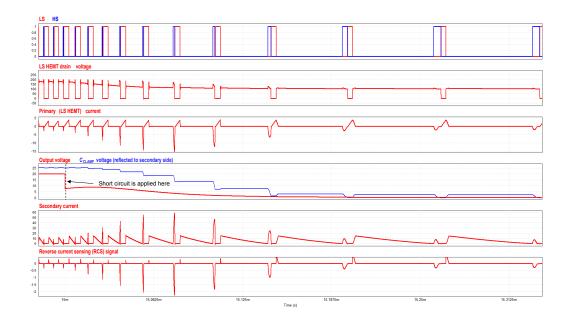

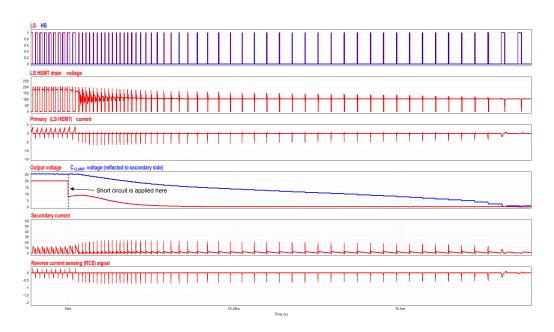

The objective of these multiple operating modes is to optimize converter efficiency over the widest load range. In an ACF converter this task is more challenging than in a conventional flyback converter. In fact, the energy necessary to achieve ZVS for the LS switch and controlled by the reverse current build-up process is essentially constant with the load. Then, although it involves a small portion of the processed power at nominal load, it may become a significant portion of it at light load, thus becoming a major source of the converters' efficiency drop.

Due to the nature of VF mode operation, when the converter is lightly loaded this effect is exacerbated by the switching frequency rising significantly. In addition, with a higher switching frequency switching losses increase correspondingly, and efficiency drops even more.

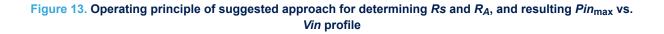

# 6.1 Theory of VF mode operation

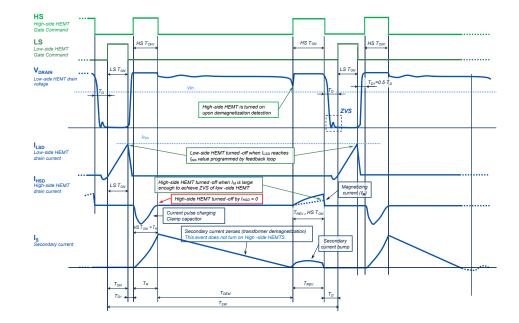

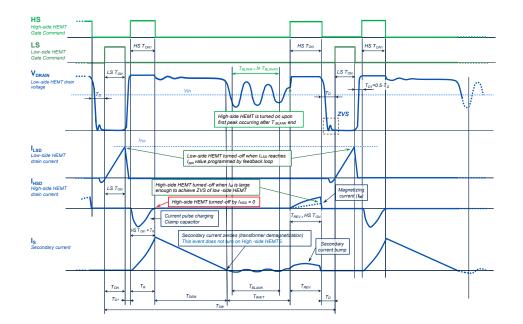

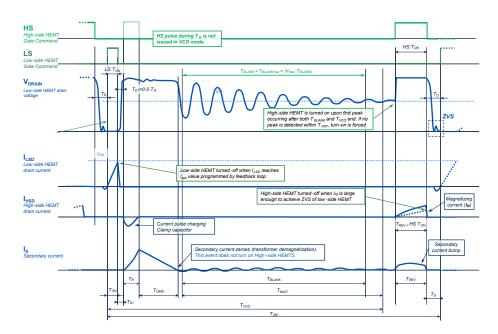

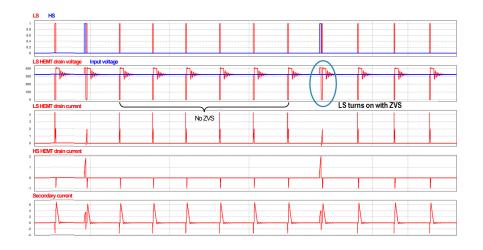

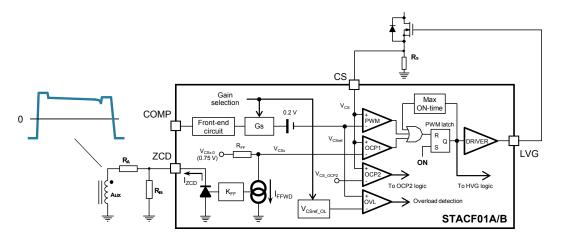

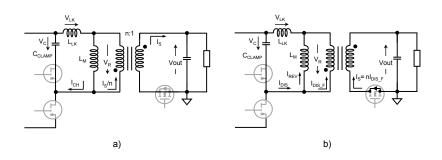

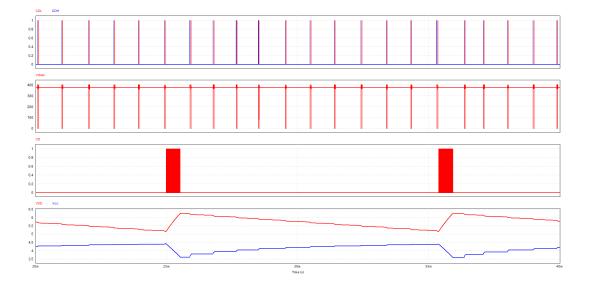

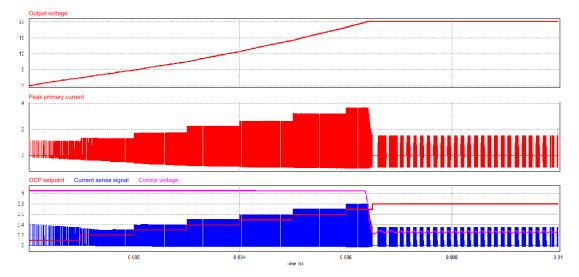

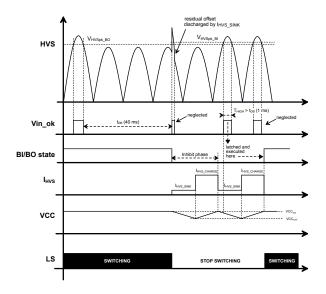

As shown in the timing diagram of Figure 4, when the STACF01A/B ICs (and the ACF converter, consequently) works in this mode, each switching cycle includes three main distinct time intervals:

<u>Transformer magnetization</u>. This time interval starts as the low-side (LS) switch is turned on and ends when the current in the transformer's primary winding reaches the level programmed by the control loop that regulates the output voltage. The LS switch is then turned off and its drain voltage goes up.

If the initial negative current (necessary condition to achieve zero-voltage switching, ZVS) is much smaller than the final peak current  $lp_{pk}$ , the duration of this time interval can be expressed as:

$$\Gamma_{ON} \approx \frac{Lp}{Vin} I p_{pk} \tag{1}$$

where *Lp* is the inductance of the primary winding and *Vin* the DC input voltage.

• <u>Transformer demagnetization</u>. After the LS switch turns off, in a first sub-interval the energy stored in the transformer's leakage inductance is transferred to the clamp capacitors in a resonant fashion. During this first sub-interval, whose duration is denoted with  $T_R$ , current starts to build up also on the secondary side and reaches a peak value as the primary current touches zero. During this time sub-interval, the high-side switch (HS) is turned on to let this current flow with a minimum source-drain voltage drop (when operated in the third quadrant, HEMT switches have a source-drain voltage drop of 3-4 V if the gate is not driven high).

Then, a second subsequent sub-interval starts where both primary switches are off and the secondary current linearly decays to zero while the energy stored in the clamp capacitor is retained. This time interval ends as the secondary current drops to zero, an event captured by the demagnetization detection circuit (ZCD).

Denoting with  $V_R$  the voltage reflected across the primary winding during this time interval, which equals the output voltage  $V_{out}$  times the primary-to-secondary turns ratio *n*, its overall duration is approximately:

$$\Gamma_{DEM} \approx \frac{Lp}{V_R} I p_{pk} \tag{2}$$

Figure 4. ACF converter key waveforms (VF mode operation, steady-state full load conditions)