#### Dual eFuse for 5 V and 12 V rails

DFN10 (2 x 3 mm)

#### **Maturity status link**

STEF512SRDB

#### **Features**

- 5 V and 12 V channels into one chip

- 25 V absolute maximum input voltage

- Precise output overvoltage clamp

- Fixed overcurrent protection trip points

- Fast reverse current protection on 5 V channel

- Thermal protection

- Latch-off thermal protection

- Input undervoltage lockout

- Adjustable output voltage slew rate for each channel by external capacitors

- Integrated 40 mΩ power MOSFETs

- 100 ms safety start-up delay

- SAS disable and enable pins

- 5 V embedded LDO

- 3 V transient protection

- DFN10 (2 x 3 mm) package

#### **Applications**

- HDD and SSD

- · Hard disk array and NAS

- Hot-swap, hot-plug protection

### **Description**

The STEF512SRDB is an integrated dual electronic fuse, designed to protect circuitry on the output from overcurrent and overvoltage events, in those applications requiring hot-swap operation and in-rush current control.

The device embeds two electronic fuses, one for the 5 V rail and one for the 12 V rail. Thanks to the very low ON-resistance of the integrated power MOSFETs, the voltage drop from the main supply to the load is very low during normal operation. The 5 V channel provides a reverse blocking feature, preventing current flow to the input in case of brownout or shutdown.

The start-up time of each eFuse can be adjusted by the user, via two small soft-start capacitors, connected to the relevant pins. In this way the in-rush current at startup can be kept under control. The maximum load current is precisely limited, by utilizing a sense FET topology, to factory-defined values.

The device also provides precise overvoltage clamp for each channel, preventing the load being damaged from power supply failures, and undervoltage lockout (UVLO), assuring that the input voltage is above the minimum operating threshold, before the power device is turned on.

When an overload condition occurs, the STEF512SRDB limits the output current to the predefined safe value. If the anomalous overload condition persists, the device goes into thermal shutdown, the internal switch is open and the load is disconnected from the power supply. 5 V fixed LDO is available to supply external load up to 10 mA.

# 1 Diagram

$V_{\rm IN\_12}$ U<sub>OUT\_12</sub>  $V_{\underline{IN}\underline{\phantom{1}}12}$ Thermal CHARGE 12 V CURRENT

VLDO 5 V LDO LIMIT PUMP Protection Driver  $V_{\underline{IN}_{5}} V_{\underline{IN}_{12}}$ ss₅ 🖒 UVLO

□ EN1 dV/dt CONTROL LOGIC **ENABLE** control SS<sub>12</sub> 🖰 Logic CURRENT LIMIT CHARGE 5 V PLP Thermal Protection PUMP Driver DRIVER  $- \downarrow V_{OUT_5}$

$V_{IN\_5}$

GND

Figure 1. Block diagram

DS13270 - Rev 2 page 2/32

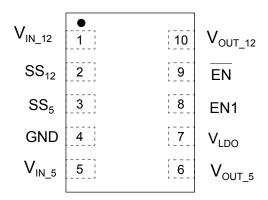

# Pin configuration

Figure 2. Pin connection (top view)

**Table 1. Pin description**

| Pin n° | Symbol              | Function                                                                                                                                                                  |

|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | V <sub>IN_12</sub>  | 12 V rail supply voltage                                                                                                                                                  |

| 2      | SS <sub>12</sub>    | Soft-start adjustment pin for the 12 V rail. A capacitor must be connected between this pin and GND to program the output voltage slew rate. Do not leave floating        |

| 3      | SS <sub>5</sub>     | Soft-start adjustment pin for the 5 V rail. A capacitor must be connected between this pin and GND to program the output voltage slew rate. Do not leave floating         |

| 4      | GND                 | Ground                                                                                                                                                                    |

| 5      | V <sub>IN_5</sub>   | 5 V rail supply voltage                                                                                                                                                   |

| 6      | V <sub>OUT_5</sub>  | 5 V rail output voltage                                                                                                                                                   |

| 7      | V <sub>LDO</sub>    | 5 V embedded LDO, bypass to GND with a 1 μF ceramic                                                                                                                       |

| 8      | EN1                 | Auxiliary enable pin, see Section 6.3. This pin is internally pulled up to 3.3 V via 3.3 $$ M $\Omega$ resistor after both input voltages exceed the UVLO threshold       |

| 9      | EN                  | SAS disable input: set this pin logic-low to turn on the device, high to turn off the device. This pin is internally pulled down to GND via 3.3 $\mbox{M}\Omega$ resistor |

| 10     | V <sub>OUT_12</sub> | 12 V rail output voltage                                                                                                                                                  |

DS13270 - Rev 2 page 3/32

# 3 Typical application

Figure 3. Typical application circuit

Table 2. Recommended application components

| Symbol              | Description                    | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------|------|------|------|------|

| C <sub>IN_12</sub>  | Input capacitor 12 V rail (1)  | 0    | 1    |      | μF   |

| C <sub>IN_5</sub>   | Input capacitor 5 V rail (1)   | 0    | 1    |      | μF   |

| C <sub>OUT_12</sub> | Output capacitor 12 V rail     | 10   | 47   |      | μF   |

| C <sub>OUT_5</sub>  | Output capacitor 5 V rail      | 10   | 47   |      | μF   |

| C <sub>SS_5</sub>   | Soft start capacitor 5 V rail  | 10   | 100  | 1000 | nF   |

| C <sub>SS_12</sub>  | Soft start capacitor 12 V rail | 10   | 100  | 1000 | nF   |

| C <sub>LDO</sub>    | LDO bypass capacitor           | 0.47 | 1    | 10   | μF   |

<sup>1.</sup> This value must be considered with DC-bias derating characteristics of capacitance used. In case of long wires cable application see Section 6.7.

DS13270 - Rev 2 page 4/32

## 4 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol                             | Parameter                                       | Value                         | Unit |

|------------------------------------|-------------------------------------------------|-------------------------------|------|

| V                                  | 5 V supply voltage                              | -0.3 to 25                    | V    |

| V <sub>IN_5</sub>                  | Negative transient tolerance (< 1 ms)           | -3                            | V    |

| V                                  | 12 V supply voltage                             | -0.3 to 25                    | V    |

| V <sub>IN_12</sub>                 | Negative transient tolerance (< 1 ms)           | -3                            | V    |

| V <sub>OUT_5</sub>                 | 5 V output voltage                              | -0.3 to 7                     | V    |

| V <sub>OUT_12</sub>                | 12 V output voltage                             | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| $V_{LDO}$                          | LDO output voltage                              | -0.3 to 7                     | V    |

| I <sub>LDO</sub>                   | LDO output current                              | 50                            | mA   |

| I <sub>OUT_5</sub>                 | Continuous output current (1) 5 V channel       | 3                             | А    |

| I <sub>OUT_12</sub>                | Continuous output current (1) 12 V channel      | 3.6                           | А    |

| V <sub>EN</sub> , V <sub>EN1</sub> | Enable pins                                     | -0.3 to 7                     | V    |

| SS <sub>x</sub>                    | Soft-start pin voltage                          | -0.3 to 7                     | V    |

| P <sub>D</sub>                     | Continuous power dissipation                    | Internal limited              |      |

| T <sub>J-OP</sub>                  | Operating junction temperature range            | -40 to 125                    | °C   |

| T <sub>J-MAX</sub>                 | Maximum junction temperature (internal limited) | 150                           | °C   |

| T <sub>STG</sub>                   | Storage temperature range                       | -55 to 150                    | °C   |

<sup>1.</sup> This value can be applied for guaranteed lifetime. Higher value can be applied for a time lower than 200 ms. The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{J-MAX}$ , the junction-to-ambient thermal resistance  $R_{thJA}$ , and the ambient temperature  $T_A$ . It can be estimated by:  $P_{D(MAX)} = (T_{J(MAX)} - T_A) / R_{thJA}$ . Exceeding the maximum allowable power dissipation produces overheating that may cause thermal shutdown.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All values are referred to GND.

Table 4. Thermal data

| Symbol            | Parameter                               | Value | Unit |

|-------------------|-----------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient (1) | 82    | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case        | 12    | °C/W |

<sup>1.</sup> Based on JESD51-7, 4-layer PCB.

Table 5. ESD performance

| Symbol | Parameter              | Test conditions | Value | Unit |

|--------|------------------------|-----------------|-------|------|

| ESD    | ESD protection voltage | НВМ             | 2     | kV   |

| LSD    | ESD protection voltage | CDM             | 500   | V    |

DS13270 - Rev 2 page 5/32

## 5 Electrical characteristics

$T_J$  = 25°C,  $V_{IN\_5}$  = 5 V,  $V_{IN\_12}$  = 12 V,  $V_{EN}$  = 0 V,  $V_{EN1}$  = 1.8 V,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 10  $\mu$ F,  $C_{LDO}$  = 1  $\mu$ F,  $C_{SS5}$  =  $C_{SS12}$  = 100 nF; unless otherwise specified.

**Table 6. Electrical characteristics**

| Symbol                | Parameter                               | Test conditions                                                                       | Min.     | Тур. | Max. | Unit |  |

|-----------------------|-----------------------------------------|---------------------------------------------------------------------------------------|----------|------|------|------|--|

| 5 V rail              |                                         |                                                                                       |          |      |      |      |  |

| V <sub>IN_5</sub>     | Operating input voltage                 |                                                                                       | 4.5      |      | 18   | V    |  |

| V <sub>Clamp_5</sub>  | Average output clamping voltage         | V <sub>IN_5</sub> = 18 V                                                              | 5.5      | 5.7  | 5.8  | V    |  |

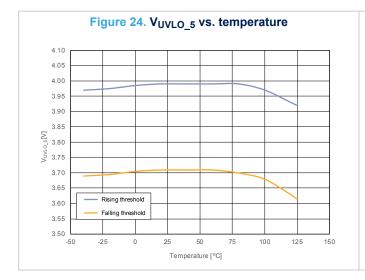

| V                     | Lindaryoltaga laakaut                   | Turn-on, V <sub>IN_5</sub> rising                                                     | 3.9      | 4    | 4.1  | V    |  |

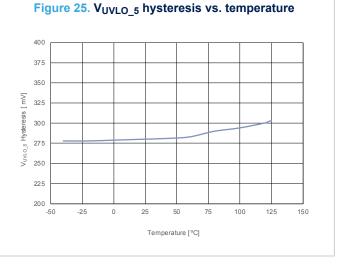

| V <sub>UVLO_5</sub>   | Undervoltage lockout                    | Hysteresis                                                                            |          | 300  |      | mV   |  |

| D <sub>-</sub> -      | On registance                           | $T_J = 25$ °C, $I_{OUT\_5} = 500$ mA                                                  |          | 45   |      | mΩ   |  |

| R <sub>DSon_5</sub>   | On-resistance                           | T <sub>J</sub> = 125°C <sup>(1)</sup>                                                 |          |      | 70   | mΩ   |  |

| I <sub>L_5</sub>      | Off-state leakage current               | $V_{EN} = 5 \text{ V}, V_{OUT\_5} = GND$                                              |          |      | 1    | μΑ   |  |

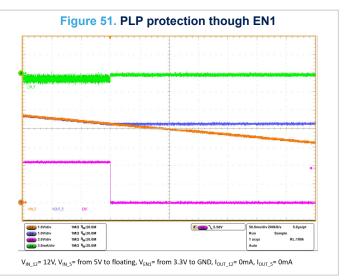

|                       | Power loss protection reverse           | $V_{EN} = 0 \text{ V}, V_{OUT\_5} = 5 \text{ V},$                                     |          |      | 4    |      |  |

| I <sub>PLP_5</sub>    | leakage current                         | $V_{IN_5} < V_{UVLO_5}$ or EN1 = GND                                                  |          |      | 1    | μA   |  |

|                       |                                         | $V_{EN} = 0 \text{ V}, V_{OUT\_5} = 5 \text{ V},$                                     |          |      |      |      |  |

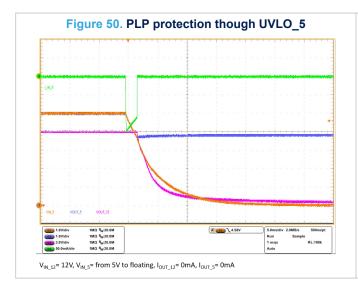

| $T_PLP$               | Power loss protection intervention time | $V_{IN_{-}5} < V_{UVLO_{-}5}$ or EN1 = GND (falling edge), $I_{PLP_{-}5} < 1 \mu A$ , |          | 300  |      | ns   |  |

|                       |                                         | (see Section 6.7)                                                                     |          |      |      |      |  |

| I <sub>TRIP_5</sub>   | Overcurrent trip point (2)              |                                                                                       |          | 3    |      | Α    |  |

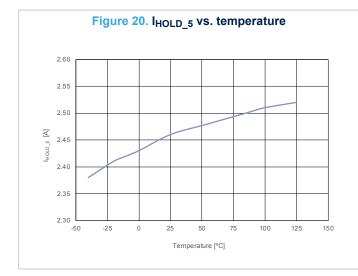

| I <sub>HOLD_5</sub>   | Overload current limit                  | V <sub>OUT_5</sub> > 2.5 V                                                            | 2.35     | 2.5  | 2.85 | Α    |  |

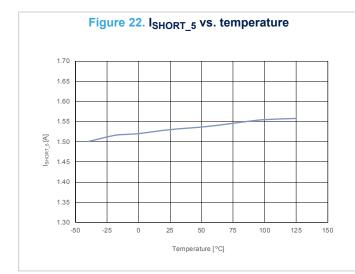

| I <sub>SHORT_5</sub>  | Short-circuit current                   | V <sub>OUT_5</sub> < 2.5 V                                                            |          | 1.55 |      | Α    |  |

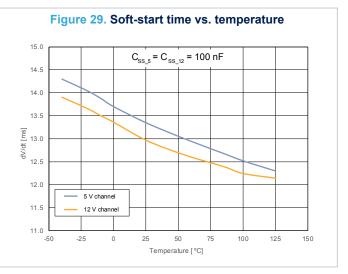

| dV/dt_5               | Output voltage ramp time                | From 10% to 90% of V <sub>OUT_5</sub>                                                 | 11       | 13   | 16   | ms   |  |

| 12 V rail             |                                         |                                                                                       |          |      |      |      |  |

| V <sub>IN_12</sub>    | Operating input voltage                 |                                                                                       | 10.5     |      | 18   | V    |  |

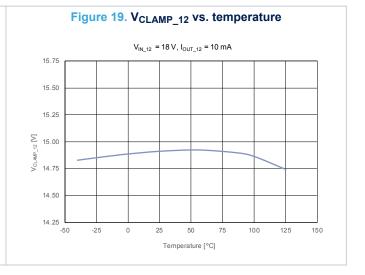

| V <sub>Clamp_12</sub> | Average output clamping voltage         | V <sub>IN_12</sub> = 18 V                                                             | 14.5     | 15   | 15.5 | V    |  |

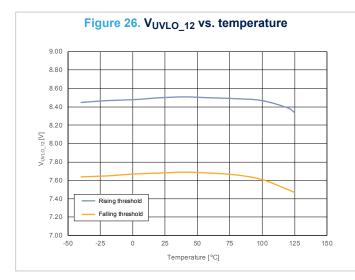

| V                     | Lindow (alternational)                  | Turn-on, V <sub>IN_12</sub> rising                                                    | 7.7      | 8.5  | 9.3  | V    |  |

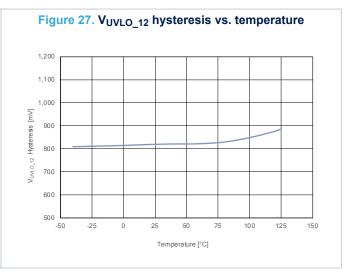

| V <sub>UVLO_12</sub>  | Undervoltage lockout                    | Hysteresis                                                                            |          | 800  |      | mV   |  |

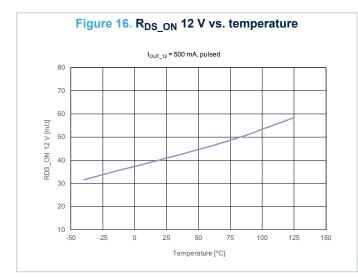

| D                     | On maintain                             | T <sub>J</sub> = 25°C, I <sub>OUT_12</sub> = 500 mA                                   |          | 40   |      | mΩ   |  |

| R <sub>DSon_12</sub>  | On-resistance                           | $T_{J} = 125^{\circ}C^{(1)}$                                                          |          |      | 65   | mΩ   |  |

| I <sub>L_12</sub>     | Off-state leakage current               | V <sub>EN</sub> = 5 V, V <sub>OUT_12</sub> = GND                                      |          |      | 3    | μΑ   |  |

| I <sub>TRIP_12</sub>  | Overcurrent trip point (2)              |                                                                                       |          | 4.5  |      | Α    |  |

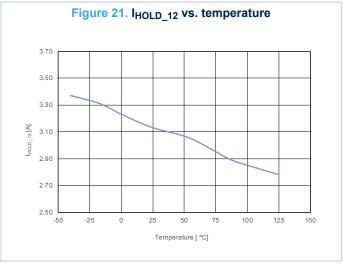

| I <sub>HOLD_12</sub>  | Overload current limit                  | V <sub>OUT_12</sub> > 7.5 V                                                           | 2.95     | 3.1  | 3.25 | Α    |  |

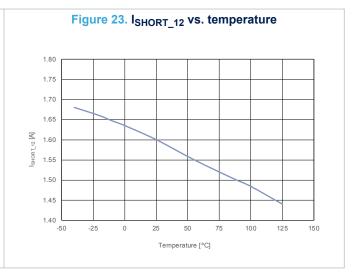

| I <sub>SHORT_12</sub> | Short-circuit current                   | V <sub>OUT_12</sub> < 7.5 V                                                           |          | 1.6  |      | Α    |  |

| dV/dt_ <sub>12</sub>  | Output voltage ramp time                | From 10% to 90% of V <sub>OUT_12</sub>                                                | 11       | 13   | 16   | ms   |  |

| 5 V LDO               | 1                                       |                                                                                       | <u> </u> | 1    | 1    |      |  |

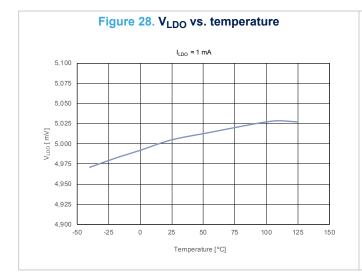

| V <sub>LDO</sub>      | V <sub>OUT</sub> accuracy               | I <sub>LDO</sub> = 1 mA                                                               | - 3      |      | 3    | %    |  |

| I <sub>OUT</sub>      | Output current capability               | Any ENx condition, V <sub>IN_5</sub> and V <sub>IN_12</sub> > V <sub>UVLO_X</sub>     | 10       |      |      | mA   |  |

|                       |                                         | - 114_0 11N_12 + UVLU_X                                                               |          |      |      |      |  |

DS13270 - Rev 2 page 6/32

| Symbol                 | Parameter                          | Test conditions                                                    | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------|--------------------------------------------------------------------|------|------|------|------|

| Line                   | Line regulation                    | V <sub>IN_12</sub> from 10 to 15 V                                 |      | 10   |      | mV   |

| Load                   | Load regulation                    | I <sub>LDO</sub> = 1 mA                                            |      | 25   |      | mV   |

| I <sub>SC</sub>        | Short-circuit protection           |                                                                    | 50   |      |      | mA   |

| T <sub>ON</sub>        | Ctart up time                      | V <sub>LDO</sub> from 10% to 90%                                   |      | 4    |      | ma   |

| ION                    | Start-up time                      | $V_{IN_{5}}$ and $V_{IN_{12}} > V_{UVLO_{X}}$                      |      | 1    |      | ms   |

| Common f               | eatures                            |                                                                    |      |      |      |      |

| V <sub>IL</sub>        | Low level input voltage (EN, EN1)  |                                                                    |      |      | 0.5  | V    |

| V <sub>IH</sub>        | High level input voltage (EN, EN1) |                                                                    | 1.4  |      |      | V    |

| V <sub>pull1</sub>     | EN1 pull-up voltage                | EN1 floating                                                       |      | 3.3  |      | V    |

| R <sub>Pull-up</sub>   | Pull-up resistor on EN1            |                                                                    |      | 3.3  |      | МΩ   |

| R <sub>Pull-down</sub> | Pull-down resistor on EN           | EN = floating                                                      |      | 3.3  |      | ΜΩ   |

| T <sub>DELAY</sub>     | Start-up output delay time         | V <sub>IN_12</sub> and V <sub>IN_5</sub> > V <sub>UVLO_X</sub>     | 80   | 100  | 120  | ms   |

| IEN                    | EN leakage                         | V <sub>EN</sub> = 5 V                                              |      | 1.5  |      | μA   |

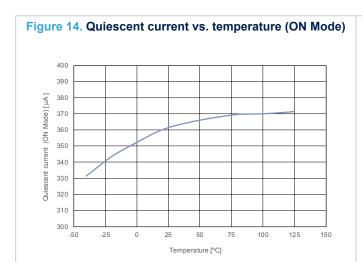

|                        |                                    | Device operating, no Load                                          |      | 350  | 600  | μA   |

| IQ                     | Quiescent current (GND)            | Off-state, $V_{EN} = 5 \text{ V}$ , including LDO and ENx currents |      | 150  |      | μA   |

| Thermal pi             | rotection                          |                                                                    |      |      |      |      |

| T <sub>SD</sub>        | Shutdown temperature (3)           |                                                                    |      | 165  |      | °C   |

| 'SD                    | Hysteresis                         |                                                                    |      | 20   |      | °C   |

Values across temperature range are guaranteed by design/correlation and tested in production only at ambient temperature.

DS13270 - Rev 2 page 7/32

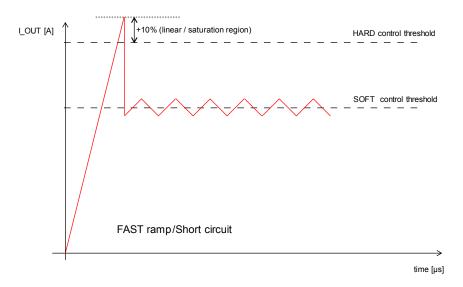

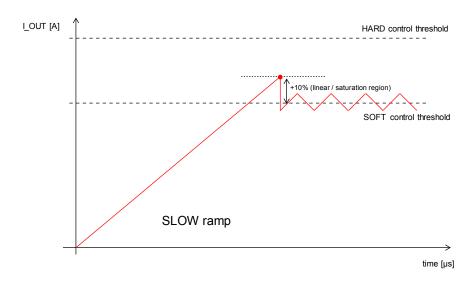

<sup>2.</sup> Guaranteed by design, but not tested in production. Ramp-up time from 0 A to  $I_{TRIP}$  point 1 ms @ 5 V, 100  $\mu$ s @ 12 V. Minimum  $I_{TRIP}$  point is always higher than  $I_{HOLD\_min}$  +10%.

<sup>3.</sup> Guaranteed by design, but not tested in production.

### 6 Functional description

The STEF512SRDB embeds a 5 V and a 12 V electronic fuse (eFuse). Each eFuse is an intelligent load switch, able to limit the voltage or the current during fault events, such as input overvoltage or output overload respectively.

For this purpose, it contains 2 digital control loops, one limiting the output voltage and one limiting the input current.

During normal operation the eFuse behaves as a low-resistance Power FET, therefore the output voltage follows the input one. In case of overvoltage or overcurrent event, the eFuse limits the  $V_{GS}$  of the internal FET, in order to clamp the output voltage or current respectively. During such events the die temperature increases due to the power dissipation and so, if the fault persists and the overtemperature threshold is overcome, the device goes into thermal shutdown, the internal FET is turned off and the load disconnected from the power supply.

Each eFuse provides factory-trimmed undervoltage lockout feature and user-adjustable output voltage linear rise time  $\Delta t$  [ms] (from 10% to 90% of  $V_{OUT}$ ) to limit the in-rush current into the output capacitor during the start-up phase.

Given the desired time interval  $\Delta t$ , the capacitance to be added on the  $C_{ss\_x}$  pin with nominal input voltage  $V_{IN~12}$  = 12 V,  $V_{IN~5}$  = 5 V can be calculated using the following theoretical formula.

$$\Delta t[ms] = C_{SS\_X}[nF] \times 0.13 \tag{1}$$

#### 6.1 Undervoltage lockout

Undervoltage lockout circuit prevents each eFuse from turning on if the supply voltage is below the UVLO rising threshold. During operation, if the input voltage of one channel falls below  $(V_{UVLO_x} - V_{Hyst_x})$ , the outputs of both channels are turned off simultaneously and LDO output shuts down at the same time.

#### 6.2 Start-up sequence and voltage clamp

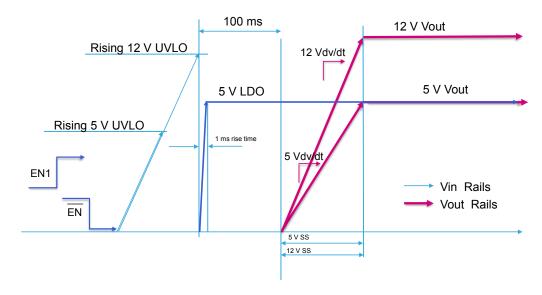

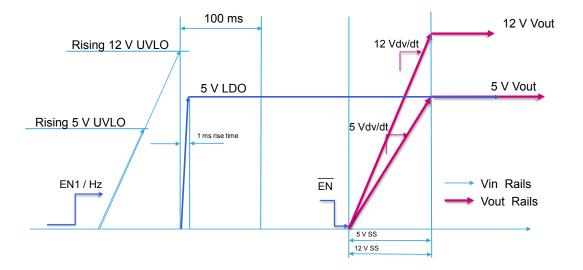

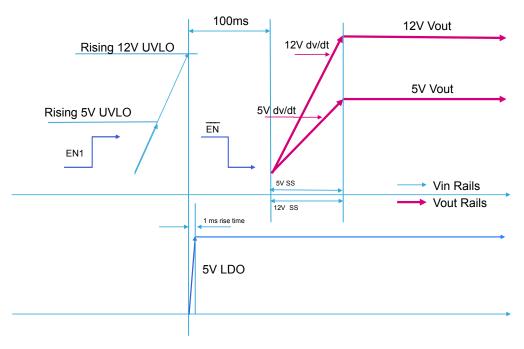

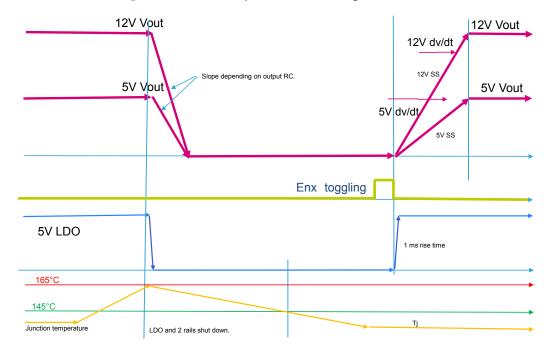

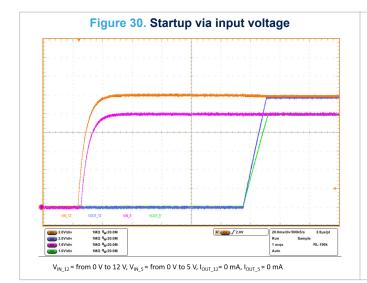

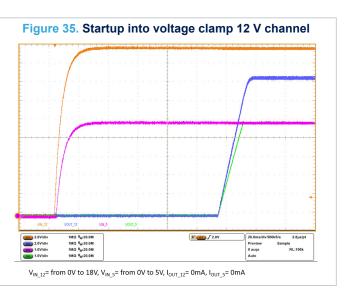

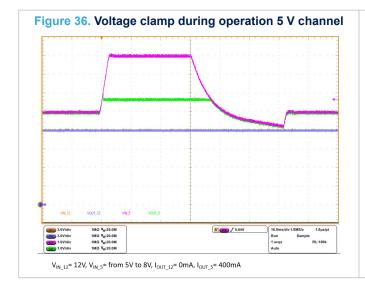

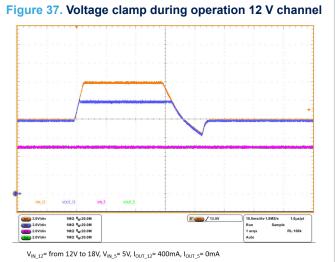

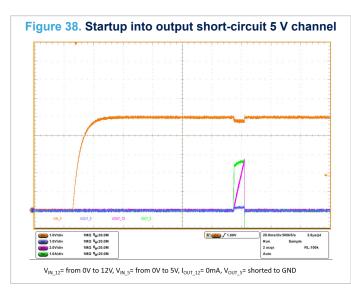

The typical start-up sequence of the eFuse is described below and shown in Figure 4, Figure 5 and Figure 6:

- The power supply is connected to the V<sub>IN x</sub> pins and higher than the undervoltage lockout threshold

- The disable pin EN and the auxiliary EN1 pin are asserted according to Table 7. Enable pins truth table by the user to enable the device

- After a delay of 100 ms the eFuse starts ramping up the output voltage

- Each channel ramps up with a rate set by the relevant C<sub>SSx</sub>

- If the input voltage continues rising, above the overvoltage threshold (V<sub>Clamp\_x</sub>), as a consequence of a failure in the power supply, the eFuse limits the output voltage to V<sub>Clamp\_x</sub>. The eFuse keeps operating in this state until it hits its overtemperature threshold and shuts down. Whenever the eFuse is in thermal shutdown, it does not restart automatically, see Section 6.2. The eFuse can be restarted manually by toggling the EN pin or EN1, or performing a power-up cycle, (this is effective as soon as the die temperature drops by at least the overtemperature hysteresis).

DS13270 - Rev 2 page 8/32

Figure 4. Typical start-up sequence with EN1 and EN in ON-state before input power supply connection

Figure 5. Typical start-up sequence with EN1 and/or EN in ON-state after time delay

DS13270 - Rev 2 page 9/32

Figure 6. Typical start-up sequence with EN1 or EN in ON-state during time delay

Figure 7. LDO and output channels during thermal event

### 6.3 Enable pins

The device provides an SAS-compliant chip disable pin  $\overline{\text{EN}}$  and an auxiliary enable pin EN1.

The auxiliary enable pin can be used to implement customized start-up/shutdown sequences, in conjunction with other system companion chips (such as power combos in the HDD) and it is pulled up to the internal preregulated voltage (typ. 3.3 V), through  $3.3 \text{ M}\Omega$  resistors, as soon as the input voltage of both channels surpasses the UVLO thresholds.

It is not recommended to use LDO output as external pull-up voltage of EN1 pin.

DS13270 - Rev 2 page 10/32

As a logic input it controls the eFuse ON/OFF status, together with the  $\overline{\text{EN}}$  pin. If this function is not needed in the application, it can be left floating. The device ON/OFF behavior depends on the enable pins as described in the following truth table:

EN

EN1

Device status

HZ/0

0

Off

HZ/0

HZ/1

On

1

0

Off

1

HZ/1

Off

Table 7. Enable pins truth table

According to the above table and the internal pull-up configuration, if both enable pins are left floating, the device is in the ON status.

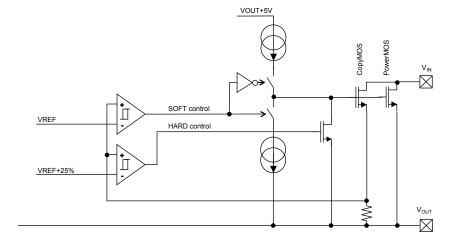

#### 6.4 Current limit function after startup

In case of overcurrent with moderate slew rate the soft control limits output current at the  $I_{HOLD}$  threshold and the gate of the power MOSFET is driven by constant current source/sink.

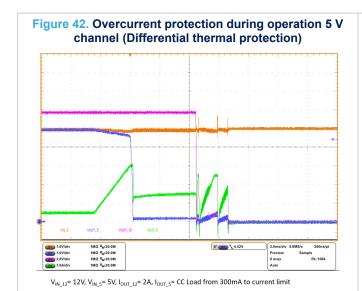

Instead, in case of fast overcurrent event or short-circuit event with output current reaching I<sub>TRIP</sub> threshold the hard control shorts immediately the gate to source by a strong pull-down. See Figure 8, Figure 9 and Figure 10.

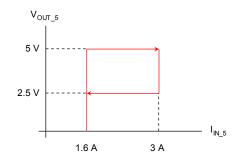

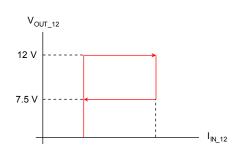

During current limitation phase the eFuse provides 2 levels of current limit protection according to output voltage level, see Figure 11 and Figure 12. If output voltage falls to 7.5 V for a 12 V channel (2.5 V for a 5 V channel) the current control loop changes the current limitation threshold from I<sub>HOLD</sub> to I<sub>SHORT</sub>.

Figure 8. Current control loop block diagram

DS13270 - Rev 2 page 11/32

Figure 10. Overcurrent protection in case of overload with slow slew rate

Figure 11. Current limit function graph (5 V channel)

DS13270 - Rev 2 page 12/32

4.5 A

Figure 12. Current limit function graph (12 V channel)

#### 6.5 Thermal shutdown

If the device temperature exceeds the thermal threshold, typically 165°C, the thermal shutdown circuitry turns the power MOSFET off, thus disconnecting the load. The device keeps the output channels and LDO output in OFF mode until the temperature goes below the hysteresis value and a toggling of the enable is performed or a power-on reset is applied.

1.6 A

The device is also equipped with a differential thermal protection that avoids damage in case of fast thermal gradients inside the chip. When the differential thermal protection is activated both the channel and the LDO are switched off. This protection works in auto-retry mode. The device restarts automatically when the thermal conditions go back into the normal operating region.

#### 6.6 Reverse current blocking feature on the 5 V channel

The 5 V eFuse contains a second power transistor (M2) that is able to prevent significant current flowing back from the 5 V output into the 5 V input, in case of input short to ground, brownout or deep input voltage glitch. The simplified structure is shown in Figure 13.

Reverse blocking MOSFET M2 is controlled by the UVLO circuit and EN1 signal.

It should be noted that when  $V_{IN\_5}$  undervoltage is detected, the M2 is turned off immediately (asynchronously), however the main MOSFET M1 is kept ON for the next 10  $\mu$ s due to the deglitch circuit.

If the input voltage recovers within the deglitch time, the eFuse is able to rapidly restore its normal operating state (warm restart). Otherwise, the eFuse shuts down completely.

As soon as the UVLO threshold has been reached again, the eFuse restarts with normal soft-start cycle.

V<sub>IN\_5</sub>

V<sub>OUT\_5</sub>

V<sub>OUT\_5</sub>

C<sub>OUT\_5</sub>

Overcurrent

Overcurrent

Overcurrent

Overcurrent

Figure 13. 5 V reverse current protection block diagram

DS13270 - Rev 2 page 13/32

#### 6.7 External capacitors and application tips

Input and output capacitors are mandatory to reduce the transient effects of stray inductances which may be present on the input and output power paths. In fact, when the STEF512SRDB interrupts the current flow, input inductance generates a positive voltage spike on the input, and output inductance generates a negative voltage spike on the output. To reduce the effects of such transients, a  $C_{IN}$  capacitor of at least 1  $\mu$ F (including derating effects) must be connected between the input pin and GND, and located as close as possible to the device.

For the same reason, a  $C_{\mbox{\scriptsize OUT}}$  capacitor of at least 10  $\mu\mbox{\scriptsize F}$  must be connected at the output port.

When the device is connected to the power supplies by means of long wires, whose inductance is higher than  $1 \mu H$ , the input capacitor should be increased.

It is suggested to provide for additional protections and methods for addressing these transients, such as:

- Minimizing inductance of the input and output tracks

- TVS diodes on the input to absorb inductive spikes placed as close as possible to input pins

- Schottky diode on the output to absorb negative spikes

- Combination of ceramic and electrolytic capacitors on the input and output.

DS13270 - Rev 2 page 14/32

## 7 Typical characteristics

The following plots refer to the typical application circuit with  $Vcc_12 = 12 \text{ V}$ ,  $Vcc_5 = 5 \text{ V}$ ,  $lout_12 = 0 \text{ A}$ ,  $lout_5 = 0 \text{ A}$ ,  $lout_LDO = 0 \text{ A}$ , ulless otherwise noted, at  $T_A = 25^{\circ}C$ .

EN1 connected to GND

EN1 connected to GND

To the second second

DS13270 - Rev 2 page 15/32

Figure 18. V<sub>CLAMP\_5</sub> vs. temperature

V<sub>IN\_5</sub>= 18 V, I<sub>OUT\_5</sub>= 10 mA

6.2

6.0

5.8

5.8

5.4

Temperature [°C]

DS13270 - Rev 2 page 16/32

DS13270 - Rev 2 page 17/32

DS13270 - Rev 2 page 18/32

DS13270 - Rev 2 page 19/32

DS13270 - Rev 2 page 20/32

DS13270 - Rev 2 page 21/32

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

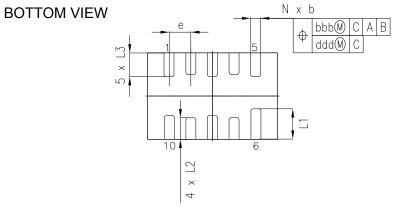

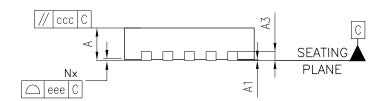

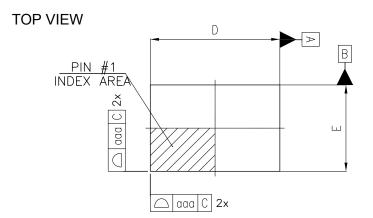

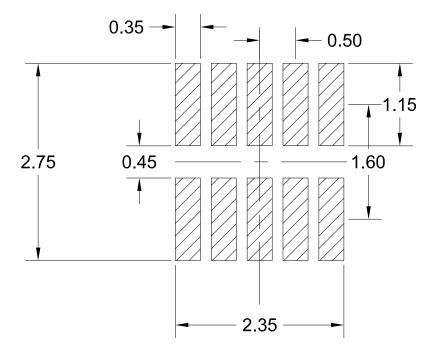

### 8.1 DFN10 (2 x 3 mm) package information

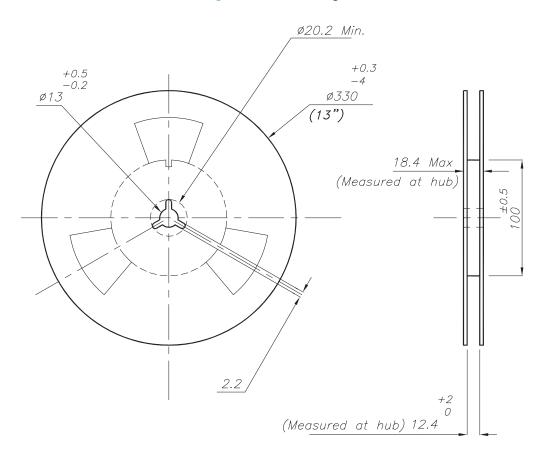

Figure 52. DFN10 (2 x 3 mm) package outline

SIDE VIEW

DS13270 - Rev 2 page 22/32

Table 8. DFN10 (2 x 3 mm) mechanical data

| Dim  |          | mm         |       |  |  |

|------|----------|------------|-------|--|--|

| Dim. | Min.     | Тур.       | Max.  |  |  |

| А    | 0.70     | 0.75       | 0.80  |  |  |

| A1   | 0.00     | 0.02       | 0.05  |  |  |

| A3   |          | 0.203 ref. |       |  |  |

| b    | 0.180    | 0.230      | 0.280 |  |  |

| D    |          | 3.00 BSC   |       |  |  |

| е    | 0.50 BSC |            |       |  |  |

| E    | 2.00 BCS |            |       |  |  |

| L1   | 0.60     | 0.70       | 0.80  |  |  |

| L2   | 0.40     | 0.50       | 0.60  |  |  |

| L3   | 0.45     | 0.55       | 0.65  |  |  |

| K    | 0.20     |            |       |  |  |

| N    | 10       |            |       |  |  |

| aaa  | 0.05     |            |       |  |  |

| bbb  | 0.10     |            |       |  |  |

| ccc  |          | 0.10       |       |  |  |

| ddd  |          | 0.05       |       |  |  |

| eee  |          | 0.08       |       |  |  |

Figure 53. DFN10 (2 x 3 mm) recommended footprint

DS13270 - Rev 2 page 23/32

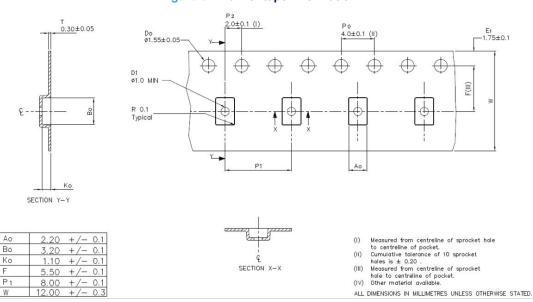

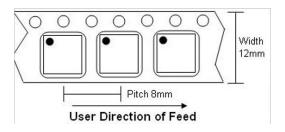

### 8.2 DFN10 (2 x 3) carrier tape information

Figure 54. Carrier tape information

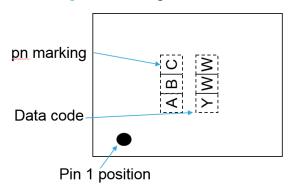

Figure 55. Marking information

DS13270 - Rev 2 page 24/32

Figure 56. Reel drawing

DS13270 - Rev 2 page 25/32

# 9 Ordering information

#### Table 9. Order codes

| Order code     | Package   | Marking | UVLO_5 [V] | UVLO_12 [V] | Trip point configuration  | Note          |

|----------------|-----------|---------|------------|-------------|---------------------------|---------------|

| STEF512SRDBPUR | DFN10 2x3 | EDB     | 4          | 8.5         | 3 A on 5 V, 4.5 A on 12 V | 5 V LDO + EN1 |

DS13270 - Rev 2 page 26/32

## **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                  |

|-------------|----------|--------------------------|

| 23-Apr-2021 | 1        | Initial release.         |

| 12-Apr-2023 | 2        | Updated Section Features |

DS13270 - Rev 2 page 27/32

## **Contents**

| 1  | Diag   | gram                                                | 2  |

|----|--------|-----------------------------------------------------|----|

| 2  |        | configuration                                       |    |

| 3  | Турі   | ical application                                    | 4  |

| 4  | Max    | imum ratings                                        | 5  |

| 5  |        | ctrical characteristics                             |    |

| 6  | Fun    | ctional description                                 | 8  |

|    | 6.1    | Undervoltage lockout                                | 8  |

|    | 6.2    | Start-up sequence and voltage clamp                 | 8  |

|    | 6.3    | Enable pins                                         | 10 |

|    | 6.4    | Current limit function after startup                | 11 |

|    | 6.5    | Thermal shutdown                                    | 13 |

|    | 6.6    | Reverse current blocking feature on the 5 V channel | 13 |

|    | 6.7    | External capacitors and application tips            |    |

| 7  | Typi   | ical characteristics                                | 15 |

| 8  | Pac    | kage information                                    | 22 |

|    | 8.1    | DFN10 (2 x 3 mm) package information                | 22 |

|    | 8.2    | DFN10 (2 x 3) carrier tape information              | 24 |

| 9  | Ord    | ering information                                   | 26 |

| Re | vision | history                                             | 27 |

## **List of tables**

| Table 1.  | Pin description                    |

|-----------|------------------------------------|

| Table 2.  | Recommended application components |

| Table 3.  | Absolute maximum ratings           |

|           | Thermal data                       |

| Table 5.  | ESD performance                    |

| Table 6.  | Electrical characteristics         |

| Table 7.  | Enable pins truth table            |

| Table 8.  | DFN10 (2 x 3 mm) mechanical data   |

| Table 9.  | Order codes                        |

| Table 10. | Document revision history          |

# **List of figures**

| Figure 1.  | Block diagram                                                                                                  |      |

|------------|----------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Pin connection (top view)                                                                                      | 3    |

| Figure 3.  | Typical application circuit                                                                                    |      |

| Figure 4.  | Typical start-up sequence with EN1 and $\overline{\text{EN}}$ in ON-state before input power supply connection | 9    |

| Figure 5.  | Typical start-up sequence with EN1 and/or EN in ON-state after time delay                                      |      |

| Figure 6.  | Typical start-up sequence with EN1 or $\overline{\text{EN}}$ in ON-state during time delay                     |      |

| Figure 7.  | LDO and output channels during thermal event                                                                   | . 10 |

| Figure 8.  | Current control loop block diagram                                                                             | . 11 |

| Figure 9.  | Overcurrent protection in case of short-circuit event                                                          | . 12 |

| Figure 10. | Overcurrent protection in case of overload with slow slew rate                                                 | . 12 |

| Figure 11. | Current limit function graph (5 V channel)                                                                     | . 12 |

| Figure 12. | Current limit function graph (12 V channel)                                                                    | . 13 |

| Figure 13. | 5 V reverse current protection block diagram                                                                   | . 13 |

| Figure 14. | Quiescent current vs. temperature (ON Mode)                                                                    | . 15 |

| Figure 15. | Quiescent current vs. temperature (OFF Mode)                                                                   | . 15 |

| Figure 16. | R <sub>DS ON</sub> 12 V vs. temperature                                                                        | . 15 |

| Figure 17. | R <sub>DS ON</sub> 5 V vs. temperature                                                                         | . 15 |

| Figure 18. | V <sub>CLAMP 5</sub> vs. temperature                                                                           |      |

| Figure 19. | V <sub>CLAMP 12</sub> vs. temperature                                                                          |      |

| Figure 20. | I <sub>HOLD 5</sub> vs. temperature                                                                            |      |

| _          | <del>-</del>                                                                                                   |      |

| Figure 21. | I <sub>HOLD_12</sub> vs. temperature                                                                           |      |

| Figure 22. | I <sub>SHORT_5</sub> vs. temperature                                                                           |      |

| Figure 23. | I <sub>SHORT_12</sub> vs. temperature                                                                          |      |

| Figure 24. | V <sub>UVLO_5</sub> vs. temperature                                                                            |      |

| Figure 25. | V <sub>UVLO_5</sub> hysteresis vs. temperature                                                                 | . 17 |

| Figure 26. | V <sub>UVLO 12</sub> vs. temperature                                                                           | . 17 |

| Figure 27. | V <sub>UVLO 12</sub> hysteresis vs. temperature                                                                |      |

| Figure 28. | V <sub>LDO</sub> vs. temperature                                                                               |      |

| Figure 29. | Soft-start time vs. temperature                                                                                |      |

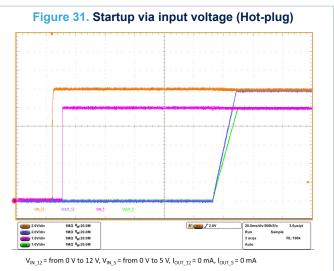

| Figure 30. | Startup via input voltage                                                                                      |      |

| Figure 31. | Startup via input voltage (Hot-plug)                                                                           |      |

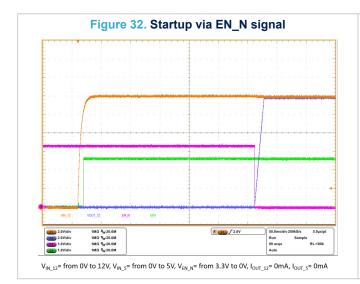

| Figure 32. | Startup via EN N signal                                                                                        |      |

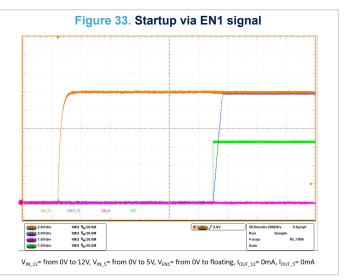

| Figure 33. | Startup via EN1 signal                                                                                         |      |

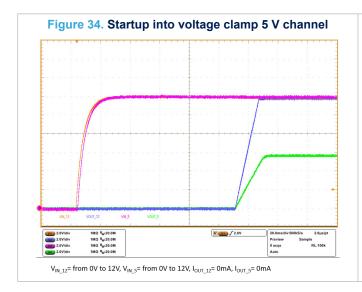

| Figure 34. | Startup into voltage clamp 5 V channel                                                                         |      |

| Figure 35. | Startup into voltage clamp 12 V channel                                                                        |      |

| Figure 36. | Voltage clamp during operation 5 V channel                                                                     |      |

| Figure 37. | Voltage clamp during operation 12 V channel                                                                    |      |

| Figure 38. | Startup into output short-circuit 5 V channel                                                                  |      |

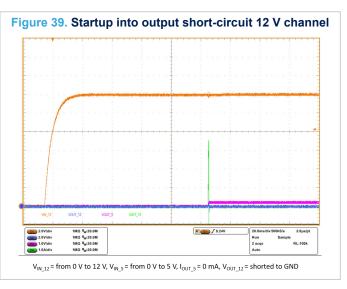

| Figure 39. | Startup into output short-circuit 12 V channel                                                                 |      |

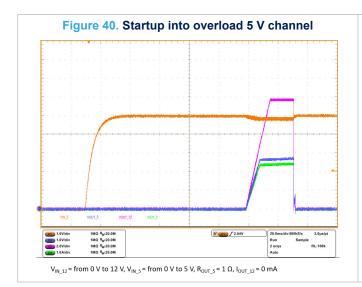

| Figure 40. | Startup into overload 5 V channel                                                                              |      |

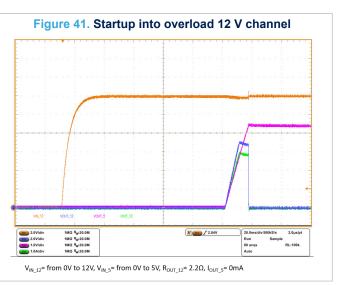

| Figure 41. | Startup into overload 12 V channel                                                                             |      |

| Figure 42. | Overcurrent protection during operation 5 V channel (Differential thermal protection)                          |      |

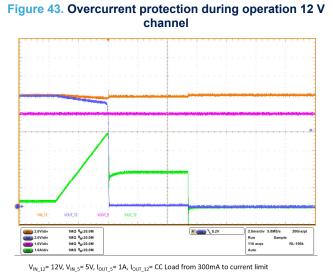

| Figure 43. | Overcurrent protection during operation 12 V channel                                                           |      |

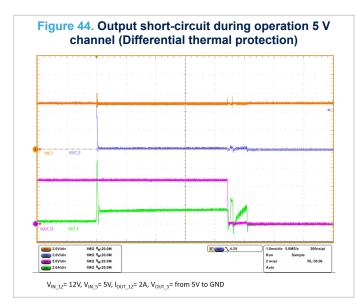

| Figure 44. | Output short-circuit during operation 5 V channel (Differential thermal protection)                            |      |

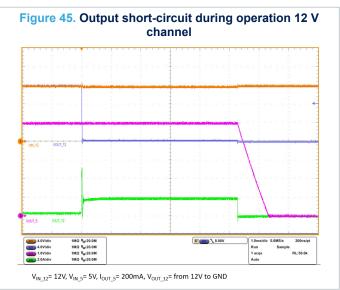

| Figure 45. | Output short-circuit during operation 12 V channel                                                             |      |

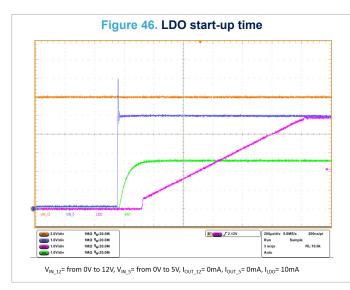

| Figure 46. | LDO start-up time                                                                                              |      |

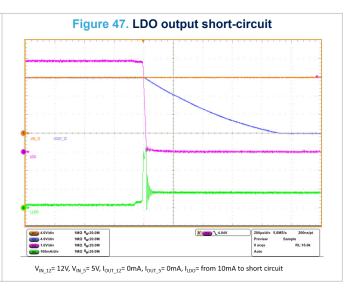

| Figure 47. | LDO output short-circuit.                                                                                      |      |

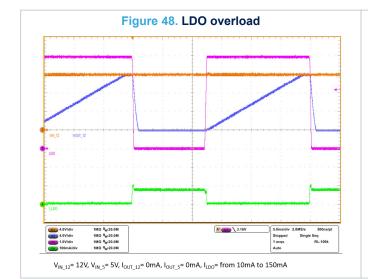

| Figure 48. | LDO overload.                                                                                                  |      |

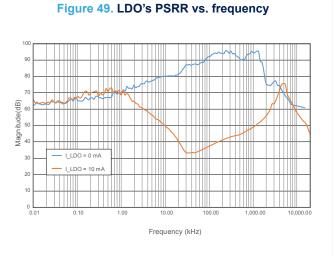

| Figure 49. | LDO's PSRR vs. frequency                                                                                       |      |

| Figure 50. | PLP protection though UVLO_5                                                                                   |      |

| Figure 51. | PLP protection though EN1                                                                                      |      |

| -          |                                                                                                                |      |

DS13270 - Rev 2 page 30/32

### STEF512SRDB

| Figure 52. | DFN10 (2 x 3 mm) package outline       | 22 |

|------------|----------------------------------------|----|

| Figure 53. | DFN10 (2 x 3 mm) recommended footprint | 23 |

| Figure 54. | Carrier tape information               | 24 |

| Figure 55. | Marking information                    | 24 |

| Figure 56. | Reel drawing                           | 25 |

DS13270 - Rev 2 page 31/32

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

DS13270 - Rev 2 page 32/32