### STM1068

### Smart voltage supervisor

Not recommended for new design

#### **Features**

- Operating voltage 2.7 V to 5.5 V

- Supply current of 1.5 µA (typ)

- Factory-trimmed voltage threshold from 3.2 V to 3.5 V in 50 mV increments

- 3% voltage threshold accuracy across temperature

- Enable and inhibit inputs (EN, INH)

- Power supply transient immunity

- Current limited output of 15 mA (max)

- Available in Flip Chip 8-bump package

- Operating temperature -30 °C to +85 °C

### **Applications**

- Portable devices

- Cell phones/smart phones

- PDA

- Palmtops

- Organizers

- Portable audio/video players

- Portable erminals

Contents STM1068

### **Contents**

| 1     | Description                         |

|-------|-------------------------------------|

| 2     | Operation                           |

|       | 2.1 Output, OUT                     |

|       | 2.2 Enable input, EN 8              |

|       | 2.3 Inhibit input, INH              |

|       | 2.4 Pass gate, PKX and POX          |

| 3     | Typical operating characteristics10 |

| 4     | Maximum ratings                     |

| 5     | DC and AC characteristics           |

| 6     | Package mechanical data             |

| 7     | Part numbering                      |

| 8     | Package marking information         |

| 9     | Revision history                    |

|       | lete 1                              |

| 01050 |                                     |

| OA    |                                     |

STM1068 List of tables

### List of tables

| Table 1.<br>Table 2.<br>Table 3.             | Pin descriptions                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.<br>Table 5.<br>Table 6.<br>Table 7. | Absolute maximum ratings                                                                                                                                                                                                                                                                                                                                           |

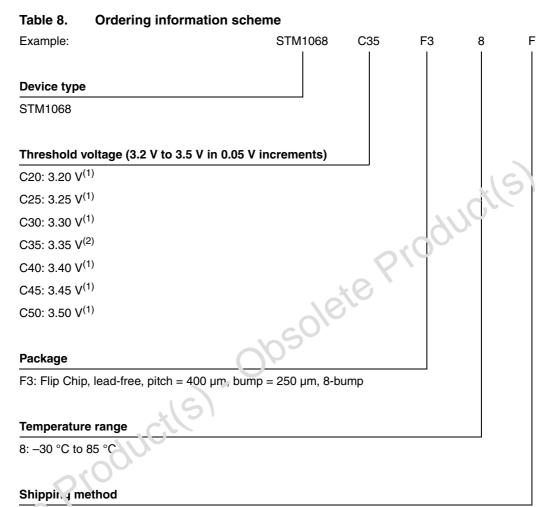

| Table 8.<br>Table 9.<br>Table 10.            | Ordering information scheme                                                                                                                                                                                                                                                                                                                                        |

|                                              | a coducil                                                                                                                                                                                                                                                                                                                                                          |

|                                              | leje Pro                                                                                                                                                                                                                                                                                                                                                           |

|                                              | Obsolu                                                                                                                                                                                                                                                                                                                                                             |

|                                              | ct(s)                                                                                                                                                                                                                                                                                                                                                              |

|                                              | Droginio                                                                                                                                                                                                                                                                                                                                                           |

| 005019                                       | Pin descriptions Truth table for output, OUT. Truth table for pass gate between PKX and POX Absolute maximum ratings Operating and AC measurement conditions. 11 Operating and AC characteristics Flip Chip 8-bump, package mechanical data 11 Ordering information scheme 13 Factory-trimmed thresholds with marking description. 22 Document revision history 23 |

| OF                                           |                                                                                                                                                                                                                                                                                                                                                                    |

|                                              |                                                                                                                                                                                                                                                                                                                                                                    |

List of figures STM1068

# **List of figures**

| Figure 1.<br>Figure 2. | Logic diagram 8-bump Flip Chip connections Block diagram  |

|------------------------|-----------------------------------------------------------|

| Figure 3.              | Block diagram                                             |

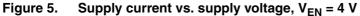

| Figure 4.<br>Figure 5. | Supply current vs. supply voltage. V <sub>ENI</sub> = 4 V |

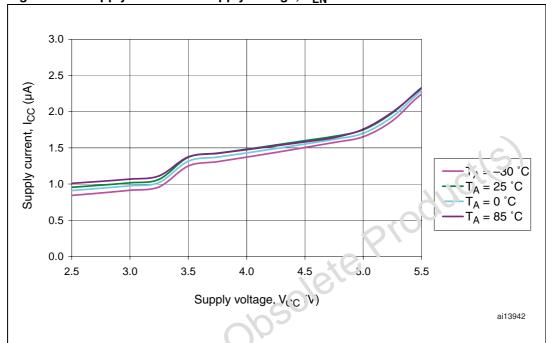

| Figure 6.              | Supply current vs. temperature, $V_{EN} = 4 V$            |

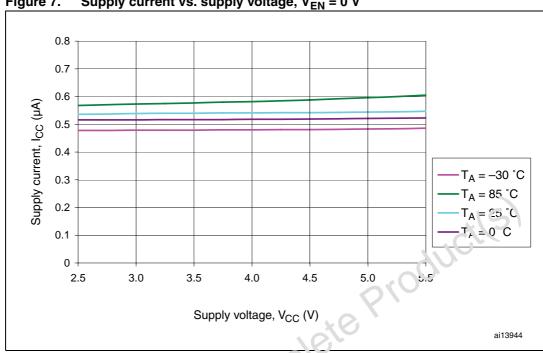

| Figure 7.              | Supply current vs. supply voltage, V <sub>EN</sub> = 0 V  |

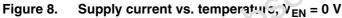

| Figure 8.              | Supply current vs. temperature, V <sub>EN</sub> = 0 V     |

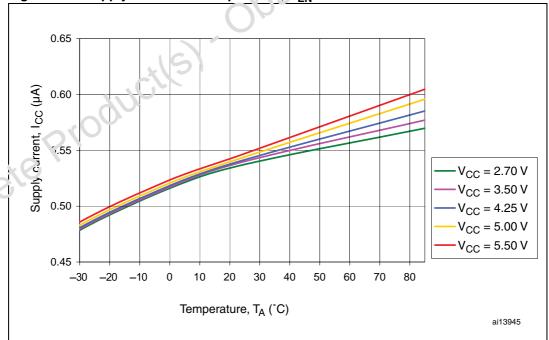

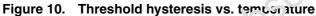

| Figure 9.              | Threshold hysteresis vs. temperature                      |

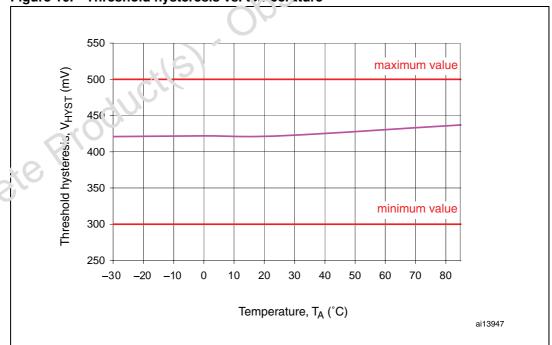

| Figure 11.             | Waveforms                                                 |

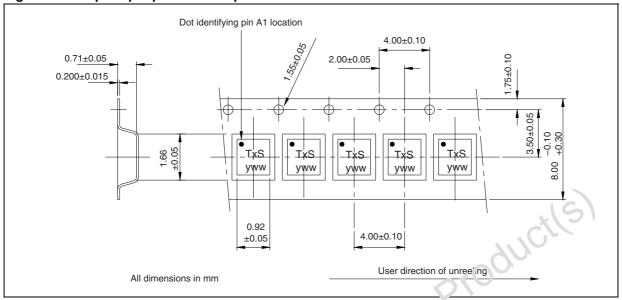

| Figure 12.             | Flip Chip 8-bump, package mechanical outline              |

| Figure 13.             | Flip Chip tape and reel specifications18                  |

|                        |                                                           |

|                        |                                                           |

|                        | × 0,                                                      |

|                        |                                                           |

|                        |                                                           |

|                        |                                                           |

|                        | Ob                                                        |

|                        |                                                           |

|                        | .15)                                                      |

|                        |                                                           |

|                        |                                                           |

|                        |                                                           |

|                        |                                                           |

|                        | 40.                                                       |

| \(()                   |                                                           |

| -0/                    |                                                           |

| 5                      |                                                           |

| )\                     |                                                           |

|                        |                                                           |

|                        |                                                           |

|                        |                                                           |

STM1068 Description

### 1 Description

STM1068 device monitors supply voltage  $V_{CC}$  and the state of EN and INH inputs. Depending on logical combination of these inputs, the output OUT is connected to  $V_{IN}$  or GND and the pass gate between PKX and POX is either enabled or disabled (see *Table 2* and *Table 3* for more details).

The device offers several voltage thresholds,  $V_{TH+}$  (see *Table 9*) and it is available in miniature Flip Chip 8-bump package.

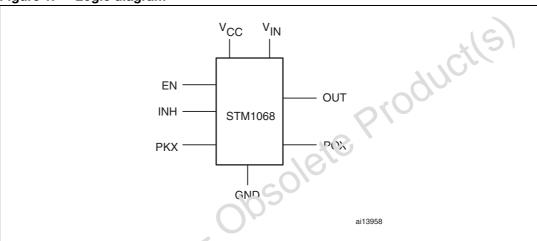

Figure 1. Logic diagram

Table 1. Pin descriptions

|      | Pin | Symbol          | Function                    |

|------|-----|-----------------|-----------------------------|

|      | 1A  | V <sub>IN</sub> | Supply for output pin (OUT) |

|      | 1,B | EN              | Enable from USB VBUS        |

|      | 1C  | GND             | Ground                      |

| 10   | 1D  | PKX             | Pass gate input             |

|      | 2A  | OUT             | Output                      |

| 0050 | 2B  | INH             | Inhibit input               |

| OF   | 2C  | V <sub>CC</sub> | Supply voltage              |

|      | 2D  | POX             | Pass gate output            |

Description STM1068

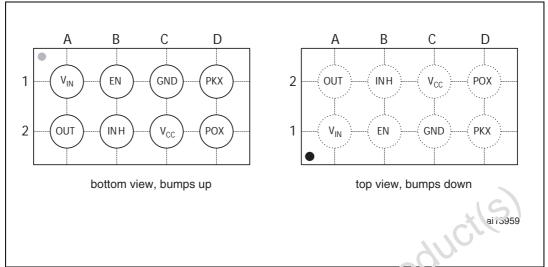

Figure 2. 8-bump Flip Chip connections

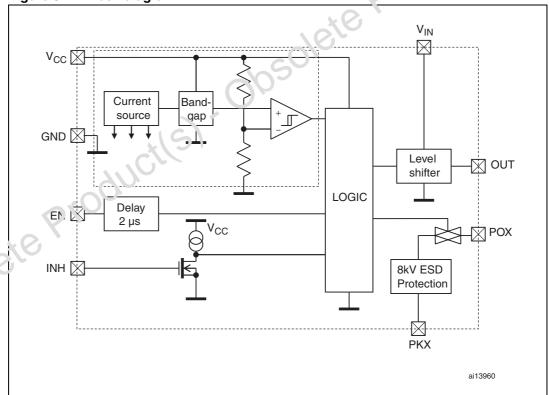

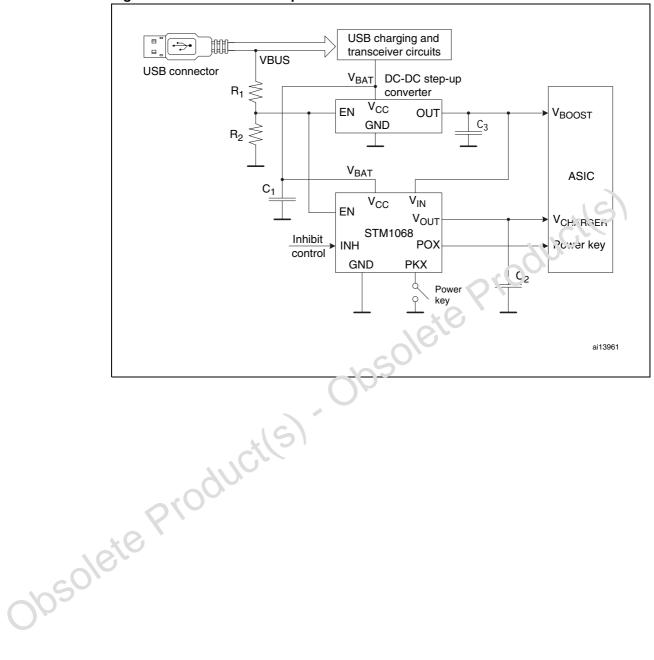

Figure 3. Block diagram

STM1068 Description

Figure 4. Hardware hookup

Operation STM1068

### 2 Operation

The STM1068 device monitors supply voltage  $V_{CC}$  and logic states of EN and INH inputs. According to detected states is the output OUT connected to  $V_{IN}$  or GND and the pass gate between PKX and POX is either enabled or disabled (see *Table 2*, *Table 3*, and *Figure 11* for more details).

#### 2.1 Output, OUT

If the enable input is in a logic high state and inhibit input is in a logic low state, the output will be connected to  $V_{IN}$  input as  $V_{CC}$  rises above the  $V_{TH+}$  voltage threshold. Otherwise, the output is connected to ground GND. The output is current limited (see *Table 6*).

#### 2.2 Enable input, EN

A logic low on the enable input disconnects the output, OUT, from  $V_{IN}$ , the POX will follow the PKX and the device enters a standby mode with very low current consumption (see *Table 6*).

#### 2.3 Inhibit input, INH

A logic high on the inhibit input discorner is the output, OUT, from  $V_{\text{IN}}$  and the POX will follow the PKX.

### 2.4 Pass gate, PKX and POX

Pass gate between PKX and POX is disabled only if enable input is in logic high, inhibit input is in logic low and the supply voltage is below the voltage threshold.

| Ta'16 2. | Trut | h table i | for out | put, OUT |

|----------|------|-----------|---------|----------|

| 1 (4)    |      |           |         |          |

| EN <sup>(1)</sup> | INH | v <sub>cc</sub>                                                        | ОИТ                          |

|-------------------|-----|------------------------------------------------------------------------|------------------------------|

| L                 | x   | X                                                                      | connected to GND             |

| х                 | Н   | X                                                                      | connected to GND             |

| х                 | х   | <v<sub>TH+ (rising edge)<br/><v<sub>TH- (falling edge)</v<sub></v<sub> | connected to GND             |

| Н                 | L   | >V <sub>TH+</sub> (rising edge)<br>>V <sub>TH-</sub> (falling edge)    | connected to V <sub>IN</sub> |

<sup>1.</sup> Once the device is disabled by EN input, the  $V_{CC}$  must be above  $V_{TH+}$  to reconnect output to  $V_{IN}$ .

STM1068 Operation

Table 3. Truth table for pass gate between PKX and POX

|       | EN                                  | INH     | V <sub>CC</sub>                                                        | POX         |

|-------|-------------------------------------|---------|------------------------------------------------------------------------|-------------|

|       | L                                   | х       | х                                                                      | follows PKX |

|       | Х                                   | Н       | х                                                                      | follows PKX |

|       | Х                                   | х       | >V <sub>TH+</sub> (rising edge)<br>>V <sub>TH-</sub> (falling edge)    | follows PKX |

|       | Н                                   | L       | <v<sub>TH+ (rising edge)<br/><v<sub>TH- (falling edge)</v<sub></v<sub> | open        |

| Note: | Table valid for V <sub>CC</sub> > 2 | 2.7 V.  | PKC                                                                    | ducile      |

|       |                                     |         | dete,                                                                  |             |

|       |                                     | 0       | 050                                                                    |             |

|       | *e Produ                            | cils) O | <v<sub>TH (falling edge)</v<sub>                                       |             |

## 3 Typical operating characteristics

Figure 6. Supply current vs. temperature,  $V_{EN} = 4 \text{ V}$

10/22 Doc ID 13864 Rev 8

Supply current vs. supply voltage,  $V_{EN} = 0 V$ Figure 7.

Figure 9. Rising voltage detector threshold vs. temperature

12/22 Doc ID 13864 Rev 8

STM1068 Maximum ratings

### 4 Maximum ratings

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 4. Absolute maximum ratings

| VIN         Outp           VEN         VBU           VOUT         Outp | pply voltage put source voltage  JS input put pin bit pin | -0.2<br>-0.2<br>-0.2<br>-0.3 |    | +7.0<br>+7.0<br>V <sub>CC</sub> + 0.3 | V<br>V | Independer to V <sub>CC</sub>  |

|------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------|----|---------------------------------------|--------|--------------------------------|

| V <sub>EN</sub> VBU                                                    | JS input<br>put pin                                       | -0.2<br>-0.3                 |    | _                                     |        |                                |

| Outr                                                                   | put pin                                                   | -0.3                         |    | V <sub>CC</sub> + 0.3                 | ٧      | Series VI external resistor    |

|                                                                        |                                                           |                              |    |                                       |        | for protection                 |

| V <sub>INH</sub> Inhib                                                 | bit pin                                                   |                              |    | V <sub>IN</sub> + 0.3                 |        | *                              |

|                                                                        |                                                           | -0.3                         |    | V <sub>CC</sub> + 03                  | V      |                                |

| /                                                                      | <b>5</b> 1                                                |                              |    | +2                                    | kV     | Human body model (all pins)    |

| / <sub>ESD</sub> Elec                                                  | Electrostatic protection                                  | -8                           | 26 | +8                                    | kV     | Human body model<br>(PKX only) |

| esD Elec                                                               | ctrostatic protection                                     | -500                         |    | +500                                  | V      | Charged device model           |

| esD Elec                                                               | ctrostatic protection                                     | -100                         |    | +100                                  | V      | Machine model                  |

| esD Poin                                                               | nt discharge on P₁♡ k∈y                                   | -8                           |    | +8                                    | kV     | IEC61000-4-2                   |

| / <sub>ESD</sub> Air d                                                 | discharge on Pr´k'key                                     | -15                          |    | +15                                   | kV     | IEC61000-4-2                   |

| T <sub>A</sub> Ope                                                     | erating sinblent temperature                              | -30                          |    | +85                                   | °C     |                                |

| Stor                                                                   | ra ça temperature                                         | -45                          |    | +150                                  | °C     |                                |

#### 5 DC and AC characteristics

This section summarizes the operating measurement conditions and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics tables that follow are derived from tests performed under the measurement conditions summarized in *Table 5: Operating and AC measurement conditions*. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

Table 5. Operating and AC measurement conditions

| Parameter                                       | Condition  | Unit   |

|-------------------------------------------------|------------|--------|

| V <sub>CC</sub> supply voltage                  | 2.7 to 5.5 | , (15) |

| Ambient operating temperature (T <sub>A</sub> ) | -30 to 85  | (C) C  |

| Input rise and fall times                       | ≤ 5        | ns     |

Note:

$V_{IN}$  assumed to be from 1.65 V to 5.5 V. No  $V_{IN}$  means no signal on OUT pin. If there is no  $V_{CC}$  then there will be no  $V_{IN}$ .

Table 6. DC and AC characteristics

| iable 0.                            | DC and AC characteristics                                                              |                                                                                                            |                       |                                     |                 |      |

|-------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------|-----------------|------|

| Sym                                 | Parameter                                                                              | Test condition <sup>(1)</sup>                                                                              | Min                   | Тур                                 | Max             | Unit |

| V <sub>CC</sub>                     | Supply voltage                                                                         |                                                                                                            | 2.7                   |                                     | 5.5             | V    |

|                                     | Complete surround index V                                                              | V <sub>EN</sub> = 0 V                                                                                      |                       | 0.6                                 | 1               | μA   |

| I <sub>CC</sub>                     | Supply current into V <sub>CC</sub> pin                                                | V <sub>EN</sub> = 4 V                                                                                      |                       | 1.5                                 | 15              | μΑ   |

| 1 . 1                               | Current into V . V nine                                                                | V <sub>EN</sub> = 0 V                                                                                      |                       |                                     | 5               | μΑ   |

| I <sub>CC</sub> + I <sub>IN</sub>   | Current into V <sub>CC</sub> + V <sub>IN</sub> pins                                    | V <sub>EN</sub> = 4 V                                                                                      |                       |                                     | 15              | μΑ   |

| V <sub>TH+</sub>                    | Rising voltage detector threshold (see <i>Table 8 on page 19</i> for detailed listing) |                                                                                                            | -3%                   | V <sub>TH+</sub>                    | +3%             | 54   |

| V <sub>HYST</sub>                   | Threshold hysteresis                                                                   |                                                                                                            | 0.3                   | (                                   | 0.5             | V    |

| V <sub>TH</sub> _                   | Falling voltage detector threshold                                                     |                                                                                                            |                       | V <sub>TH+</sub> -v <sub>FYS1</sub> |                 | V    |

| t <sub>PD-FALL</sub> <sup>(2)</sup> | V <sub>CC</sub> falling to OUT delay                                                   | V <sub>CC</sub> falling from<br>(V <sub>TH</sub> + 100 mV) to<br>(V <sub>TH</sub> - 100 mV) at<br>10 mV/µs | 10                    | 30                                  |                 | μs   |

| t <sub>PD-RISE</sub> <sup>(2)</sup> | V <sub>CC</sub> rising to OUT delay                                                    | $V_{CC}$ rising from $(V_{TH} - i O n N)$ to $(V_{TH} - i O m N)$ at 10 m $V/\mu s$                        |                       | 70                                  |                 | μs   |

| V <sub>IN</sub>                     | Voltage on V <sub>IN</sub> pin<br>Supply for output pin                                | Allows 2.5 V rail,<br>V <sub>BAT</sub> or +5 V                                                             | 2.4                   |                                     | 5.5             | V    |

| Output pin,                         | OUT <sup>(3)</sup>                                                                     |                                                                                                            |                       |                                     |                 |      |

| V <sub>OUT-OH</sub>                 | Output high vc tave                                                                    | I <sub>SOURCE</sub> = 5 mA                                                                                 | V <sub>IN</sub> - 0.2 |                                     | V <sub>IN</sub> | V    |

| V <sub>OUT-OL</sub>                 | Output ion voitage                                                                     | I <sub>SINK</sub> = 10 mA                                                                                  |                       |                                     | 0.3             | V    |

| l <sub>out</sub>                    | Cu su' current                                                                         |                                                                                                            | 5                     |                                     | 15              | mA   |

| Enable ing.                         | .t, EN                                                                                 |                                                                                                            |                       |                                     |                 |      |

|                                     | When VBUS is valid                                                                     |                                                                                                            | 1.2                   |                                     |                 | V    |

| $ V_{EN-IL}$                        | When VBUS is not valid                                                                 |                                                                                                            |                       |                                     | 0.4             | V    |

| I <sub>EN-IN</sub>                  | Enable input current                                                                   |                                                                                                            |                       |                                     | 0.1             | μA   |

|                                     | EN glitch immunity                                                                     |                                                                                                            | 1                     |                                     |                 | μs   |

| Inhibit inpu                        | it, INH                                                                                |                                                                                                            |                       |                                     |                 | •    |

| V <sub>INH–IH</sub>                 | Inhibit logic high                                                                     |                                                                                                            | 1.2                   |                                     |                 | V    |

| V <sub>INH–IL</sub>                 | Inhibit logic low                                                                      |                                                                                                            |                       |                                     | 0.4             | V    |

| V <sub>INH–IN</sub>                 | Inhibit input current                                                                  |                                                                                                            |                       |                                     | 0.1             | μΑ   |

|                                     | INH glitch immunity                                                                    |                                                                                                            | 1                     |                                     |                 | μs   |

DC and AC characteristics (continued) Table 6.

| Sym                 | Parameter                      | Test condition <sup>(1)</sup> | Min | Тур | Max | Unit |  |  |  |

|---------------------|--------------------------------|-------------------------------|-----|-----|-----|------|--|--|--|

| Pass gate I         | Pass gate between PKX and POX  |                               |     |     |     |      |  |  |  |

| R <sub>DS(on)</sub> | Static pass gate on resistance |                               |     | 300 |     | Ω    |  |  |  |

- 1. Valid for ambient operating temperature:  $T_A = -30$  °C to +85 °C;  $V_{CC} = 2.7$  V to 5.5 V (except where noted).

- 2. Guaranteed by design.

- obsolete Product(s). Obsolete Product(s) 3. For  $V_{CC}$  below  $V_{TH-}$ , the output remains low down to  $V_{CC}$  = 1 V. Below  $V_{CC}$  = 1 V the voltage  $V_{IN}$  must be less than  $V_{OUT-OL}$  (max.) to guarantee output low voltage less than 0.3 V.

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

Figure 12. Flip Chip 8-bump, package mechanical outline Pottom view Josolete P Top view

Figure 13. Flip Chip tape and reel specifications

Table 7. Flip chip 8-bump, package mechanical data

| Symbol |       | mm    |       | 96,   | inches |       |

|--------|-------|-------|-------|-------|--------|-------|

| Symbol | Min   | Тур   | Max   | Nin   | Тур    | Max   |

| Α      | 0.54  | 0.60  | 0.66  | 0.021 | 0.024  | 0.026 |

| A1     | 0.170 | 0.205 | 0.240 | 0.007 | 0.008  | 0.009 |

| A2     |       | 0.395 | 51    |       | 0.015  |       |

| b      | 0.215 | 0.255 | 0.295 | 0.008 | 0.010  | 0.012 |

| D      | 1.570 | 000.  | 1.605 | 0.062 | 0.063  | 0.063 |

| D1     | 01/   | 1.20  |       |       | 0.047  |       |

| е      | 0.55  | 0.40  | 0.44  | 0.014 | 0.016  | 0.017 |

| E      | 0.77  | 0.80  | 0.83  | 0.030 | 0.031  | 0.033 |

| [:1]   | 0.36  | 0.40  | 0.44  | 0.014 | 0.016  | 0.017 |

| SE     | 0.18  | 0.20  | 0.22  | 0.007 | 0.008  | 0.009 |

| f      |       | 0.20  |       |       | 0.008  |       |

| ccc    |       | 0.05  |       |       | 0.002  |       |

| \$     | 0.035 | 0.045 | 0.050 | 0.001 | 0.002  | 0.002 |

STM1068 Part numbering

# 7 Part numbering

- T = ECOPACK® package, tape and reel

- 1. Contact local ST sales office for availability.

- 2. Not recommended for new design. Contact local ST sales office for availability.

# 8 Package marking information

Table 9. Factory-trimmed thresholds with marking description

| Part number    | Rising voltage detector threshold V <sub>TH+</sub> at ambient temperature T <sub>A</sub> from -30 to +85 °C |      |           | Topside marking <sup>(1)</sup> |

|----------------|-------------------------------------------------------------------------------------------------------------|------|-----------|--------------------------------|

|                | Min (-3%)                                                                                                   | Тур  | Max (+3%) | Topside marking                |

| STM1068C20F38F | 3.104                                                                                                       | 3.20 | 3.296     | THS<br>yww                     |

| STM1068C25F38F | 3.152                                                                                                       | 3.25 | 3.348     | TIS<br>y w                     |

| STM1068C30F38F | 3.201                                                                                                       | 3.30 | 3.399     | iJS<br>yww                     |

| STM1068C35F38F | 3.249                                                                                                       | 3.35 | 3.451     | TKS<br>yww                     |

| STM1068C40F38F | 3.298                                                                                                       | 3.40 | 3.502     | TLS<br>yww                     |

| STM1068C45F38F | 3.346                                                                                                       | 3.45 | 3.554     | TMS<br>yww                     |

| STM1068C50F38F | 3.395                                                                                                       | 3.50 | 3.605     | TNS<br>yww                     |

<sup>1.</sup> Where "y" = assembly year (0 to 9) and "ww ' = ass en bly work week (01 to 52).

STM1068 Revision history

# 9 Revision history

Table 10. Document revision history

| Date       | Date        | Revision | Changes                                                                                                                         |  |

|------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 1-Aug-2007 | 31-Aug-2007 | 1        | Initial release.                                                                                                                |  |

| 7-Sep-2007 | 07-Sep-2007 | 2        | Updated cover page, Section 1: Description, Figure 3, and Table 6.                                                              |  |

| 3-Jan-2008 | 03-Jan-2008 | 3        | Updated Figure 1, 11, 13, and Table 3, 5, 6, 9; added Section 3: Typical operating characteristics; minor presentation changes. |  |

| 6-Mar-2008 | 26-Mar-2008 | 4        | Updated Table 6, 7.                                                                                                             |  |

| 9-Apr-2008 | 09-Apr-2008 | 5        | Document status upgraded to full datasheet; updated Figur # 12.                                                                 |  |

| 7-May-2008 | 27-May-2008 | 6        | Minor document reformatting.                                                                                                    |  |

| 6-Mar-2010 | 16-Mar-2010 | 7        | Document reformatted, updated ECOPACK® text in Section 6, corrected Figure 13.                                                  |  |

| 2-Sep-2010 | 22-Sep-2010 | 8        | Device not recommended for new (es gr. (updated document status and <i>Table 8</i> ).                                           |  |

| SProd      | e Pro       | ductle   | a) Obsoleite                                                                                                                    |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia. 'ea (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and sen ices described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services the cribed herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property 1.3, is s granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a cer se grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a aa ranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained in the services or any intellectual property contained in the services.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PROD JC'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP ENTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p. or ucts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war and granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liabi.<sup>it</sup>; \tau \( \ii \) Γ.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

22/22 Doc ID 13864 Rev 8