Errata sheet

# Limitations of the VD55G1

## Introduction

This document covers the known limitations of the VD55G1, and workarounds, when available.

## 1 I2C/I3C

## 1.1 Repeated start

There is a limitation in the case of Read from Random Location that must always be initiated with a Start condition (not a repeated start).

#### Workaround

Always initiate Read from Random Location with Start condition (not a repeated start).

## 1.2 I3C image readout

GPIO to start image readout cannot be triggered once at the beginning at the frame. GPIO is triggered every line to read a line.

#### Workaround

None

ES0643 - Rev 1 page 2/12

## 2 GPIOs

### 2.1 Extra strobe sent in overlap

When the exposure overlaps over frames, a strobe/integration is present after the last frame readout.

#### Workaround

None

## 2.2 Strobe signal does not match exposure register

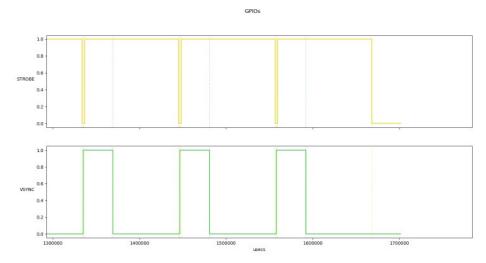

The strobe signal length is the integration time plus 1 line. As represented in the figure below, the strobe signal begins a half-line time before, and ends a half-line time after the integration.

#### Workaround

None

## 2.3 PWM strobe edge synchronization

PWM is not synchronized with strobe output. This means that the PWM and strobe edge are not aligned. If the number of PWM cycles in the strobe envelope is low, it can affect the actual duty cycle.

#### Workaround

None

## 2.4 GPIOs in STANDBY state

The control of GPIOs while in SW STBY state is not supported.

#### Workaround

None

ES0643 - Rev 1 page 3/12

## 2.5 VSYNC start delay does not support negative values

VSYNC start delay is a signed value of the delay to apply in lines. This register accepts only values [0-127]. Values [128-255] are not supported.

ES0643 - Rev 1 page 4/12

## 3 PLL

## 3.1 Fractional part

The fractional part of the PLL does not work. The PLL device cannot generate any MIPI frequency from the input clock.

#### Workaround

The output clock must always be a multiple of the input clock. For example, 1200 Mbps for a 12 MHz clock.

## **3.2** MIPI data rate 751-780 Mbps

The pixel clock exceeds it specification range (> 150 MHz) when using the MIPI data-rate in the range [750, 780].

#### Workaround

None. Do not use the MIPI data rate of [750, 780].

## 3.3 MIPI data rate 400-450 and 800-900 Mbps

The charge pumps are not correctly set in the range [400-450] and [800-900] Mbps. In this range, the sensor cannot reach the saturation level, but a column FPN is visible.

#### Workaround

None, do not use the MIPI data rate of [400-450] and [800-900] Mbps.

ES0643 - Rev 1 page 5/12

# 4 Autoexposure

## 4.1 Dual autoexposure

If the dual autoexposure feature is activated, the minimum frame margin is not enough.

#### Workaround

Add 25 lines to the minimum frame length.

ES0643 - Rev 1 page 6/12

## 5 QVGA at 480 fps cannot support all features

QVGA at 480 fps is very aggressive in terms of frame rate and cannot be guaranteed in all conditions.

#### Workaround

QVGA @480fps can be achieved with the following dedicated settings:

- WRITE REG8 STREAM STATICS OIF ULPM 'h01 # MIPI in ULPM

- WRITE\_REG8 DBG\_FULL\_READ\_OFFSET\_9BIT 'h1F # 31

- WRITE\_REG8 DBG\_FW\_LATCH\_TIME 'h0A # 10

- WRITE\_REG8 STREAM\_STATICS\_FORMAT\_CTRL 'h08 # RAW8

- WRITE\_REG8 STREAM\_STATICS\_VT\_CTRL 'h04 # VT 9 bits

- WRITE\_REG8 STREAM\_CTX0\_READOUT\_CTRL 'h06 # 0x06: (XYBIN\_X2)

- WRITE\_REG8 STREAM\_STATICS\_LINE\_LENGTH 'h03D2 # 978 pixels 9 bits

- WRITE\_REG8 EXPO\_MANUAL\_COARSE\_EXP 'h00C8 # 200 lines

- WRITE\_REG8 STREAM\_CTX0\_Y\_HEIGHT 'h01E0 # 480 lines

- WRITE\_REG8 STREAM\_CTX0\_X\_WIDTH 'h0280 # 640 lines

- WRITE REG8 STREAM CTX0 FRAME LENGTH 'h013F # 319 lines

- WRITE\_REG8 CHANNEL\_STATS\_ROI\_REDUCE\_FACTOR 'h10 # 16 lines removed to the stats ROI

ES0643 - Rev 1 page 7/12

## 6 Low power

The device enables the low power as soon as the interframe is long enough. The interframe is computed as below:

Low power Inter Frame = Frame length - Coarse Integration - Output Y size -100

Note:

Coarse integration time must be doubled when in subtraction mode.

As soon as the **Low power Interframe** exceeds a value of 509, the sensor activates the low power. The formula to find the maximum integration time to be always in low power is the following:

Max integration time for low power = Frame length - 509 - Output Y size -100

For example, the application should limit the integration time to 6.79 ms to always have the benefit of this low-power mechanism with the following configuration:

Table 1. Low-power configuration

| MIPI data rate                     | 1200 Mbps                          |

|------------------------------------|------------------------------------|

| Line time                          | 7.52 us (Line length = 1128)       |

| Output resolution                  | 804x704                            |

| Frame rate                         | 60 fps (frame length = 2216)       |

| Max integration time for low power | 6.79 ms (coarse integration = 903) |

### 6.1 Missing frames

The device misses frames when switching (on the fly) between low power feasible and low power.

#### **Workaround 1**

Always keep the integration time below the Max integration time for low power. One easy way is to use the <code>EXPOSURE\_USER\_MAX\_COARSE\_INTEGRATION\_LINES</code> register.

#### Workaround 2

The application can disable the low power mechanism with ENABLE LOW POWER MODE register.

Table 2. ENABLE\_LOW\_POWER\_MODE register definition

| Register name    | ENABLE_LOW_POWER_MODE          |

|------------------|--------------------------------|

| Register address | 0x976                          |

| Register size    | 8 bits                         |

| Register values  | 0: Low power disabled          |

|                  | 1: Low power enabled (Default) |

ES0643 - Rev 1 page 8/12

# 7 Slave mode

When using the slave mode of the GPIO\_0, polarity cannot be changed.

Workaround

None

ES0643 - Rev 1 page 9/12

# **Revision history**

Table 3. Document revision history

| Date        | Version | Changes         |

|-------------|---------|-----------------|

| 29-Nov-2024 | 1       | Initial release |

ES0643 - Rev 1 page 10/12

# **Contents**

| 1  | I2C/ | I2C/I3C                                            |   |  |  |

|----|------|----------------------------------------------------|---|--|--|

|    | 1.1  | Repeated start                                     | 2 |  |  |

|    | 1.2  | I3C image readout                                  | 2 |  |  |

| 2  | GPI  | Os                                                 | 3 |  |  |

|    | 2.1  | Extra strobe sent in overlap                       | 3 |  |  |

|    | 2.2  | Strobe signal does not match exposure register     | 3 |  |  |

|    | 2.3  | PWM strobe edge synchronization                    | 3 |  |  |

|    | 2.4  | GPIOs in STANDBY state                             | 3 |  |  |

|    | 2.5  | VSYNC start delay does not support negative values | 4 |  |  |

| 3  | PLL  | PLL                                                |   |  |  |

|    | 3.1  | Fractional part                                    | 5 |  |  |

|    | 3.2  | MIPI data rate 751-780 Mbps                        | 5 |  |  |

|    | 3.3  | MIPI data rate 400-450 and 800-900 Mbps            | 5 |  |  |

| 4  | Auto | oexposure                                          | 6 |  |  |

|    | 4.1  | Dual autoexposure                                  | 6 |  |  |

| 5  | QVO  | GA at 480 fps cannot support all features          | 7 |  |  |

| 6  | Low  | <i>y</i> power                                     | 8 |  |  |

|    | 6.1  | Missing frames                                     | 8 |  |  |

| 7  | Slav | /e mode                                            | 9 |  |  |

| Re |      | history                                            |   |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

ES0643 - Rev 1 page 12/12