# UM0438 User manual

# Variable-Length Encoding (VLE) extension programming interface manual

#### Introduction

This user manual defines a programming model for use with the variable-length encoding (VLE) instruction set extension. Three types of programming interfaces are described herein:

- An application binary interface (ABI) defining low-level coding conventions

- An assembly language interface

- A simplified mnemonic assembly language interface

Contents UM0438

## **Contents**

| Preface . |        |                                                  | 7 |

|-----------|--------|--------------------------------------------------|---|

|           | About  | this book                                        | 7 |

|           | Audier | nce                                              | 7 |

|           | Organ  | iization                                         | 7 |

|           | Sugge  | ested reading                                    | 7 |

|           | Relate | ed documentation                                 | 3 |

|           | Gener  | ral information                                  | 3 |

|           | Conve  | entions                                          | 3 |

|           | Termir | nology conventions                               | 9 |

|           | Acrony | yms and abbreviations                            | ) |

| 1         | Overv  | view11                                           | ı |

|           | 1.1    | Application Binary Interface (ABI)               |   |

|           | 1.2    | Assembly language interface                      |   |

|           | 1.3    | Simplified mnemonics assembly language interface |   |

| 2         | Appli  | cation Binary Interface (ABI)                    | 2 |

| _         | 2.1    | Instruction and data representation              |   |

|           | 2.2    | Executable and Linking Format (ELF) object files |   |

|           |        | 2.2.1 VLE information section                    |   |

|           |        | 2.2.2 VLE identification                         |   |

|           |        | 2.2.3 Relocation types                           | 5 |

| 3         | Instru | uction set                                       | ) |

| Appendix  | A Si   | implified mnemonics for VLE instructions         | 2 |

|           | A.1    | Overview                                         | 2 |

|           | A.2    | Subtract simplified mnemonics                    | 2 |

|           |        | A.2.1 Subtract immediate                         | 2 |

|           |        | A.2.2 Subtract                                   | 3 |

|           | A.3    | Rotate and shift simplified mnemonics            | 3 |

|           |        | A.3.1 Operations on words                        | 1 |

|           | A.4    | Branch instruction simplified mnemonics          | 1 |

| 2/50      |        |                                                  | - |

UM0438 Contents

|          |      | A.4.1     | Key facts about simplified branch mnemonics                                                                 | 26 |

|----------|------|-----------|-------------------------------------------------------------------------------------------------------------|----|

|          |      | A.4.2     | Eliminating the BO32 and BO16 operands                                                                      | 26 |

|          |      | A.4.3     | The BI32 and BI16 operand—CR Bit and field representations                                                  | 27 |

|          |      | A.4.4     | BI32 and BI16 operand instruction encoding                                                                  | 28 |

|          | A.5  | Simplifie | ed mnemonics that incorporate the BO32 and BO16 operands :                                                  | 31 |

|          |      | A.5.1     | Examples that eliminate the BO32 and BO16 operands                                                          | 31 |

|          |      | A.5.2     | Simplified mnemonics that incorporate CR conditions (eliminates BO32 and BO16 and replaces BI32 with crS)33 |    |

|          |      | A.5.3     | Branch simplified mnemonics that incorporate CR conditions: examples 35                                     |    |

|          |      | A.5.4     | Branch simplified mnemonics that incorporate CR conditions: listings. $\boldsymbol{.}$                      | 35 |

|          | A.6  | Compar    | e word simplified mnemonics                                                                                 | 36 |

|          | A.7  | Trap ins  | tructions simplified mnemonics                                                                              | 37 |

|          | A.8  | Simplifie | ed mnemonics for accessing SPRs                                                                             | 39 |

|          | A.9  | Recomr    | nended simplified mnemonics                                                                                 | 40 |

|          |      | A.9.1     | No-Op( <b>nop</b> )                                                                                         | 40 |

|          |      | A.9.2     | Load Address (la)                                                                                           | 40 |

|          |      | A.9.3     | Move Register ( <b>mr</b> )                                                                                 | 40 |

|          |      | A.9.4     | Complement Register ( <b>not</b> )                                                                          | 40 |

|          |      | A.9.5     | Move to Condition Register (mtcr)                                                                           | 40 |

|          | A.10 | EIS-Spe   | ecific simplified mnemonics                                                                                 | 41 |

|          |      | A.10.1    | Integer Select (isel)                                                                                       | 41 |

|          | A.11 | Compre    | hensive list of simplified mnemonics                                                                        | 41 |

| Appendix | B G  | lossary   |                                                                                                             | 45 |

|          |      | Α         |                                                                                                             | 45 |

|          |      | В         |                                                                                                             | 45 |

|          |      | _         |                                                                                                             | _  |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             | _  |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             |    |

|          |      |           |                                                                                                             |    |

|          |      | п         |                                                                                                             | 4/ |

| 4 | Revision history |

|---|------------------|

|   | W                |

|   | U48              |

|   | T48              |

|   | S47              |

|   |                  |

UM0438 List of tables

# List of tables

| Table 1.  | Terminology conventions                                                             | 9  |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 2.  | Acronyms and abbreviated terms                                                      | 9  |

| Table 3.  | Typical Elf note section format                                                     | 13 |

| Table 4.  | VLE identifier                                                                      | 13 |

| Table 5.  | VLE relocation fields                                                               | 15 |

| Table 6.  | VLE relocation field descriptions                                                   | 16 |

| Table 7.  | Notation conventions                                                                | 16 |

| Table 8.  | VLE relocation types                                                                | 17 |

| Table 9.  | Relocation types with special semantics                                             | 19 |

| Table 10. | Subtract immediate simplified mnemonics                                             | 23 |

| Table 11. | Subtract simplified mnemonics                                                       | 23 |

| Table 12. | Word rotate and shift simplified mnemonics                                          | 24 |

| Table 13. | Branch instructions                                                                 | 25 |

| Table 14. | BO32 and BO16 operand encodings                                                     |    |

| Table 15. | CR0 and CR1 fields as updated by integer and floating-point instructions            | 29 |

| Table 16. | BI32 and BI16 operand settings for CR fields for branch comparisons                 |    |

| Table 17. | CR field identification symbols                                                     | 30 |

| Table 18. | Branch simplified mnemonics                                                         | 31 |

| Table 19. | Branch instructions                                                                 | 31 |

| Table 20. | Simplified mnemonics for <b>e_bc</b> and <b>se_bc</b> without LR update             |    |

| Table 21. | Simplified mnemonics for <b>e_bcl</b> with LR update                                | 32 |

| Table 22. | Standard coding for branch conditions                                               |    |

| Table 23. | Branch instructions and simplified mnemonics that incorporate CR conditions         | 34 |

| Table 24. | Simplified mnemonics with comparison conditions                                     | 34 |

| Table 25. | Simplified mnemonics for <b>e_bc</b> and <b>se_bc</b> without comparison conditions |    |

|           | or LR updating35                                                                    |    |

| Table 26. | Simplified mnemonics for <b>e_bcl</b> with comparison conditions and LR updating    |    |

| Table 27. | Word compare simplified mnemonics                                                   |    |

| Table 28. | Standard codes for trap instructions                                                |    |

| Table 29. | Trap simplified mnemonics                                                           |    |

| Table 30. | TO operand Bit Encoding                                                             |    |

| Table 31. | Additional simplified mnemonics for Accessing SPRGs                                 |    |

| Table 32. | Simplified mnemonics                                                                | 41 |

| Table 33. | Document revision history                                                           | 49 |

List of figures UM0438

# **List of figures**

6/50

| Figure 1. | Branch conditional (e_bc, se_bc) instruction formats | 25   |

|-----------|------------------------------------------------------|------|

| Figure 2. | BI32 and BI16 fields                                 | . 28 |

UM0438 Preface

#### **Preface**

#### **About this book**

The primary objective of this manual is to help programmers provide software that is compatible across the family of processors using variable-length encoding (VLE) extension.

Individual VLE technology implementations are beyond the scope of this manual. Each processor is unique in its implementation of the VLE extension.

The information in this book is subject to change without notice. As with any technical documentation, it is the reader's responsibility to ensure they are using the most recent version of the documentation. For more information, contact your sales representative.

#### **Audience**

This manual is for system software and application programmers who want to develop products using the VLE extension. An understanding of operating systems, microprocessor system design, the basic principles of RISC processing, and the VLE instruction set is assumed.

### **Organization**

Following is a summary of the major sections of this manual:

- Section 1: Overview provides a general understanding of what the programming model defines in the VLE extension.

- Section 2: Application Binary Interface (ABI) describes the VLE extensions for the PowerPC™ e500 Application Binary Interface (e500 ABI) to support VLE technology.

- Section 3: Instruction set provides an overview of the VLE instruction set architecture.

For a detailed description of each instruction, including assembly language syntax, refer to the VLE section of the EREF.

- Appendix A: Simplified mnemonics for VLE instructions describes simplified mnemonics, which are provided for easier coding of assembly language programs using VLE technology.

## **Suggested reading**

This section lists background reading for this manual as well as general information on the VLE extension and PowerPC architecture.

Preface UM0438

#### **Related documentation**

STMicroelectronics processor documentation is organized in the following types of documents:

- RM0004: A Programmer 's Reference Manual for Book E processor A higher-level view of the programming model as it is defined by Book E

- User's manuals—Provide details on individual implementations and are for use with the Programming Environments Manual for 32-Bit Implementations of the PowerPC™ Architecture

- Datasheet—Specific data regarding bus timing, signal behavior, and AC, DC, and thermal characteristics, as well as other design considerations.

- Application notes—Address-specific design issues useful to programmers and engineers working with STMicroelectronics processors.

Additional literature is released as new processors become available.

#### **General information**

The following documentation, published by Morgan-Kaufmann Publishers, 340 Pine Street, Sixth Floor, San Francisco, CA, provides useful information on the PowerPC architecture and computer architecture in general:

- The PowerPC Architecture: A Specification for a New Family of RISC Processors, Second Edition, by International Business Machines, Inc.

- For updates to the specification, see http://www.austin.ibm.com/tech/ppc-chg.html.

- Computer Architecture: A Quantitative Approach, Third Edition, by John L. Hennessy and David A. Patterson

- Computer Organization and Design: The Hardware/Software Interface, Second Edition, David A. Patterson and John L. Hennessy

#### Conventions

This document uses the following notational conventions:

cleared/set When a bit takes the value zero, it is said to be cleared; when it

takes a value of one, it is said to be set.

mnemonics Instruction mnemonics are shown in lowercase bold.

italics Italics indicate variable command parameters, for example, bcctrx.

Book titles in text are set in italics.

Internal signals are set in italics, for example,  $\overline{qual} \ \overline{BG}$ .

0x0 Prefix to denote hexadecimal number

0b0 Prefix to denote binary number

rA, rB Instruction syntax used to identify a source GPRrD Instruction syntax used to identify a destination GPR

REG[FIELD] Abbreviations for registers are shown in uppercase text. Specific

bits, fields, or ranges appear in brackets. For example, MSR[LE] refers to the little-endian mode enable bit in the machine state

register.

UM0438 Preface

| x | In some contexts, such as signal encodings, an unitalicized x indicates a don't care. |

|---|---------------------------------------------------------------------------------------|

| X | An italicized x indicates an alphanumeric variable.                                   |

| n | An italicized <i>n</i> indicates an numeric variable.                                 |

| ٦ | NOT logical operator                                                                  |

| & | AND logical operator                                                                  |

| 1 | OR logical operator                                                                   |

## **Terminology conventions**

*Table 1* lists certain terms used in this manual that differ from the architecture terminology conventions.

Table 1. Terminology conventions

| Architecture specification            | This manual                 |

|---------------------------------------|-----------------------------|

| Change bit                            | Changed bit                 |

| Extended mnemonics                    | Simplified mnemonics        |

| Out of order memory accesses          | Speculative memory accesses |

| Privileged mode (or privileged state) | Supervisor level            |

| Problem mode (or problem state)       | User level                  |

| Reference bit                         | Referenced bit              |

| Relocation                            | Translation                 |

| Storage (locations)                   | Memory                      |

| Storage (the act of)                  | Access                      |

## Acronyms and abbreviations

Table 2 contains acronyms and abbreviations that are used in this document.

Table 2. Acronyms and abbreviated terms

| Term | Meaning                                           |

|------|---------------------------------------------------|

| CR   | Condition register                                |

| CTR  | Count register                                    |

| DCR  | Data control register                             |

| DTLB | Data translation lookaside buffer                 |

| EA   | Effective address                                 |

| ECC  | Error checking and correction                     |

| FPR  | Floating-point register                           |

| GPR  | General-purpose register                          |

| IEEE | Institute of Electrical and Electronics Engineers |

Preface UM0438

Table 2. Acronyms and abbreviated terms (continued)

| Term  | Meaning                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------|

| ITLB  | Instruction translation lookaside buffer                                                               |

| L2    | Secondary cache                                                                                        |

| LIFO  | Last-in-first-out                                                                                      |

| LR    | Link register                                                                                          |

| LRU   | Least recently used                                                                                    |

| LSB   | Least-significant byte                                                                                 |

| Isb   | Least-significant bit                                                                                  |

| MMU   | Memory management unit                                                                                 |

| MSB   | Most-significant byte                                                                                  |

| msb   | Most-significant bit                                                                                   |

| MSR   | Machine state register                                                                                 |

| NaN   | Not a number                                                                                           |

| NIA   | Next instruction address                                                                               |

| No-op | No operation                                                                                           |

| PTE   | Page table entry                                                                                       |

| RISC  | Reduced instruction set computing                                                                      |

| RTL   | Register transfer language                                                                             |

| SIMM  | Signed immediate value                                                                                 |

| SPR   | Special-purpose register                                                                               |

| TLB   | Translation lookaside buffer                                                                           |

| UIMM  | Unsigned immediate value                                                                               |

| UISA  | User instruction set architecture                                                                      |

| VA    | Virtual address                                                                                        |

| VLE   | Variable-length encoding                                                                               |

| XER   | Register used primarily for indicating conditions such as carries and overflows for integer operations |

UM0438 Overview

## 1 Overview

This document defines a programming model for use with the variable-length encoding (VLE) instruction set extension. Three types of programming interfaces are described herein:

- An application binary interface (ABI) defining low-level coding conventions

- An assembly language interface

- A simplified mnemonic assembly language interface

### 1.1 Application Binary Interface (ABI)

The VLE programming model extends the existing PowerPC™ ABIs. This extension is independent of the endian mode with regard to data; however, VLE instructions are supported only in big-endian mode. The ABI reviews instruction and data representations for memory management and distinguishes between PowerPC Book E and VLE instructions. The ABI also discusses VLE section identification and relocation types used by the executable and linking format (ELF).

Note:

Use this chapter in conjunction with the PowerPC e500 Application Binary Interface (e500 ABI). Except for the sections discussed in this chapter, the VLE ABI follows the e500 ABI standard. For information on register usage and availability, function calling sequence, parameter passing, stack frames, and other topics, refer to the e500 ABI.

## 1.2 Assembly language interface

The assembly language interface provides an overview of the VLE instructions. The description of each instruction along with the instruction mnemonic and operands can be found in the VLE section of the EREF.

## 1.3 Simplified mnemonics assembly language interface

Simplified mnemonics are provided for easier coding of assembly language programs. They are defined for the most frequently used forms of branch conditional, compare, trap, rotate and shift, and certain other instructions defined by the VLE extension. Some assemblers may define additional simplified mnemonics not listed in this document; however, all assemblers should support the VLE simplified mnemonics listed in Appendix A.

## 2 Application Binary Interface (ABI)

Note:

The ABI extensions described herein for VLE applications are still under review by the PowerPC ABI industry working group and may be subject to change. Any modifications will be highlighted in revisions of this document.

This chapter specifies VLE extensions to the PowerPC e500 Application Binary Interface (e500 ABI) that defines both a big-endian and a little-endian ABI. This VLE ABI extension is independent of the endian mode with regards to data; however, VLE instructions are supported only in big-endian mode.

Note:

This chapter should be used in conjunction with the PowerPC e500 Application Binary Interface (e500 ABI). Except for the sections discussed in this chapter, the VLE ABI follows the e500 ABI standard. For information on topics not covered in this section, including function calling sequence, register usage and availability, stack frame layout, parameter passing, and other topics, please refer to the e500 ABI.

#### 2.1 Instruction and data representation

The VLE extension includes additional operations with an alternate instruction encoding to enable reduced code footprint. This alternate encoding set is selected on an instruction page basis. A single page attribute bit selects between standard PowerPC Book E instruction encodings and the VLE instructions for the particular page of memory. This page attribute is an extension to the existing PowerPC Book E page attributes. Pages can be freely intermixed, allowing for a mixture of code with both types of encodings.

Instruction encodings in pages marked as using VLE are either 16 or 32 bits long and are aligned on 16-bit boundaries. Therefore, all instruction pages marked as VLE must use bigendian byte ordering.

The programmer's model uses the same register set when executing either instruction encoding, although certain registers are not accessible to VLE instructions using the 16-bit formats, and not all fields of the condition register (CR) are used by condition setting or conditional branch instructions when executing from a VLE instruction page. In addition, immediate fields and displacements differ in size and use, due to the more restrictive encodings imposed by VLE instructions.

Other than the requirement of big-endian byte ordering for instruction pages, and the additional page attribute to identify whether the instruction page corresponds to a VLE section of code, VLE uses the identical storage model, interrupts and exceptions, timer facilities, debug facilities, and special-purpose registers (SPRs) defined throughout Book E.

## 2.2 Executable and Linking Format (ELF) object files

Both VLE and Book E instructions can coexist in the same ELF binary separated into different ELF sections allowing easy identification for defining memory management page tables for run-time environments. Because implementations supporting VLE use an extension to the existing PowerPC Book E page attributes, providing a single additional page attribute to select between VLE and Book E encodings, memory pages of VLE and Book E instructions can be freely intermixed. Binding of VLE and Book E memory pages to different memory bounds requires separation of VLE and Book E encodings into different ELF sections.

The VLE encodings also require additional relocation types, which allow the linker to resolve immediate and branch displacement fields in the instruction encoding once a symbol or label address is known (at link time). The VLE encodings require additional relocation types to resolve fields not present in the PowerPC Book E encodings.

#### 2.2.1 VLE information section

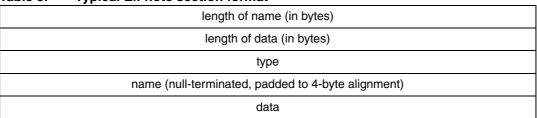

The e500 ABI defines an information section named .PPC.EMB.apuinfo having type SHT\_NOTE and attributes of 0, which matches the format of a typical ELF note section as shown in *Table 3*. The information section allows disassemblers and debuggers to interpret the instructions properly within the binary and can be used by operating systems to provide emulation or error checking of the VLE extension revisions.

Table 3. Typical Elf note section format

For the .PPC.EMB.apuinfo section, the name is APUinfo the type is 2 (as type 1 is already reserved), and the data contains a series of words providing information about the APU or extension, one per word. The information contains two unsigned half words: the upper half contains the unique identifier, and the lower half contains the revision number. The VLE identifier is shown in *Table 4*.

Table 4. VLE identifier

| Identifier (16 Bits) | APU/Extension |  |

|----------------------|---------------|--|

| 0x0104               | VLE           |  |

#### Example - Object file a.o

| 0  | 0x00000008 | # 8 bytes in<br>"APUinfo\0"                |

|----|------------|--------------------------------------------|

| 4  | 0x000000C  | # 12 bytes (3 words)<br>of APU information |

| 8  | 0x0000002  | # NOTE type 2                              |

| 12 | 0x41505569 | # ASCII for "APUi"                         |

| 16 | 0x6e666f00 | # ASCII for "nfo\0"                        |

| 20 | 0x00010001 | # APU #1, revision 1                       |

| 24 | 0x01040001 | # VLE, revision 1                          |

| 28 | 0x00040001 | # APU #4, revision 1                       |

| Example -   | Ohio | ect fi   | ile b | <u>.</u> |

|-------------|------|----------|-------|----------|

| LAGIIIDIC - | VDI  | - O L II | пси   | . •      |

| 0  | 0x0000008  | # 8 bytes in<br>"APUinfo\0"               |

|----|------------|-------------------------------------------|

| 4  | 0x0000008  | # 8 bytes (2 words)<br>of APU information |

| 8  | 0x0000002  | # NOTE type 2                             |

| 12 | 0x41505569 | # ASCII for "APUi"                        |

| 16 | 0x6e666f00 | # ASCII for "nfo\0"                       |

| 20 | 0x00010002 | # APU #1, revision 2                      |

| 24 | 0x00040001 | # APU #4, revision 1                      |

Linkers merge all .PPC.EMB.apuinfo sections in individual object files into one, with merging of per-APU information. For example, after linking file a.o and b.o, the merged .PPC.EMB.apuinfo is as shown in example below.

#### **Example - PPC.EMB.apuinfo**

| 0  | 0x0000008  | # 8 bytes in<br>"APUinfo\0"                |

|----|------------|--------------------------------------------|

| 4  | 0x000000C  | # 12 bytes (3 words)<br>of APU information |

| 8  | 0x0000002  | # NOTE type 2                              |

| 12 | 0x41505569 | # ASCII for "APUi"                         |

| 16 | 0x6e666f00 | # ASCII for "nfo\0"                        |

| 20 | 0x00010002 | # APU #1, revision 2                       |

| 24 | 0x01040001 | # VLE, revision 1                          |

| 28 | 0x00040001 | # APU #4, revision 1                       |

Note that it is assumed that a later revision of any APU or extension is compatible with an earlier one, but not *vice versa*. Thus, the resultant .PPC.EMB.apuinfo section requires APU #1 revision 2 or greater to work, and does not work on APU #1 revision 1. If a revision breaks backwards compatibility, it must be given a new unique identifier.

A linker may optionally warn when different objects require different revisions, because moving the revision up may make the executable no longer work on processors with the older revision. In this example, the linker could emit a warning like "Warning: bumping APU #1 revision number to 2, required by b.o."

#### 2.2.2 VLE identification

The executable and linking format (ELF) allows processor-specific section header and program header flag attributes to be defined. The following section header and program header flag attribute definitions are used to mark ELF sections containing VLE instruction encodings.

The SHF\_PPC\_VLE flag marks ELF sections containing VLE instructions. Similarly, the PF\_PPC\_VLE flag is used by ELF program headers to mark program sections containing VLE instructions. If either the SHF\_PPC\_VLE flag or the PF\_PPC\_VLE flag is set, then instructions in those marked sections are interpreted as VLE instructions; Book E instructions reside in sections that do not have these flags set.

ELF sections setting the SHF\_PPC\_VLE flag that contain VLE instructions should also use the SHF\_ALLOC and SHF\_EXECINSTR bits as necessary. Setting the SHF\_PPC\_VLE bit does not automatically imply a section that is marked as *allocate* (*SHF\_ALLOC*) or *executable* (*SHF\_EXECINSTR*). The linker keeps sections marked as VLE (SHF\_PPC\_VLE) in separate output sections that do not contain Book E instructions.

Similarly, ELF program headers setting the PF\_PPC\_VLE flag should use the PF\_X, PF\_W, and PF\_R flags to indicate executable, writable, or readable attributes. It is considered an error for a program header with PF\_PPC\_VLE set to contain sections that do not have SHF\_PPC\_VLE set.

A program loader or debugger can then scan the section headers or program headers to detect VLE sections in case anything special is required for section processing or downloading.

#### 2.2.3 Relocation types

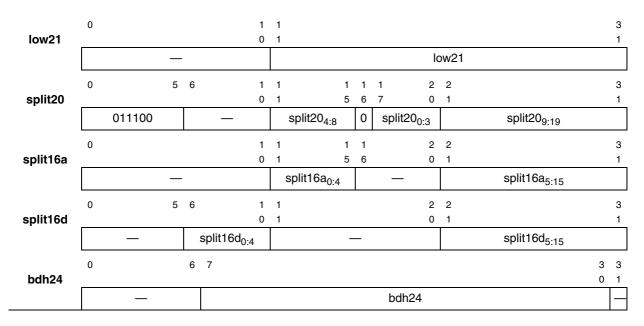

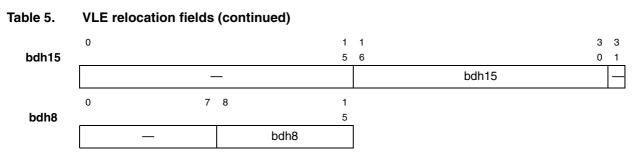

Relocation entries describe how to alter the instruction relocation fields once symbols or labels are defined at link time. The VLE instruction set requires relocation types beyond those described in the PowerPC e500 Application Binary Interface (e500 ABI). *Table 5* shows additional relocation fields used by the VLE instruction set.

Table 5. VLE relocation fields

Relocation field name

Table 6 describes the additional relocation fields required by VLE instructions.

Table 6. VLE relocation field descriptions

| Field    | Descriptions                                                                                                                                                                                                                                                                                                             |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| low21    | 21-bit field occupying the lsbs of a word (bits 11-31).                                                                                                                                                                                                                                                                  |

| split20  | 20-bit field with the 4 msbs occupying bits 17–20, the next 5 bits occupying bits 11–15, and the remaining 11 bits occupying bits 21–31. In addition, bits 0–5 in the destination word are encoded with the binary value 011100, bit 16 is encoded with the binary value 0.                                              |

| Spiit20  | This relocation field specifies the opcode for the VLE <b>e_li</b> instruction, allowing the linker to force the encoding of the <b>e_li</b> instruction, potentially changing the user's specified instruction. This functionality supports small data area relocation types. (R_PPC_VLE_SDA21 and R_PPC_VLE_SDA21_LO). |

| split16a | 16-bit field with the 5 msbs occupying bits 11–15 (the rA field) and the remaining 11 bits occupying bits 21–31.                                                                                                                                                                                                         |

| split16d | 16-bit field with the 5 msbs occupying bits 6–10 (the ${\bf r}{\bf D}$ field) and the remaining 11 bits occupying bits 21–31.                                                                                                                                                                                            |

| bdh24    | 24-bit field occupying bits 7–30 used to resolve branch displacements to half-word boundaries.                                                                                                                                                                                                                           |

| bdh15    | 15-bit field occupying bits 16–30 used to resolve branch displacements to half-word boundaries.                                                                                                                                                                                                                          |

| bdh8     | 8-bit field occupying bits 8–15 of a half-word. This field is used by a 16-bit branch instruction.                                                                                                                                                                                                                       |

Note:

Relocation entry types applied to VLE sections use half-word alignment boundaries, because the VLE instruction architecture mixes 16- and 32-bit encodings within a VLE section. Book E instruction encodings in non-VLE sections use e500 ABI alignment specifications.

Calculations in *Table 8* assume the actions are transforming a relocatable file into either an executable or a shared object file. Conceptually, the link editor merges one or more relocatable files to form the output. It determines how to combine and locate the input files, updates the symbol values, and then performs relocations. Relocations applied to executable or shared object files are similar and accomplish the same result. The notations used in *Table 8* are described in *Table 7*.

Table 7. Notation conventions

| Field | Descriptions                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------|

| Α     | Represents the addend used to compute the value of the relocatable field.                                       |

| Р     | Represents the place (section offset or address) of the storage unit being relocated (computed using r_offset). |

| S     | Represents the value of the symbol whose index resides in the relocation entry.                                 |

Table 7. Notation conventions (continued)

| Field | Descriptions                                                                                                                                                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х     | Represents the offset from the appropriate base (_SDA_BASE_, _SDA2_BASE_, or 0) to where the linker placed the symbol whose index is in r_info.                                                                                                                                                                                |

| Y     | Represents a 5-bit value for the base register for the section where the linker placed the symbol whose index is in r_info. Acceptable values are: the value 13 for symbols in .sdata or .sbss, the value 2 for symbols in .PPC.EMB.sdata2 or .PPC.EMB.sbss2, or the value 0 for symbols in .PPC.EMB.sdata0 or .PPC.EMB.sbss0. |

Relocation entries apply to half words or words. In either case, the r\_offset value designates the offset or virtual address of the first byte of the affected storage unit. The relocation type specifies which bits to change and how to calculate their values. Processors that implement the PowerPC architecture use only the Elf32\_Rela relocation entries with explicit addends. For relocation entries, the r\_addend member serves as the relocation addend. In all cases, the offset, addend, and the computed result use the byte order specified in the ELF header.

The following general rules apply to the interpretation of the relocation types in Table 8.

- + and denote 32-bit modulus addition and subtraction.

- Il denotes concatenation of bits or bit fields.

- >> denotes arithmetic right-shifting (shifting with sign copying) of the value of the left operand by the number of bits given by the right operand.

- For relocation types associated with branch displacements, in which the name of the relocation type contains 8, the upper 24 bits of the computed value before shifting must all be the same (either all zeros or all ones—that is, sign-extended displacement). For relocation types in which the name contains 15, the upper 17 bits of the computed value before shifting must all be the same. For relocation types in which the name contains 24, the upper 7 bits of the computed value before shifting must all be the same. For relocation types whose names contain 8, 15, or 24, the low 1-bit of the computed value before shifting must be zero (half-word boundary).

- #hi(value) and #lo(value) denote the 16 msbs and lsbs of the indicated value. That is, #lo(x)=(x & 0xFFFF) and #hi(x)=((x>>16) & 0xFFFF).

- The high-adjusted value, #ha(value), compensates for #lo() being treated as a signed number: #ha(x)=(((x >> 16) + ((x & 0x8000) ? 1 : 0)) & 0xFFFF).

- \_SDA\_BASE\_ is a symbol defined by the link editor whose value in shared objects is the same as \_GLOBAL\_OFFSET\_TABLE\_, and in executable programs is an address within the small data area. Similarly, \_SDA2\_BASE\_ is a symbol defined by the link editor whose value in executable programs is an address within the small data 2 area.

Note that the relocation types in *Table 8* apply only to VLE sections. Sections containing Book E instructions should use the PowerPC e500 Application Binary Interface.

Table 8. VLE relocation types

| Name            | Value | Field    | Calculation      |

|-----------------|-------|----------|------------------|

| R_PPC_VLE_REL8  | 216   | bdh8     | (S + A - P) >> 1 |

| R_PPC_VLE_REL15 | 217   | bdh15    | (S + A - P) >> 1 |

| R_PPC_VLE_REL24 | 218   | bdh24    | (S + A - P) >> 1 |

| R_PPC_VLE_LO16A | 219   | split16a | #lo(S + A)       |

Table 8. VLE relocation types (continued)

| Name                   | Value | Field            | Calculation                           |

|------------------------|-------|------------------|---------------------------------------|

| R_PPC_VLE_LO16D        | 220   | split16d         | #lo(S + A)                            |

| R_PPC_VLE_HI16A        | 221   | split16a         | #hi(S + A)                            |

| R_PPC_VLE_HI16D        | 222   | split16d         | #hi(S + A)                            |

| R_PPC_VLE_HA16A        | 223   | split16a         | #ha(S + A)                            |

| R_PPC_VLE_HA16D        | 224   | split16d         | #ha(S + A)                            |

| R_PPC_VLE_SDA21        | 225   | low21<br>split20 | Y II (X + A). See <i>Table 9</i> .    |

| R_PPC_VLE_SDA21_LO     | 226   | low21<br>split20 | Y    #lo(X + A). See <i>Table 9</i> . |

| R_PPC_VLE_SDAREL_LO16A | 227   | split16a         | #lo(X + A)                            |

| R_PPC_VLE_SDAREL_LO16D | 228   | split16d         | #lo(X + A)                            |

| R_PPC_VLE_SDAREL_HI16A | 229   | split16a         | #hi(X + A)                            |

| R_PPC_VLE_SDAREL_HI16D | 230   | split16d         | #hi(X + A)                            |

| R_PPC_VLE_SDAREL_HA16A | 231   | split16a         | #ha(X + A)                            |

| R_PPC_VLE_SDAREL_HA16D | 232   | split16d         | #ha(X + A)                            |

Relocation types with special semantics are described in *Table 9*.

Table 9. Relocation types with special semantics

| Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R_PPC_VLE_SDA21 <sup>(1)</sup>  | The linker computes a 21-bit value with the 5 msbs having the value 13 (for GPR13), 2 (for GPR2), or 0. If the symbol whose index is in r_info is contained in .sdata or .sbss, a linker supplies a value of 13; if the symbol is in .PPC.EMB.sdata2 or .PPC.EMB.sbss2, the linker supplies a value of 2; if the symbol is in .PPC.EMB.sdata0 or .PPC.EMB.sbss0, the linker supplies a value of 0; otherwise, the link fails.  The 16 lsbs of this 21-bit value are set to the address of the symbol plus the relocation entry r_addend value minus the appropriate base for the symbol section:  _SDA_BASE_ for a symbol in .sdata or .sbss  _SDA2_BASE_ for a symbol in .PPC.EMB.sdata2 or .PPC.EMB.sbss2  0 for a symbol in .PPC.EMB.sdata0 or .PPC.EMB.sbss0  If the 5 msbs of the computed 21-bit value are non-zero, the linker uses the low21 relocation field, where the 11 msbs remain unchanged and the computed 21-bit value occupies bits 11–31.  Otherwise, the 5 msbs of the computed 21-bit value are zero, with the following results:  The linker uses the split20 relocation field, where only bits occupying 6–10 remain unchanged  The 5 msbs of the 21-bit value are ignored  The next msb is copied to bit 11 and to bits 17–20 as a sign-extension  The next 4 msbs are copied to bits 12–15  The 11 remaining bits are copied to bits 21–31.  In the destination word, bits 0–5 are encoded with the binary value 011100, and bit 16 is encoded with the binary value 0.  Use of the split20 relocation field forces the encoding of the VLE e_li instruction, which may change the user's specified instruction. See Table 6. |

| R_PPC_VLE_SDA21_LO <sup>1</sup> | Like R_PPC_VLE_SDA21, except that the #lo() operator obtains the 16 lsbs of the 21-bit value. The #lo() operator is applied after the address of the symbol plus the relocation entry r_addend value is calculated, minus the appropriate base for the symbol's section: _SDA_BASE_ for a symbol in .sdata or .sbss, _SDA2_BASE_ for a symbol in .PPC.EMB.sdata2 or .PPC.EMB.sbss2, or 0 for a symbol in .PPC.EMB.sdata0 or .PPC.EMB.sbss0. The R_PPC_VLE_SDA21 entry describes applying the calculated 21-bit value to the destination word that uses either the low21 relocation field or the split20 relocation field. See <i>Table 6</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

<sup>1.</sup> Note that if the opcode is changed, 27 bits are changed instead of 21.

Note:

The relocations in Table 9 are not for load and store instructions (such as, e\_lwz and e\_stw), which should use the EABI relocation R\_PPC\_EMB\_SDA21. These relocations, as written here, only start with an e\_add16i. A linker might convert the instruction to an e\_li. Although other relocations do not specify the instructions they apply to, it may be useful to know that these relocations can apply only to one instruction.

Instruction set UM0438

#### 3 Instruction set

Note:

This section provides an overview of the VLE instruction set architecture. For details on each instruction, including assembly mnemonic and operands, refer to the VLE section of the EREF.

The VLE extension allows PowerPC Book E implementations to support more efficient binary representations of applications for the embedded processor spaces where code density plays a major role in affecting overall system cost, and to a somewhat lesser extent, performance. The intent of the VLE extension is not to define an entirely different ISA nor to supplant the existing PowerPC ISA. Instead, it can be viewed as a supplement that is applied conditionally to an application, or to part of an application, to improve code density.

The major objectives of the VLE extension are as follows:

- Maintain coexistence and consistency with the existing PowerPC Book E ISA and architecture

- Maintain a common programming model and instruction operation model in the VLE extension

- Reduce overall code size by 30 percent over existing PowerPC text segments

- Limit the increase in execution path length to under 10 percent for most important applications

- Limit the increase in hardware complexity for implementations containing the VLE extension

By meeting these objectives, cost-sensitive markets may significantly benefit from the use of the VLE extension.

The VLE extension uses the same semantics as traditional Book E. Due to the limited instruction encoding formats, VLE instructions typically support reduced immediate fields and displacements, and not all Book E operations are encoded in the VLE extension. The basic philosophy is to capture all useful operations, with most frequent operations given priority. Immediate fields and displacements are provided to cover most ranges encountered in embedded control code. Instructions are encoded in either a 16- or 32-bit format, and these formats can be freely intermixed.

Book E floating-point registers are not accessible to VLE instructions. Book E GPRs and SPRs are used by VLE instructions with the following limitations:

- VLE instructions using the 16-bit formats are limited to addressing GPR0–GPR7 and GPR24–GPR31 in most instructions. Move instructions are provided to transfer register contents between these registers and GPR8–GPR23.

- VLE instructions using the 16-bit formats are limited to addressing CR0.

- VLE instructions using the 32-bit formats are limited to addressing CR0-CR3.

VLE instruction encodings generally differ from Book E instructions, except that most Book E instructions falling within Book E primary opcode 31 are encoded identically in 32-bit VLE instructions. Also, they have identical semantics unless they affect or access a resource not supported by the VLE extension. Primary opcode 4 is available to support additional instructions using identical encodings for both Book E and VLE. Therefore, an implementation of VLE can include additional APUs, such as the cache line locking APU, vector or scalar single-precision floating-point APU, and SPE extension and use the exact encodings.

UM0438 Instruction set

The VLE extension does not currently fully encompass 64-bit operations, although the addition of such operations in a future version is envisioned. For future compatibility, and to avoid confusion with Book E, register bit numbering remains the same as in traditional Book E.

The description of each instruction is contained in the VLE section of the *EREF* and includes the mnemonic and a formatted list of operands. VLE instructions have either exact or similar semantics to Book E instructions. Where the semantics, side-effects, and binary encodings are identical, the Book E mnemonics and formats are used. Where the semantics are similar but the binary encodings differ, the Book E mnemonic is generally preceded with an 'e\_'. To distinguish similar instructions available in both 16- and 32-bit formats under VLE and standard Book E instructions, VLE instructions encoded with 16 bits have an 'se\_' prefix. VLE instructions encoded with 32 bits that have different binary encodings or semantics than the equivalent Book E instruction have an 'e\_' prefix. Some examples are the following:

```

stw RS,D(RA) // Standard Book E instruction e_stw RS,D(RA) // 32-bit VLE instruction se stw RZ,SD4(RX)// 16-bit VLE instruction

```

For detailed functional descriptions of each VLE instruction, along with the assembly mnemonic and operands, refer to the VLE section of the *EREF*.

## Appendix A Simplified mnemonics for VLE instructions

This appendix describes simplified mnemonics for easier coding of assembly language programs. Simplified mnemonics are defined for the most frequently used forms of branch conditional, compare, trap, rotate and shift, and certain other instructions defined by the VLE extension.

The simplified mnemonics for the VLE extension are similar to those defined for the PowerPC programming environment. The result is a consistent programming view when working with VLE instructions on PowerPC architectures. Section A.11: Comprehensive list of simplified mnemonics provides an alphabetical listing of VLE simplified mnemonics used by a variety of processors. Some assemblers may define additional simplified mnemonics not included here. The simplified mnemonics listed here should be supported by all compilers.

#### A.1 Overview

Simplified (or extended) mnemonics allow an assembly-language programmer to use more intuitive mnemonics and symbols than the instructions and syntax defined by the instruction set architecture. For example, to code the conditional call "branch to target if CR3 specifies a greater than condition, setting the LR" without simplified mnemonics, the programmer would write the branch conditional and link instruction **e\_bcl 1,13**, target. The simplified mnemonic, branch if greater than and link, **e\_bgtl cr3**, target, incorporates the conditions. Not only is it easier to remember the symbols than the numbers when programming, it is also easier to interpret simplified mnemonics when reading existing code.

Simplified mnemonics are not a formal part of the architecture, but rather a recommendation for assemblers that support the instruction set.

Simplified mnemonics for VLE instructions provide a consistent assembly-language interface with the PowerPC architecture. Many simplified mnemonics were originally defined in the PowerPC architecture documentation. Some assemblers created their own, and others have been added to support extensions to the instruction set (for example, AltiVec instructions and Book E auxiliary processing units (APUs)). Simplified mnemonics for new architecturally defined and new implementation-specific special-purpose registers (SPRs) are described here very generally.

## A.2 Subtract simplified mnemonics

This section describes simplified mnemonics for subtract instructions.

#### A.2.1 Subtract immediate

The effect of a subtract immediate instruction can be achieved by negating the immediate operand of the add immediate instructions, **e\_add16i**, **e\_add2i**, **e\_add2is**, and **e\_addi**. Simplified mnemonics include this negation, making the intent of the computation clearer. These are listed in *Table 10*.

| Simplified mnemonic                 | Standard mnemonic                      |

|-------------------------------------|----------------------------------------|

| e_sub16i rD,rA,value                | <b>e_add16i r</b> D, <b>r</b> A,-value |

| e_sub2i. rA,value                   | e_add2i. rA,-value                     |

| e_sub2is rA,value                   | <b>e_add2is r</b> A,–value             |

| <b>e_subi r</b> D, <b>r</b> A,value | e_addi rD,rA,-value                    |

| e_subic rD,rA,value                 | e_addic rD,rA,-value                   |

| e_subic. rD,rA,value                | e_addic. rD,rA,-value                  |

Table 10. Subtract immediate simplified mnemonics

#### A.2.2 Subtract

Subtract from instructions subtract the second operand (rA) from the third (rB). The simplified mnemonics in *Table 11* use the more common order in which the third operand is subtracted from the second.

Table 11. Subtract simplified mnemonics

| Simplified mnemonic | Standard mnemonic <sup>(1)</sup> |

|---------------------|----------------------------------|

| sub[o][.] rD,rA,rB  | subf[o][.] rD,rB,rA              |

| subc[o][.] rD,rA,rB | subfc[o][.] rD,rB,rA             |

rD,rB,rA is not the standard order for the operands. The order of rB and rA is reversed to show the

equivalent behavior of the simplified mnemonic.

## A.3 Rotate and shift simplified mnemonics

Rotate and shift instructions provide powerful, general ways to manipulate register contents, but they can be difficult to understand. Simplified mnemonics are provided for the following operations:

- Extract—Select a field of *n* bits starting at bit position *b* in the source register; left or right justify this field in the target register; clear all other bits of the target register.

- Insert—Select a left- or right-justified field of *n* bits in the source register; insert this field starting at bit position *b* of the target register; leave other bits of the target register unchanged.

- Rotate—Rotate the contents of a register right or left n bits without masking.

- Shift—Shift the contents of a register right or left *n* bits, clearing vacated bits (logical shift).

- Clear—Clear the leftmost or rightmost n bits of a register.

- Clear left and shift left—Clear the leftmost *b* bits of a register, then shift the register left by *n* bits. This operation can be used to scale a (known non-negative) array index by the width of an element.

#### A.3.1 Operations on words

The simplified mnemonics in *Table 12* do not support coding with a dot (.) suffix. In PowerPC instructions, a dot (.) suffix causes the Rc bit to be set in the underlying instruction. However, the following VLE instruction forms do not support this.

Table 12. Word rotate and shift simplified mnemonics

| Operation                                | Simplified mnemonic                                        | Equivalent to:                                                                             |

|------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Extract and left justify word immediate  | <b>e_extlwi</b> rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0) | e_rlwinm rA,rS, <i>b</i> , <b>0</b> , <i>n</i> – 1                                         |

| Extract and right justify word immediate | <b>e_extrwi</b> rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0) | e_rlwinm rA,rS,b + n,32 - n,31                                                             |

| Insert from left word immediate          | <b>e_inslwi</b> rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0) | e_rlwimi rA,rS,32 - <i>b,b</i> ,( <i>b</i> + <i>n</i> ) - 1                                |

| Insert from right word immediate         | <b>e_insrwi</b> rA,rS, <i>n</i> , <i>b</i> ( <i>n</i> > 0) | <b>e</b> _rlwimi rA,rS,32 - ( <i>b</i> + <i>n</i> ), <i>b</i> ,( <i>b</i> + <i>n</i> ) - 1 |

| Rotate left word immediate               | e_rotlwi rA,rS,n                                           | e_rlwinm rA,rS,n,0,31                                                                      |

| Rotate right word immediate              | e_rotrwi rA,rS,n                                           | e_rlwinm rA,rS,32 - n,0,31                                                                 |

| Shift left word immediate                | <b>e_slwi</b> rA,rS, <i>n</i> ( <i>n</i> < 32)             | e_rlwinm rA,rS,n,0,31 - n                                                                  |

| Shift right word immediate               | <b>e_srwi</b> rA,rS, <i>n</i> ( <i>n</i> < 32)             | e_rlwinm rA,rS,32 - n,n,31                                                                 |

| Clear left word immediate                | <b>e_clrlwi</b> rA,rS, <i>n</i> ( <i>n</i> < 32)           | e_rlwinm rA,rS,0,n,31                                                                      |

| Clear right word immediate               | <b>e_clrrwi</b> rA,rS,n (n < 32)                           | e_rlwinm rA,rS,0,0,31 - n                                                                  |

| Clear left and shift left word immediate | e_clrlslwi rA,rS, $b$ , $n$ ( $n \le b \le 31$ )           | <b>e_rlwinm</b> rA,rS, <i>n</i> , <i>b</i> – <i>n</i> ,31 – <i>n</i>                       |

Examples using word mnemonics follow:

1. Extract the sign bit (bit 0) of **r**S and place the result right-justified into **r**A.

e\_extrwi rA,rS,1,0

equivalent to

e rlwinm

rA,rS,1,31,31

2. Insert the bit extracted in (1) into the sign bit (bit 0) of rB.

e insrwi rB,rA,1,0

equivalent to

e\_rlwimi rB,rA,31,0,0

3. Shift the contents of rA left 8 bits.

e\_slwi rA,rA,8

equivalent to

e\_rlwinm rA,rA,8,0,23

4. Clear the high-order 16 bits of rS and place the result into rA.

e\_clrlwi rA,rS,16

equivalent to

e\_rlwinm

rA,rS,0,16,31

## A.4 Branch instruction simplified mnemonics

Branch conditional instructions can be coded with the operations and with a condition to be tested as part of the instruction mnemonic rather than as numeric operands (the BO32, BI32 and BO16, BI16 operands). *Table 13* shows the four general types of branch instructions. Simplified mnemonics are defined only for branch conditional instructions that include either the BO32, BI32 or BO16, BI16 operands; there is no need to simplify the other branch mnemonics.

| Instruction name         | Mnemonic                   | Syntax                                         |

|--------------------------|----------------------------|------------------------------------------------|

| Branch                   | e_b (e_bl)<br>se_b (se_bl) | target_addr<br>target_addr                     |

| Branch Conditional       | e_bc (e_bcl)<br>se_bc      | BO32,BI32,target_addr<br>BO16,BI16,target_addr |

| Branch to Link Register  | se_bir (se_biri)           | _                                              |

| Branch to Count Register | se_bctr (se_bctrl)         | _                                              |

Table 13. Branch instructions

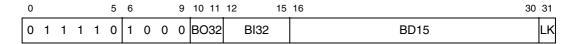

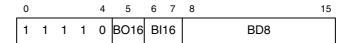

The BO32, BI32, and BO16, BI16 operands correspond to fields in the instruction opcode, as *Figure 1* shows for Branch Conditional (**e\_bc**, **e\_bcl**, and **se\_bc**) instructions.

Figure 1. Branch conditional (e\_bc, se\_bc) instruction formats e\_bc (e\_bcl)

se\_bc

Both the BO32 and BO16 operands allow testing whether a CR bit causes a branch to occur based on a true or false condition. The BO32 operand provides additional capability that allows branch operations that involve decrementing the CTR and testing for a zero or non-zero CTR value.

The BI32 and BI16 operands identify a CR bit to test (whether a comparison is less than or greater than, for example). The simplified mnemonics avoid the need to memorize the numerical values for BO32, BI32, and BO16, BI16 operands.

For example, **e\_bc 2,0,** target is a conditional branch that, as a BO32 value of 2 (0b10) indicates, decrements the CTR, then branches if the decremented CTR is not zero. The operation specified by BO32 is abbreviated as **d** (for decrement) and **nz** (for not zero), which replace the **c** in the original mnemonic; so the simplified mnemonic for **e\_bc** becomes **e\_bdnz**. The branch does not depend on a condition in the CR, so BI32 can be eliminated, reducing the expression to **e\_bdnz** target.

In addition to CTR operations, the BO32 operand provides branch decisions based on true or false conditions. For example, if a branch instruction depends on an equal condition in CR0, the expression is **e\_bc 1,2**, target. To specify a true condition, the BO32 value becomes 1; the CR0 equal field is indicated by a BI32 value of 2. Incorporating the branchif-true condition a 't' is used to replace the **c** in the original mnemonic, **e\_bt**. The BI32 value of 2 is replaced by the **eq** symbol. Using the simplified mnemonic and the **eq** operand, the expression becomes **e\_bt eq**, target.

This example tests CR0[EQ]; however, to test the equal condition in CR3 (CR bit 14), the expression becomes **e\_bc 1,14**, target. The BI32 operand of 14 indicates CR[14] (CR3[2], or

BI32 field 0b1110). This can be expressed as the simplified mnemonic, **e\_bt 4**  $\times$  **cr3 + eq**, *target*.

The notation,  $4 \times cr3 + eq$  may at first seem awkward, but it eliminates computing the value of the CR bit. It can be seen that  $(4 \times 3) + 2 = 14$ . Note that although 32-bit registers in Book E processors are numbered 32–63, only values 0–15 are valid (or possible) for Bl32 operands. A Book E–compliant processor automatically translates the Bl32 bit values; specifying a Bl32 value of 14 selects bit 46 on a Book E processor, or CR3[2] = CR3[EQ].

To reduce code size, VLE provides a 16-bit conditional branch instruction that uses the BO16 and BI16 operands. For example, the 32-bit conditional branch **e\_bc 1,2**, *target* can be expressed using a 16-bit instruction format, **se\_bc 1,2**, *target*. In simplified mnemonic form this becomes **se\_bt eq**, target. The BO16 operand only allows testing a true or false condition, unlike the BO32 operand that also allows decrementing the CTR. The BI16 operand allows testing of only CR0, unlike the BI32 operand, which allows testing CR0–CR3.

#### A.4.1 Key facts about simplified branch mnemonics

The following key points are helpful in understanding how to use simplified branch mnemonics:

- All simplified branch mnemonics eliminate the BO32 and BO16 operands, so if any operand is present in a branch simplified mnemonic, it is the BI32 or BI16 operand (or a reduced form of it).

- If the CR is not involved in the branch, the BI32 and BI16 operands can be deleted.

- If the CR is involved in the branch, the BI32 and BI16 operands can be treated in the following ways:

- It can be specified as a numeric value, just as it is in the architecturally defined instruction, or it can be indicated with an easier to remember formula, 4 \* crn + [test bit symbol], where n indicates the CR field number. For BI16 operands only CR0 is allowed, for BI32 CR0–CR3 is allowed.

- The condition of the test bit (eq, lt, gt, and so) can be incorporated into the mnemonic, leaving the need for an operand that defines only the CR field.

- If the test bit is in CR0, no operand is needed.

- If the test bit is in CR1–CR3, the Bl32 operand can be replaced with a **cr**S operand (that is, **cr1**, **cr2**, **or cr3**). The Bl16 operand cannot be used for test bits that are not in CR0.

#### A.4.2 Eliminating the BO32 and BO16 operands

The 2-bit BO32 field, shown in *Figure 1*, encodes the following operations in 32-bit conditional branch instructions:

- Decrement count register (CTR)

- And test if result is equal to zero

- And test if result is not equal to zero

- Test condition register (CR)

- Test condition true

- Test condition false

The 1-bit BO16 field, shown in *Figure 1*, encodes the following operations in 16-bit conditional branch instructions:

- Test condition register (CR)

- Test condition true

- Test condition false

As shown in *Table 14*, the '**c**' in the standard mnemonic is replaced with the operations otherwise specified in the BO32 or BO16 field, (**d** for decrement, **z** for zero, **nz** for non-zero, **t** for true, and **f** for false).

Table 14. BO32 and BO16 operand encodings

| BO32<br>Field     | BO16<br>Field | Value<br>(Decimal) | Description                                                     | Symbol             |

|-------------------|---------------|--------------------|-----------------------------------------------------------------|--------------------|

| 00                | 0             | 0                  | Branch if the condition is FALSE. <sup>(1)</sup>                | f                  |

| 01                | 1             | 1                  | Branch if the condition is TRUE. <sup>1</sup>                   | t                  |

| 10 <sup>(2)</sup> | _             | 2                  | Decrement the CTR, then branch if the decremented CTR $\neq$ 0. | dnz <sup>(3)</sup> |

| 11 <sup>2</sup>   | _             | 3                  | Decrement the CTR, then branch if the decremented CTR = 0.      | $dz^3$             |

- Instructions for which BO32 or BO16 are 0 (branch if condition true) or 1 (branch if condition false) do not depend on the CTR value and alternately can be coded by incorporating the condition specified by the BI32 or BI16 fields. See Section A.5.2: Simplified mnemonics that incorporate CR conditions (eliminates BO32 and BO16 and replaces BI32 with crS)

- 2. Simplified mnemonics for branch instructions that do not test CR bits (BO32 = 2 or 3) should specify only a target. Otherwise a programming error may occur.

- 3. Notice that these instructions do not use the branch in condition true or false operations, so simplified mnemonics for these should not specify a Bl32 operand.

#### A.4.3 The BI32 and BI16 operand—CR Bit and field representations

With standard branch mnemonics, the BI32 and BI16 operands are used to test a CR bit, as shown in the example in *Section A.4: Branch instruction simplified mnemonics*.

With simplified mnemonics, the BI32 and BI16 operands are handled differently depending on whether the simplified mnemonic incorporates a CR condition to test, as follows:

- Some branch simplified mnemonics incorporate only the BO32 or BO16 operand.

These simplified mnemonics can use the architecturally defined BI32 or BI16 operand to specify the CR bit, as follows:

- The BI32 or BI16 operands can be presented exactly as it is with standard mnemonics—as a decimal number, 0–15 for the BI32 operand, and 0–3 for the BI16 operand.

- Symbols can be used to replace the decimal operand, as shown in the example in Section A.4: Branch instruction simplified mnemonics where e\_bt 4 \* cr3 + eq,target could be used instead of e\_bt 14,target. This is described in Section: Specifying a CR Bit

The simplified mnemonics in *Section A.5: Simplified mnemonics that incorporate the BO32* and *BO16* operands use one of these two methods to specify a CR bit.

Additional simplified mnemonics incorporate CR conditions that would otherwise be specified by the BI32 or BI16 operand, so the BI32 or BI16 operand is replaced by the crS operand to specify the CR field. See Section A.4.4: BI32 and BI16 operand instruction encoding

These mnemonics are described in Section A.5.2: Simplified mnemonics that incorporate CR conditions (eliminates BO32 and BO16 and replaces BI32 with crS)

#### A.4.4 BI32 and BI16 operand instruction encoding

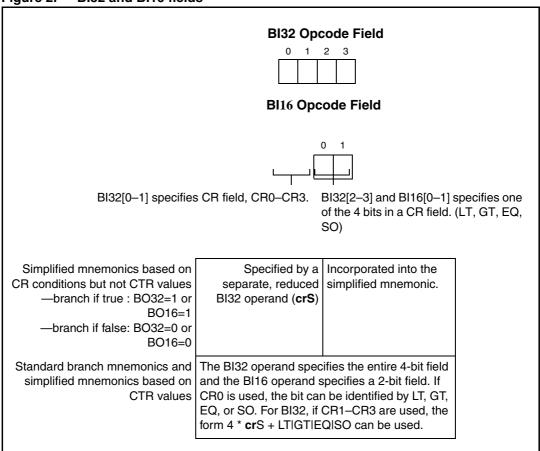

The entire 4-bit BI32 and 2-bit BI16 fields, shown in *Figure 2*, represent the bit number for the CR bit to be tested. For standard branch mnemonics and for branch simplified mnemonics that do not incorporate a CR condition, the BI32 operand provides all 4 bits and the BI16 operand provides all 2 bits.

For simplified branch mnemonics described in *Section A.5.2: Simplified mnemonics that incorporate CR conditions (eliminates BO32 and BO16 and replaces BI32 with crS)* the BI32 or BI16 operand is replaced by a **cr**S operand. To understand this, it is useful to view the BI32 operand as composed of two parts. As *Figure 2* shows, BI32[0–1] indicates the CR field and BI32[2–3] represents the condition to test. The 2-bit BI16 operand only has one part, BI16[0–1] represents the condition within CR0 to test.

Figure 2. BI32 and BI16 fields

Integer record-form instructions update CR0 and floating-point record-form instructions update CR1, as described in *Table 15*.

5//

#### Specifying a CR Bit

Note that the AIM version of the PowerPC architecture numbers CR bits 0–31 and Book E numbers them 32–63. However, no adjustment is necessary to the code; in Book E devices, 32 is automatically added to the BI32 and BI16 values, as shown in *Table 15* and *Table 16*.

Table 15. CR0 and CR1 fields as updated by integer and floating-point instructions

| CRn Bit  | CI  | CR Bits |         | BI32 |     | Description                                                             |  |

|----------|-----|---------|---------|------|-----|-------------------------------------------------------------------------|--|

| Chii bil | AIM | Book E  | 0–1 2–3 |      | 0–1 | Bescription                                                             |  |

| CR0[0]   | 0   | 32      | 00      | 00   | 00  | Negative (LT)—Set when the result is negative.                          |  |

| CR0[1]   | 1   | 33      | 00      | 01   | 01  | Positive (GT)—Set when the result is positive (and not zero).           |  |

| CR0[2]   | 2   | 34      | 00      | 10   | 10  | Zero (EQ)—Set when the result is zero.                                  |  |

| CR0[3]   | 3   | 35      | 00      | 11   | 11  | Summary overflow (SO). Copy of XER[SO] at the instruction's completion. |  |

| CR1[0]   | 4   | 36      | 01      | 00   | _   | Copy of FPSCR[FX] at the instruction's completion.                      |  |

| CR1[1]   | 5   | 37      | 01      | 01   | _   | Copy of FPSCR[FEX] at the instruction's completion.                     |  |

| CR1[2]   | 6   | 38      | 01      | 10   | _   | Copy of FPSCR[VX] at the instruction's completion.                      |  |

| CR1[3]   | 7   | 39      | 01      | 11   | _   | Copy of FPSCR[OX] at the instruction's completion.                      |  |