# How to use STSW-AKIDRV and an STM32 to control the ADC120/ADC1283 through SPI

#### Introduction

This user manual provides information on using the STSW-AKIDRV software.

The ADC120 and ADC1283 are both 8 channel 12-bit ADCs. The demo boards for both devices are STEVAL-AKI001V1 and STEVAL-AKI002V1, respectively.

The STM32 family of 32-bit microcontrollers developed by STMicroelectronics are based on the Arm Cortex-M processor architecture and are widely used in a variety of applications.

Serial peripheral interface (SPI) is a synchronous serial communication protocol.

## 1 SPI configuration of your microcontroller

#### 1.1 Pinout

As the ADC120 and ADC1283 are full duplex peripherals, the STM32 MCU must be used in full duplex controller mode to communicate with them.

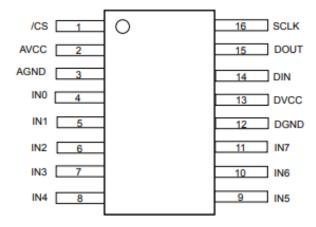

Figure 1. ADC120/ADC1283 pinout

Figure 1. Pin description (top view)

The following table matches the STEVAL-AKI001V1 SPI pinout with the Nucleo STM32L476RG pinout.

Table 1. SPI pinout

| Pin for SPI | STM32L476RG pinout to connect the STEVAL-AKI001V1 |

|-------------|---------------------------------------------------|

| SCLK        | PB13                                              |

| MOSI        | PB15                                              |

| MISO        | PB14                                              |

| CSI         | PB12                                              |

#### 1.2 SPI speed

The frequency used by the microcontroller must match the different possible frequencies of the ADC120 and ADC1283.

Table 2. SPI communication speeds according to the device

|         | Minimum frequency | Maximum frequency |

|---------|-------------------|-------------------|

| ADC120  | 800 kHz (50ksps)  | 16 MHz (1Msps)    |

| ADC1283 | 800 kHz (50ksks)  | 3.2 MHz (200ksps) |

UM3329 - Rev 1 page 2/11

#### 1.3 Adress and ship select management

Both ADCs have 8 multiplexed inputs. These inputs can be selected thanks to several addresses.

Table 3. Match between address and channel to read

| Input | Hexadecimal address |

|-------|---------------------|

| IN0   | 0x00                |

| IN1   | 0x08                |

| IN2   | 0x10                |

| IN3   | 0x18                |

| IN4   | 0x20                |

| IN5   | 0x28                |

| IN6   | 0x30                |

| IN7   | 0x38                |

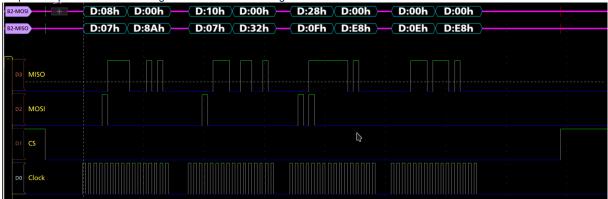

Regardless of the first input requested to read, the ADC120 and ADC1283 start by reading the channel 0. The following figure provides an example showing several consecutive readings. During and between all readings, chip select must remain low.

Figure 2. Example of reading several channels

Chip select pin remains low during and between the readings

The following table shows that the first MISO payload is the channel INO digital conversion.

Table 4. Explanation of reading steps, there is a shift between the ask of reading and the reading.

| Data on the bus | MOSI | 08 00         | 10 00         | 28 00         | 00 00         |

|-----------------|------|---------------|---------------|---------------|---------------|

| Data on the bus | MISO | 07 8A         | 07 32         | 0F E8         | 0E E8         |

| Explanations    | MOSI | Ask for IN1   | Ask for IN2   | ASK for IN5   |               |

| Схріанаціонз    | MISO | Result of IN0 | Result of IN1 | Result of IN2 | Result of IN5 |

Note: The chip select pin remains low during all the readings. If the chip select pin returns to high between two readings, the next value read will be the channel INO digital conversion.

UM3329 - Rev 1 page 3/11

#### 2 Use of the software

The STSW-AKIDRV software gives an example to use with the NUCLEO-L476RG.

#### 2.1 Configuration of the SPI

The SPI configuration is performed through the MX SPI2 Init function.

Figure 3. SPI initialisation function

```

static void MX SPI2 Init(void)

1

/* USER CODE BEGIN SPI2 Init 0 */

/* USER CODE END SPI2 Init 0 */

/* USER CODE BEGIN SPI2 Init 1 */

/* USER CODE END SPI2 Init 1 */

/* SPI2 parameter configuration*/

hspi2.Instance = SPI2;

hspi2.Init.Mode = SPI_MODE_MASTER;

hspi2.Init.Direction = SPI DIRECTION 2LINES;

hspi2.Init.DataSize = SPI DATASIZE 8BIT;

hspi2.Init.CLKPolarity = SPI POLARITY LOW;

hspi2.Init.CLKPhase = SPI PHASE 1EDGE;

hspi2.Init.NSS = SPI NSS SOFT;

hspi2.Init.BaudRatePrescaler = SPI BAUDRATEPRESCALER 32;

hspi2.Init.FirstBit = SPI FIRSTBIT MSB;

hspi2.Init.TIMode = SPI TIMODE DISABLE;

hspi2.Init.CRCCalculation = SPI_CRCCALCULATION_DISABLE;

hspi2.Init.CRCPolynomial = 7;

hspi2.Init.CRCLength = SPI CRC LENGTH DATASIZE;

hspi2.Init.NSSPMode = SPI NSS PULSE DISABLE;

if (HAL SPI Init(&hspi2) != HAL_OK)

Error Handler();

/* USER CODE BEGIN SPI2 Init 2 */

/* USER CODE END SPI2 Init 2 */

}

```

The following table summarizes the values set to communicate with the ADC120/ADC1283.

Table 5. SPI initialisation values

| Variable             | Value                | Explanation                                                          |

|----------------------|----------------------|----------------------------------------------------------------------|

| hspi2.Instance       | SPI2                 | Defines the instance of the SPI interface to use (SPI2).             |

| hspi2.Init.Mode      | SPI_MODE_MASTER      | Defines the operating mode of the SPI interface as master mode.      |

| hspi2.Init.Direction | SPI_DIRECTION_2LINES | Defines the data transfer direction using two lines (MOSI and MISO). |

| hspi2.Init.DataSize  | SPI_DATASIZE_8BIT    | Defines the size of the data to be transferred in 8 bits.            |

UM3329 - Rev 1 page 4/11

| Variable                     | Value                      | Explanation                                                                      |

|------------------------------|----------------------------|----------------------------------------------------------------------------------|

| hspi2.Init.CLKPolarity       | SPI_POLARITY_LOW           | Defines the polarity level of the SPI clock as low.                              |

| hspi2.Init.CLKPhase          | SPI_PHASE_1EDGE            | Defines the phase of the SPI clock at the first transition.                      |

| hspi2.Init.NSS               | SPI_NSS_SOFT               | NSS (negative chip select) will be handled externally by a GPIO.                 |

| hspi2.Init.BaudRatePrescaler | SPI_BAUDRATEPRESCALER_32   | Defines the prescaler of the SPI clock frequency as 32.                          |

| hspi2.Init.FirstBit          | SPI_FIRSTBIT_MSB           | Defines the data bit to be transferred first (MSB).                              |

| hspi2.Init.TIMode            | SPI_TIMODE_DISABLE         | Disables the TI (Transmit-Only) mode of the SPI interface.                       |

| hspi2.Init.CRCCalculation    | SPI_CRCCALCULATION_DISABLE | Disables the CRC (Cyclic Redundancy Check) calculation for the transferred data. |

| hspi2.Init.CRCPolynomial     | 7                          | Defines the polynomial used for the CRC calculation.                             |

| hspi2.Init.CRCLength         | SPI_CRC_LENGTH_DATASIZE    | Defines the length of the CRC to the size of the transferred data.               |

| hspi2.Init.NSSPMode          | SPI_NSS_PULSE_DISABLE      | Disables the pulse mode of the NSS line.                                         |

#### 2.1.1 SPI speed according to the device

STSW-AKIDRV comes with a preset code for SPI communication.

In this example, the SPI speed can be modified in the MX SPI2 Init (void) function.

In this function, one of the SPI init attributes is hspi2. Init.BaudRatePrescaler.

In the example, hspi2.Init.BaudRatePrescaler = SPI BAUDRATEPRESCALER 32.

The following table provides the associated frequencies.

Table 6. Prescaler and the associated frequencies for a clock system (SYSCLK) of 80 MHz

| Prescaler | Frequency (MHz) |

|-----------|-----------------|

| 2         | 40 MHz          |

| 4         | 20 MHz          |

| 8         | 10 MHz          |

| 16        | 5 MHz           |

| 32        | 2.5 MHz         |

| 64        | 1.25 MHz        |

| 128       | 0.625 MHz       |

| 256       | 0.3125 MHz      |

#### 2.2 Function to read the channels

Communication with ADC120 and ADC1283 is relatively straightforward. The simple function read ADC120 128 () allows reading one or several channels.

The STSW-AKIDRV comes with stm32 HAL (hardware abstraction layer) libraries to control the SPI communication and GPIOs.

Figure 4. read\_ADC120\_128() function example

```

void read_ADC120_128(uint8_t* channels_to_read, uint8_t* collected_data)

{

size=sizeof(channels_to_read)*2; //number of byte to send

HAL_GPIO_WritePin(GPIOB, GPIO_PIN_12, GPIO_PIN_RESET); //Chip select set to low

HAL_SPI_TransmitReceive(&hspi2, channels_to_read, collected_data, size, SPI_TIMEOUT); //transmission of the data

HAL_GPIO_WritePin(GPIOB, GPIO_PIN_12, GPIO_PIN_SET); //Chip select set to high.

// note: If the chip select go back back to high between readings, the next value read by the ADC will be channel 0

}

```

UM3329 - Rev 1 page 5/11

This function takes in two parameters:

- channels\_to\_read, which is a pointer to an array of uint8\_t data type that specifies the channels to read from the ADC.

- collected\_data, which is a pointer to an array of uint8\_t data type that stores the collected data.

The function first calculates the number of bytes to send based on the size of the <code>channels\_to\_read</code> array and sets the chip select pin to low to activate the ADC.

It then uses the SPI protocol to transmit and receive data to and from the ADC.

Once the data are collected, the chip select pin is released to high again using  ${\tt HAL\_GPIO\_WritePin}$  function.

UM3329 - Rev 1 page 6/11

## **Revision history**

Table 7. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 20-Jun-2024 | 1       | Initial release. |

UM3329 - Rev 1 page 7/11

## **Contents**

| 1                     | SPI    | configuration of your microcontroller   | .2  |

|-----------------------|--------|-----------------------------------------|-----|

|                       | 1.1    | Pinout                                  | . 2 |

|                       | 1.2    | SPI speed                               | . 2 |

|                       | 1.3    | Adress and ship select management       | . 3 |

| 2 Use of the software |        | of the software                         | .4  |

|                       | 2.1    | Configuration of the SPI                | . 4 |

|                       |        | 2.1.1 SPI speed according to the device | . 5 |

|                       | 2.2    | Function to read the channels           | . 5 |

| Rev                   | vision | history                                 | .7  |

## **List of figures**

| Figure 1. | ADC120/ADC1283 pinout               | Ž |

|-----------|-------------------------------------|---|

| Figure 2. | Example of reading several channels | 3 |

| Figure 3. | SPI initialisation function         | 4 |

| Figure 4. | read_ADC120_128() function example  | Ĉ |

UM3329 - Rev 1 page 9/11

## **List of tables**

| Table 1. | SPI pinout                                                                                | 2 |

|----------|-------------------------------------------------------------------------------------------|---|

| Table 2. | SPI communication speeds according to the device                                          | 2 |

| Table 3. | Match between address and channel to read                                                 |   |

| Table 4. | Explanation of reading steps, there is a shift between the ask of reading and the reading | 3 |

| Table 5. | SPI initialisation values                                                                 | 4 |

| Table 6. | Prescaler and the associated frequencies for a clock system (SYSCLK) of 80 MHz            | 5 |

| Table 7. | Document revision history                                                                 | 7 |

|          |                                                                                           |   |

UM3329 - Rev 1 page 10/11

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

UM3329 - Rev 1 page 11/11