Application note

## ISM330IS: always-on 3-axis accelerometer and 3-axis gyroscope with ISPU intelligent sensor processing unit

## Introduction

This document provides usage information and application hints related to ST's ISM330IS iNEMO inertial module with intelligent sensor processing unit (ISPU).

The ISM330IS is a 3-axis digital accelerometer and 3-axis digital gyroscope system-in-package with a digital I<sup>2</sup>C/SPI serial interface standard output, performing at 0.59 mA in combo high-performance mode (gyroscope + accelerometer only, ISPU not included). Thanks to the ultralow noise performance of both the gyroscope and the accelerometer, the device combines always-on low-power features with superior sensing precision for an optimal motion experience for the consumer.

The device has a dynamic user-selectable full-scale acceleration range of  $\pm 2/\pm 4/\pm 8/\pm 16$  g and an angular rate range of  $\pm 125/\pm 250/\pm 500/\pm 1000/\pm 2000$  dps.

The availability of a dedicated connection mode with up to 4 external sensors allows the implementation of the sensor hub functionality.

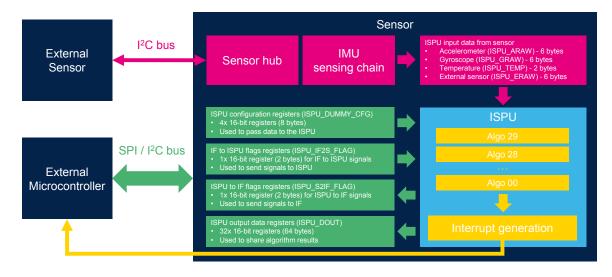

The ISM330IS embeds a new ST category of processing, ISPU - intelligent sensor processing unit, to support real-time applications that rely on sensor data. The ISPU is an ultralow-power, high-performance programmable core based on the STRED architecture, a proprietary architecture developed by STMicroelectronics. The ISPU toolchain allows developing in C code and loading any custom program in the core, ranging from signal processing algorithms to machine learning and deep learning models.

The ISM330IS is available in a small plastic land grid array package (LGA-14L) and it is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.

The ultrasmall size and weight of the SMD package make it an ideal choice for industrial applications such as robotics, anomaly detection, and asset tracking.

# 1 Pin description

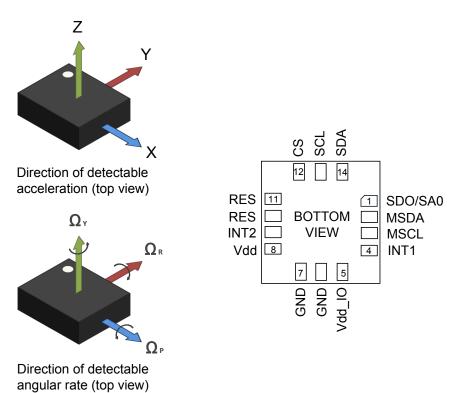

57

Figure 1. Pin connections

#### Table 1. Internal pin status

| Pin # | Name   | Mode 1 function                                                                                                        | Mode 2 function                                                                                                        | Pin status - mode 1                                                                                                                   | Pin status - mode 2                                                                                                                   |

|-------|--------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|       | SDO    | SPI 4-wire interface serial                                                                                            | SPI 4-wire interface serial                                                                                            | Default: input without pull-up                                                                                                        | Default: input without pull-up                                                                                                        |

| 1     |        | data output (SDO)                                                                                                      | data output (SDO)                                                                                                      | Pull-up is enabled if bit                                                                                                             | Pull-up is enabled if bit                                                                                                             |

|       | SA0    | I <sup>2</sup> C least significant bit of the device address (SA0)                                                     | I <sup>2</sup> C least significant bit of the device address (SA0)                                                     | SDO_PU_EN = 1 in PIN_CTRL<br>(02h).                                                                                                   | SDO_PU_EN = 1 in PIN_CTRL<br>(02h).                                                                                                   |

|       |        |                                                                                                                        |                                                                                                                        | Default: input without pull-up                                                                                                        | Default: input without pull-up                                                                                                        |

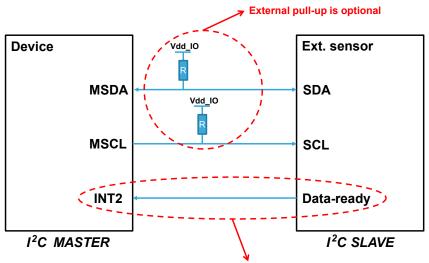

| 2     | MSDA   | Connect to Vdd_IO or<br>GND                                                                                            | I²C serial data master<br>(MSDA)                                                                                       | Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in<br>MASTER_CONFIG (14h) in the<br>sensor hub registers (see Note<br>to enable pull-up). | Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in<br>MASTER_CONFIG (14h) in the<br>sensor hub registers (see Note<br>to enable pull-up). |

|       |        |                                                                                                                        |                                                                                                                        | Default: input without pull-up                                                                                                        | Default: input without pull-up                                                                                                        |

| 3     | MSCL   | Connect to Vdd_IO or<br>GND                                                                                            | I <sup>2</sup> C serial clock master<br>(MSCL)                                                                         | Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in<br>MASTER_CONFIG (14h) in the<br>sensor hub registers (see Note<br>to enable pull-up). | Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in<br>MASTER_CONFIG (14h) in the<br>sensor hub registers (see Note<br>to enable pull-up). |

| 4     | INT1   | Programmable interrupt 1                                                                                               | Programmable interrupt 1                                                                                               | Default: input with pull-down <sup>(1)</sup>                                                                                          | Default: input with pull-down <sup>(1)</sup>                                                                                          |

| 5     | Vdd_IO | Power supply for I/O pins                                                                                              | Power supply for I/O pins                                                                                              |                                                                                                                                       |                                                                                                                                       |

| 6     | GND    | 0 V supply                                                                                                             | 0 V supply                                                                                                             |                                                                                                                                       |                                                                                                                                       |

| 7     | GND    | 0 V supply                                                                                                             | 0 V supply                                                                                                             |                                                                                                                                       |                                                                                                                                       |

| 8     | Vdd    | Power supply                                                                                                           | Power supply                                                                                                           |                                                                                                                                       |                                                                                                                                       |

| 9     | INT2   | Programmable interrupt 2<br>(INT2)                                                                                     | Programmable interrupt<br>2 (INT2) / I <sup>2</sup> C master<br>external synchronization<br>signal (MDRDY)             | Default: output forced to ground                                                                                                      | Default: output forced to ground                                                                                                      |

| 10    | RES    | Leave unconnected                                                                                                      | Leave unconnected                                                                                                      |                                                                                                                                       |                                                                                                                                       |

| 11    | RES    | Connect to Vdd_IO or<br>leave unconnected                                                                              | Connect to Vdd_IO or leave unconnected                                                                                 |                                                                                                                                       |                                                                                                                                       |

|       |        | I <sup>2</sup> C / SPI mode selection                                                                                  | I <sup>2</sup> C / SPI mode selection                                                                                  |                                                                                                                                       |                                                                                                                                       |

| 12    | CS     | (1: SPI idle mode / I <sup>2</sup> C communication enabled;                                                            | (1: SPI idle mode / I <sup>2</sup> C communication enabled;                                                            | Default: input with pull-up                                                                                                           | Default: input with pull-up                                                                                                           |

|       |        | 0: SPI communication<br>mode / I <sup>2</sup> C disabled)                                                              | 0: SPI communication<br>mode / I <sup>2</sup> C disabled)                                                              |                                                                                                                                       |                                                                                                                                       |

| 13    | SCL    | I <sup>2</sup> C serial clock (SCL) /<br>SPI serial port clock (SPC)                                                   | I <sup>2</sup> C serial clock (SCL) / SPI<br>serial port clock (SPC)                                                   | Default: input without pull-up                                                                                                        | Default: input without pull-up                                                                                                        |

| 14    | SDA    | I <sup>2</sup> C serial data (SDA) / SPI<br>serial data input (SDI) / 3-<br>wire interface serial data<br>output (SDO) | I <sup>2</sup> C serial data (SDA) / SPI<br>serial data input (SDI) / 3-<br>wire interface serial data<br>output (SDO) | Default: input without pull-up                                                                                                        | Default: input without pull-up                                                                                                        |

1. INT1 must be set to 0 or left unconnected during power-on.

Internal pull-up value is from 30 k $\Omega$  to 50 k $\Omega$ , depending on Vdd\_IO. *The procedure to enable the pull-up on pins 2 and 3 is as follows:*

Note:

1. From the primary I<sup>2</sup>C/SPI interface: write 40h in register at address 01h (enable access to the sensor hub registers)

From the primary I<sup>2</sup>C/SPI interface: write 08h in register at address 14h (enable the pull-up on pins 2 and 3)

From the primary I<sup>2</sup>C/SPI interface: write 00h in register at address 01h (disable access to the sensor hub registers)

Table 2. Registers

| Register name             | Address | Bit7                   | Bit6                | Bit5         | Bit4        | Bit3       | Bit2           | Bit1              | Bit0         |

|---------------------------|---------|------------------------|---------------------|--------------|-------------|------------|----------------|-------------------|--------------|

| FUNC_CFG_ACCESS           | 01h     | ISPU_REG<br>_ACCESS    | SHUB_REG<br>_ACCESS | 0            | 0           | 0          | 0              | SW_RESET<br>_ISPU | 0            |

| PIN_CTRL                  | 02h     | 0                      | SDO_PU_EN           | 1            | 1           | 1          | 1              | 1                 | 1            |

| DRDY_PULSED_REG           | 0Bh     | DRDY_PULSED            | 0                   | 0            | 0           | 0          | 0              | 0                 | 0            |

| INT1_CTRL                 | 0Dh     | 0                      | 0                   | 0            | 0           | 0          | INT1_BOOT      | INT1_DRDY_G       | INT1_DRDY_XL |

| INT2_CTRL                 | 0Eh     | INT2_SLEEP<br>_ISPU    | 0                   | 0            | 0           | 0          | INT2_DRDY_TEMP | INT2_DRDY_G       | INT2_DRDY_XL |

| WHO_AM_I                  | 0Fh     | 0                      | 0                   | 1            | 0           | 0          | 0              | 1                 | 0            |

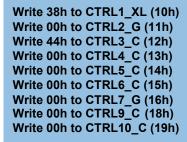

| CTRL1_XL                  | 10h     | ODR_XL3                | ODR_XL2             | ODR_XL1      | ODR_XL0     | FS1_XL     | FS0_XL         | 0                 | 0            |

| CTRL2_G                   | 11h     | ODR_G3                 | ODR_G2              | ODR_G1       | ODR_G0      | FS1_G      | FS0_G          | FS_125            | 0            |

| CTRL3_C                   | 12h     | BOOT                   | BDU                 | H_LACTIVE    | PP_OD       | SIM        | IF_INC         | 0                 | SW_RESET     |

| CTRL4_C                   | 13h     | 0                      | SLEEP_G             | INT2_on_INT1 | 0           | 0          | I2C_disable    | 0                 | 0            |

| CTRL5_C                   | 14h     | 0                      | 0                   | 0            | 0           | ST1_G      | ST0_G          | ST1_XL            | ST0_XL       |

| CTRL6_C                   | 15h     | 0                      | 0                   | 0            | XL_HM_MODE  | 0          | 0              | 0                 | 0            |

| CTRL7_G                   | 16h     | G_HM_MODE              | 0                   | 0            | 0           | 0          | 0              | 0                 | 0            |

| CTRL9_C                   | 18h     | ISPU_RATE_3            | ISPU_RATE_2         | ISPU_RATE_1  | ISPU_RATE_0 | 0          | 0              | ISPU_BDU_1        | ISPU_BDU_0   |

| CTRL10_C                  | 19h     | 0                      | 0                   | TIMESTAMP_EN | 0           | 0          | ISPU_CLK_SEL   | 0                 | 0            |

| ISPU_INT_STATUS0_MAINPAGE | 1Ah     | IA_ISPU_7              | IA_ISPU_6           | IA_ISPU_5    | IA_ISPU_4   | IA_ISPU_3  | IA_ISPU_2      | IA_ISPU_1         | IA_ISPU_0    |

| ISPU_INT_STATUS1_MAINPAGE | 1Bh     | IA_ISPU_15             | IA_ISPU_14          | IA_ISPU_13   | IA_ISPU_12  | IA_ISPU_11 | IA_ISPU_10     | IA_ISPU_9         | IA_ISPU_8    |

| ISPU_INT_STATUS2_MAINPAGE | 1Ch     | IA_ISPU_23             | IA_ISPU_22          | IA_ISPU_21   | IA_ISPU_20  | IA_ISPU_19 | IA_ISPU_18     | IA_ISPU_17        | IA_ISPU_16   |

| ISPU_INT_STATUS3_MAINPAGE | 1Dh     | 0                      | 0                   | IA_ISPU_29   | IA_ISPU_28  | IA_ISPU_27 | IA_ISPU_26     | IA_ISPU_25        | IA_ISPU_24   |

| STATUS_REG                | 1Eh     | TIMESTAMP_<br>ENDCOUNT | 0                   | 0            | 0           | 0          | TDA            | GDA               | XLDA         |

| OUT_TEMP_L                | 20h     | Temp7                  | Temp6               | Temp5        | Temp4       | Temp3      | Temp2          | Temp1             | Temp0        |

| OUT_TEMP_H                | 21h     | Temp15                 | Temp14              | Temp13       | Temp12      | Temp11     | Temp10         | Temp9             | Temp8        |

| OUTX_L_G                  | 22h     | D7                     | D6                  | D5           | D4          | D3         | D2             | D1                | D0           |

| OUTX_H_G                  | 23h     | D15                    | D14                 | D13          | D12         | D11        | D10            | D9                | D8           |

| OUTY_L_G                  | 24h     | D7                     | D6                  | D5           | D4          | D3         | D2             | D1                | D0           |

| OUTY_H_G                  | 25h     | D15                    | D14                 | D13          | D12         | D11        | D10            | D9                | D8           |

| OUTZ_L_G                  | 26h     | D7                     | D6                  | D5           | D4          | D3         | D2             | D1                | D0           |

| OUTZ_H_G                  | 27h     | D15                    | D14                 | D13          | D12         | D11        | D10            | D9                | D8           |

| OUTX_L_A                  | 28h     | D7                     | D6                  | D5           | D4          | D3         | D2             | D1                | D0           |

| OUTX_H_A                  | 29h     | D15                    | D14                 | D13          | D12         | D11        | D10            | D9                | D8           |

page 4/65

2

| Register name           | Address | Bit7                    | Bit6                    | Bit5                    | Bit4                    | Bit3                    | Bit2                    | Bit1                   | Bit0                   |

|-------------------------|---------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|

| OUTY_L_A                | 2Ah     | D7                      | D6                      | D5                      | D4                      | D3                      | D2                      | D1                     | D0                     |

| OUTY_H_A                | 2Bh     | D15                     | D14                     | D13                     | D12                     | D11                     | D10                     | D9                     | D8                     |

| OUTZ_L_A                | 2Ch     | D7                      | D6                      | D5                      | D4                      | D3                      | D2                      | D1                     | D0                     |

| OUTZ_H_A                | 2Dh     | D15                     | D14                     | D13                     | D12                     | D11                     | D10                     | D9                     | D8                     |

| STATUS_MASTER_ MAINPAGE | 39h     | WR_ONCE_DONE            | SLAVE3_NACK             | SLAVE2_NACK             | SLAVE1_NACK             | SLAVE0_NACK             | 0                       | 0                      | SENS_HUB<br>_ENDOP     |

| TIMESTAMP0              | 40h     | D7                      | D6                      | D5                      | D4                      | D3                      | D2                      | D1                     | D0                     |

| TIMESTAMP1              | 41h     | D15                     | D14                     | D13                     | D12                     | D11                     | D10                     | D9                     | D8                     |

| TIMESTAMP2              | 42h     | D23                     | D22                     | D21                     | D20                     | D19                     | D18                     | D17                    | D16                    |

| TIMESTAMP3              | 43h     | D31                     | D30                     | D29                     | D28                     | D27                     | D26                     | D25                    | D24                    |

| MD1_CFG                 | 5Eh     | 0                       | 0                       | 0                       | 0                       | 0                       | 0                       | INT1_ISPU              | INT1_SHUB              |

| MD2_CFG                 | 5Fh     | 0                       | 0                       | 0                       | 0                       | 0                       | 0                       | INT2_ISPU              | INT2_TIMESTAMP         |

| INTERNAL_FREQ_FINE      | 63h     | FREQ_FINE7              | FREQ_FINE6              | FREQ_FINE5              | FREQ_FINE4              | FREQ_FINE3              | FREQ_FINE2              | FREQ_FINE1             | FREQ_FINE0             |

| ISPU_DUMMY_CFG_1_L      | 73h     | ISPU_DUMMY<br>_CFG_1_7  | ISPU_DUMMY<br>_CFG_1_6  | ISPU_DUMMY<br>_CFG_1_5  | ISPU_DUMMY<br>_CFG_1_4  | ISPU_DUMMY<br>_CFG_1_3  | ISPU_DUMMY<br>_CFG_1_2  | ISPU_DUMMY<br>_CFG_1_1 | ISPU_DUMMY<br>_CFG_1_0 |

| ISPU_DUMMY_CFG_1_H      | 74h     | ISPU_DUMMY<br>_CFG_1_15 | ISPU_DUMMY<br>_CFG_1_14 | ISPU_DUMMY<br>_CFG_1_13 | ISPU_DUMMY<br>_CFG_1_12 | ISPU_DUMMY<br>_CFG_1_11 | ISPU_DUMMY<br>_CFG_1_10 | ISPU_DUMMY<br>_CFG_1_9 | ISPU_DUMMY<br>_CFG_1_8 |

| ISPU_DUMMY_CFG_2_L      | 75h     | ISPU_DUMMY<br>_CFG_2_7  | ISPU_DUMMY<br>_CFG_2_6  | ISPU_DUMMY<br>_CFG_2_5  | ISPU_DUMMY<br>_CFG_2_4  | ISPU_DUMMY<br>_CFG_2_3  | ISPU_DUMMY<br>_CFG_2_2  | ISPU_DUMMY<br>_CFG_2_1 | ISPU_DUMMY<br>_CFG_2_0 |

| ISPU_DUMMY_CFG_2_H      | 76h     | ISPU_DUMMY<br>_CFG_2_15 | ISPU_DUMMY<br>_CFG_2_14 | ISPU_DUMMY<br>_CFG_2_13 | ISPU_DUMMY<br>_CFG_2_12 | ISPU_DUMMY<br>_CFG_2_11 | ISPU_DUMMY<br>_CFG_2_10 | ISPU_DUMMY<br>_CFG_2_9 | ISPU_DUMMY<br>_CFG_2_8 |

| ISPU_DUMMY_CFG_3_L      | 77h     | ISPU_DUMMY<br>_CFG_3_7  | ISPU_DUMMY<br>_CFG_3_6  | ISPU_DUMMY<br>_CFG_3_5  | ISPU_DUMMY<br>_CFG_3_4  | ISPU_DUMMY<br>_CFG_3_3  | ISPU_DUMMY<br>_CFG_3_2  | ISPU_DUMMY<br>_CFG_3_1 | ISPU_DUMMY<br>_CFG_3_0 |

| ISPU_DUMMY_CFG_3_H      | 78h     | ISPU_DUMMY<br>_CFG_3_15 | ISPU_DUMMY<br>_CFG_3_14 | ISPU_DUMMY<br>_CFG_3_13 | ISPU_DUMMY<br>_CFG_3_12 | ISPU_DUMMY<br>_CFG_3_11 | ISPU_DUMMY<br>_CFG_3_10 | ISPU_DUMMY<br>_CFG_3_9 | ISPU_DUMMY<br>_CFG_3_8 |

| ISPU_DUMMY_CFG_4_L      | 79h     | ISPU_DUMMY<br>_CFG_4_7  | ISPU_DUMMY<br>_CFG_4_6  | ISPU_DUMMY<br>_CFG_4_5  | ISPU_DUMMY<br>_CFG_4_4  | ISPU_DUMMY<br>_CFG_4_3  | ISPU_DUMMY<br>_CFG_4_2  | ISPU_DUMMY<br>_CFG_4_1 | ISPU_DUMMY<br>_CFG_4_0 |

| ISPU_DUMMY_CFG_4_H      | 7Ah     | ISPU_DUMMY<br>_CFG_4_15 | ISPU_DUMMY<br>_CFG_4_14 | ISPU_DUMMY<br>_CFG_4_13 | ISPU_DUMMY<br>_CFG_4_12 | ISPU_DUMMY<br>_CFG_4_11 | ISPU_DUMMY<br>_CFG_4_10 | ISPU_DUMMY<br>_CFG_4_9 | ISPU_DUMMY<br>_CFG_4_8 |

5

## ISPU interaction registers

The list of the registers for the ISPU functions available in the device is given in Table 3. ISPU interaction registers and Table 4. ISPU to external resources. The ISPU interaction registers are accessible over the I<sup>2</sup>C/SPI interface when the ISPU\_REG\_ACCESS bit is set to 1 in the FUNC\_CFG\_ACCESS (01h) register. These registers are also accessible from ISPU through the address indicated in the third column (ISPU address), regardless of the configuration of the ISPU\_REG\_ACCESS bit.

| Register name    | Address | ISPU<br>address | Bit7        | Bit6        | Bit5        | Bit4        | Bit3        | Bit2        | Bit1       | Bit0       |

|------------------|---------|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|

| ISPU_CONFIG      | 02h     | 6802h           | 0           | 0           | 0           | LATCHED     | 0           | 0           | CLK_DIS    | ISPU_RST_N |

| ISPU_STATUS      | 04h     | 6804h           | 0           | 0           | 0           | 0           | 0           | BOOT_END    | 0          | 0          |

| ISPU_MEM_SEL     | 08h     | -               | 0           | READ_MEM_EN | 0           | 0           | 0           | 0           | 0          | MEM_SEL    |

| ISPU_MEM_ADDR1   | 09h     | -               | MEM_ADDR_15 | MEM_ADDR_14 | MEM_ADDR_13 | MEM_ADDR_12 | MEM_ADDR_11 | MEM_ADDR_10 | MEM_ADDR_9 | MEM_ADDR_8 |

| ISPU_MEM_ADDR0   | 0Ah     | -               | MEM_ADDR_7  | MEM_ADDR_6  | MEM_ADDR_5  | MEM_ADDR_4  | MEM_ADDR_3  | MEM_ADDR_2  | MEM_ADDR_1 | MEM_ADDR_0 |

| ISPU_MEM_DATA    | 0Bh     | -               | MEM_DATA_7  | MEM_DATA_6  | MEM_DATA_5  | MEM_DATA_4  | MEM_DATA_3  | MEM_DATA_2  | MEM_DATA_1 | MEM_DATA_0 |

| ISPU_IF2S_FLAG_L | 0Ch     | 680Ch           | IF2S_7      | IF2S_6      | IF2S_5      | IF2S_4      | IF2S_3      | IF2S_2      | IF2S_1     | IF2S_0     |

| ISPU_IF2S_FLAG_H | 0Dh     | 680Dh           | IF2S_15     | IF2S_14     | IF2S_13     | IF2S_12     | IF2S_11     | IF2S_10     | IF2S_9     | IF2S_8     |

| ISPU_S2IF_FLAG_L | 0Eh     | 680Eh           | S2IF_7      | S2IF_6      | S2IF_5      | S2IF_4      | S2IF_3      | S2IF_2      | S2IF_1     | S2IF_0     |

| ISPU_S2IF_FLAG_H | 0Fh     | 680Fh           | S2IF_15     | S2IF_14     | S2IF_13     | S2IF_12     | S2IF_11     | S2IF_10     | S2IF_9     | S2IF_8     |

| ISPU_DOUT_00_L   | 10h     | 6810h           | DOUT0_7     | DOUT0_6     | DOUT0_5     | DOUT0_4     | DOUT0_3     | DOUT0_2     | DOUT0_1    | DOUT0_0    |

| ISPU_DOUT_00_H   | 11h     | 6811h           | DOUT0_15    | DOUT0_14    | DOUT0_13    | DOUT0_12    | DOUT0_11    | DOUT0_10    | DOUT0_9    | DOUT0_8    |

| ISPU_DOUT_01_L   | 12h     | 6812h           | DOUT1_7     | DOUT1_6     | DOUT1_5     | DOUT1_4     | DOUT1_3     | DOUT1_2     | DOUT1_1    | DOUT1_0    |

| ISPU_DOUT_01_H   | 13h     | 6813h           | DOUT1_15    | DOUT1_14    | DOUT1_13    | DOUT1_12    | DOUT1_11    | DOUT1_10    | DOUT1_9    | DOUT1_8    |

| ISPU_DOUT_02_L   | 14h     | 6814h           | DOUT2_7     | DOUT2_6     | DOUT2_5     | DOUT2_4     | DOUT2_3     | DOUT2_2     | DOUT2_1    | DOUT2_0    |

| ISPU_DOUT_02_H   | 15h     | 6815h           | DOUT2_15    | DOUT2_14    | DOUT2_13    | DOUT2_12    | DOUT2_11    | DOUT2_10    | DOUT2_9    | DOUT2_8    |

| ISPU_DOUT_03_L   | 16h     | 6816h           | DOUT3_7     | DOUT3_6     | DOUT3_5     | DOUT3_4     | DOUT3_3     | DOUT3_2     | DOUT3_1    | DOUT3_0    |

| ISPU_DOUT_03_H   | 17h     | 6817h           | DOUT3_15    | DOUT3_14    | DOUT3_13    | DOUT3_12    | DOUT3_11    | DOUT3_10    | DOUT3_9    | DOUT3_8    |

| ISPU_DOUT_04_L   | 18h     | 6818h           | DOUT4_7     | DOUT4_6     | DOUT4_5     | DOUT4_4     | DOUT4_3     | DOUT4_2     | DOUT4_1    | DOUT4_0    |

| ISPU_DOUT_04_H   | 19h     | 6819h           | DOUT4_15    | DOUT4_14    | DOUT4_13    | DOUT4_12    | DOUT4_11    | DOUT4_10    | DOUT4_9    | DOUT4_8    |

| ISPU_DOUT_05_L   | 1Ah     | 681Ah           | DOUT5_7     | DOUT5_6     | DOUT5_5     | DOUT5_4     | DOUT5_3     | DOUT5_2     | DOUT5_1    | DOUT5_0    |

| ISPU_DOUT_05_H   | 1Bh     | 681Bh           | DOUT5_15    | DOUT5_14    | DOUT5_13    | DOUT5_12    | DOUT5_11    | DOUT5_10    | DOUT5_9    | DOUT5_8    |

| ISPU_DOUT_06_L   | 1Ch     | 681Ch           | DOUT6_7     | DOUT6_6     | DOUT6_5     | DOUT6_4     | DOUT6_3     | DOUT6_2     | DOUT6_1    | DOUT6_0    |

| ISPU_DOUT_06_H   | 1Dh     | 681Dh           | DOUT6_15    | DOUT6_14    | DOUT6_13    | DOUT6_12    | DOUT6_11    | DOUT6_10    | DOUT6_9    | DOUT6_8    |

| ISPU_DOUT_07_L   | 1Eh     | 681Eh           | DOUT7_7     | DOUT7_6     | DOUT7_5     | DOUT7_4     | DOUT7_3     | DOUT7_2     | DOUT7_1    | DOUT7_0    |

| ISPU_DOUT_07_H   | 1Fh     | 681Fh           | DOUT7_15    | DOUT7_14    | DOUT7_13    | DOUT7_12    | DOUT7_11    | DOUT7_10    | DOUT7_9    | DOUT7_8    |

| ISPU_DOUT_08_L   | 20h     | 6820h           | DOUT8_7     | DOUT8_6     | DOUT8_5     | DOUT8_4     | DOUT8_3     | DOUT8_2     | DOUT8_1    | DOUT8_0    |

| ISPU_DOUT_08_H   | 21h     | 6821h           | DOUT8_15    | DOUT8_14    | DOUT8_13    | DOUT8_12    | DOUT8_11    | DOUT8_10    | DOUT8_9    | DOUT8_8    |

#### Table 3. ISPU interaction registers

2.1

|                   |         | ISPU    |               |               |               |               |               |               |              |          |

|-------------------|---------|---------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|----------|

| Register name     | Address | address | Bit7          | Bit6          | Bit5          | Bit4          | Bit3          | Bit2          | Bit1         | Bit0     |

| SPU_DOUT_09_L     | 22h     | 6822h   | DOUT9_7       | DOUT9_6       | DOUT9_5       | DOUT9_4       | DOUT9_3       | DOUT9_2       | DOUT9_1      | DOUT9_0  |

| SPU_DOUT_09_H     | 23h     | 6823h   | DOUT9_15      | DOUT9_14      | DOUT9_13      | DOUT9_12      | DOUT9_11      | DOUT9_10      | DOUT9_9      | DOUT9_8  |

| SPU_DOUT_10_L     | 24h     | 6824h   | DOUT10_7      | DOUT10_6      | DOUT10_5      | DOUT10_4      | DOUT10_3      | DOUT10_2      | DOUT10_1     | DOUT10_0 |

| SPU_DOUT_10_H     | 25h     | 6825h   | DOUT10_15     | DOUT10_14     | DOUT10_13     | DOUT10_12     | DOUT10_11     | DOUT10_10     | DOUT10_9     | DOUT10_8 |

| SPU_DOUT_11_L     | 26h     | 6826h   | DOUT11_7      | DOUT11_6      | DOUT11_5      | DOUT11_4      | DOUT11_3      | DOUT11_2      | DOUT11_1     | DOUT11_0 |

| SPU_DOUT_11_H     | 27h     | 6827h   | DOUT11_15     | DOUT11_14     | DOUT11_13     | DOUT11_12     | DOUT11_11     | DOUT11_10     | DOUT11_9     | DOUT11_8 |

| SPU_DOUT_12_L     | 28h     | 6828h   | DOUT12_7      | DOUT12_6      | DOUT12_5      | DOUT12_4      | DOUT12_3      | DOUT12_2      | DOUT12_1     | DOUT12_0 |

| SPU_DOUT_12_H     | 29h     | 6829h   | DOUT12_15     | DOUT12_14     | DOUT12_13     | DOUT12_12     | DOUT0_11      | DOUT12_10     | DOUT12_9     | DOUT12_8 |

| SPU_DOUT_13_L     | 2Ah     | 682Ah   | DOUT13_7      | DOUT13_6      | DOUT13_5      | DOUT13_4      | DOUT13_3      | DOUT13_2      | DOUT13_1     | DOUT13_0 |

| SPU_DOUT_13_H     | 2Bh     | 682Bh   | DOUT13_15     | DOUT13_14     | DOUT13_13     | DOUT13_12     | DOUT13_11     | DOUT13_10     | DOUT13_9     | DOUT13_8 |

| SPU_DOUT_14_L     | 2Ch     | 682Ch   | DOUT14_7      | DOUT14_6      | DOUT14_5      | DOUT14_4      | DOUT14_3      | DOUT14_2      | DOUT14_1     | DOUT14_0 |

| SPU_DOUT_14_H     | 2Dh     | 682Dh   | DOUT14_15     | DOUT14_14     | DOUT14_13     | DOUT14_12     | DOUT14_11     | DOUT14_10     | DOUT14_9     | DOUT14_8 |

| SPU_DOUT_15_L     | 2Eh     | 682Eh   | DOUT15_7      | DOUT15_6      | DOUT15_5      | DOUT15_4      | DOUT15_3      | DOUT15_2      | DOUT15_1     | DOUT15_0 |

| SPU_DOUT_15_H     | 2Fh     | 682Fh   | DOUT15_15     | DOUT15_14     | DOUT15_13     | DOUT15_12     | DOUT15_11     | DOUT15_10     | DOUT15_9     | DOUT15_8 |

| SPU_DOUT_16_L     | 30h     | 6830h   | DOUT16_7      | DOUT16_6      | DOUT16_5      | DOUT16_4      | DOUT16_3      | DOUT16_2      | DOUT16_1     | DOUT16_0 |

| SPU_DOUT_16_H     | 31h     | 6831h   | DOUT16_15     | DOUT16_14     | DOUT16_13     | DOUT16_12     | DOUT16_11     | DOUT16_10     | DOUT16_9     | DOUT16_8 |

| SPU_DOUT_17_L     | 32h     | 6832h   | DOUT17_7      | DOUT17_6      | DOUT17_5      | DOUT17_4      | DOUT17_3      | DOUT17_2      | DOUT17_1     | DOUT17_0 |

| SPU_DOUT_17_H     | 33h     | 6833h   | DOUT17_15     | DOUT17_14     | DOUT17_13     | DOUT17_12     | DOUT17_11     | DOUT17_10     | DOUT17_9     | DOUT17_8 |

| SPU_DOUT_18_L     | 34h     | 6834h   | DOUT18_7      | DOUT18_6      | DOUT18_5      | DOUT18_4      | DOUT18_3      | DOUT18_2      | DOUT18_1     | DOUT18_0 |

| SPU_DOUT_18_H     | 35h     | 6835h   | DOUT18_15     | DOUT18_14     | DOUT18_13     | DOUT18_12     | DOUT18_11     | DOUT18_10     | DOUT18_9     | DOUT18_8 |

| SPU_DOUT_19_L     | 36h     | 6836h   | DOUT19_7      | DOUT19_6      | DOUT19_5      | DOUT19_4      | DOUT19_3      | DOUT19_2      | DOUT19_1     | DOUT19_0 |

| SPU_DOUT_19_H     | 37h     | 6837h   | DOUT19_15     | DOUT19_14     | DOUT19_13     | DOUT19_12     | DOUT19_11     | DOUT19_10     | DOUT19_9     | DOUT19_8 |

| SPU_DOUT_20_L     | 38h     | 6838h   | DOUT20_7      | DOUT20_6      | DOUT20_5      | DOUT20_4      | DOUT20_3      | DOUT20_2      | DOUT20_1     | DOUT20_0 |

| SPU_DOUT_20_H     | 39h     | 6839h   | DOUT20_15     | DOUT20_14     | DOUT20_13     | DOUT20_12     | DOUT20_11     | DOUT20_10     | DOUT20_9     | DOUT20_8 |

| SPU_DOUT_21_L     | 3Ah     | 683Ah   | DOUT21_7      | DOUT21_6      | DOUT21_5      | DOUT21_4      | DOUT21_3      | DOUT21_2      | DOUT21_1     | DOUT21_0 |

| SPU_DOUT_21_H     | 3Bh     | 683Bh   | DOUT21_15     | DOUT21_14     | DOUT21_13     | DOUT21_12     | DOUT21_11     | DOUT21_10     | DOUT21_9     | DOUT21_8 |

| SPU_DOUT_22_L     | 3Ch     | 683Ch   | DOUT22_7      | DOUT22_6      | DOUT22_5      | DOUT22_4      | DOUT22_3      | DOUT22_2      | DOUT22_1     | DOUT22_0 |

| SPU_DOUT_22_H     | 3Dh     | 683Dh   | DOUT22_15     | DOUT22_14     | DOUT22_13     | DOUT22_12     | DOUT22_11     | DOUT22_10     | DOUT22_9     | DOUT22_8 |

| SPU_DOUT_23_L     | 3Eh     | 683Eh   | DOUT23_7      | DOUT23_6      | DOUT23_5      | DOUT23_4      | DOUT23_3      | DOUT23_2      | DOUT23_1     | DOUT23_0 |

| SPU_DOUT_23_H     | 3Fh     | 683Fh   | <br>DOUT23_15 | <br>DOUT23_14 | <br>DOUT23_13 | <br>DOUT23_12 | <br>DOUT23_11 | <br>DOUT23_10 | DOUT23_9     | DOUT23_8 |

| SPU_DOUT_24_L     | 40h     | 6840h   | DOUT24_7      | DOUT24_6      | DOUT24_5      | DOUT24_4      | DOUT24_3      | DOUT24_2      | DOUT24_1     | DOUT24_0 |

| <br>SPU_DOUT_24_H | 41h     | 6841h   | <br>DOUT24_15 | <br>DOUT24_14 | <br>DOUT24_13 | <br>DOUT24_12 | <br>DOUT24_11 | <br>DOUT24_10 | DOUT24_9     | DOUT24_8 |

| SPU_DOUT_25_L     | 42h     | 6842h   | <br>DOUT25_7  | <br>DOUT25_6  | <br>DOUT25_5  | DOUT25_4      | <br>DOUT25_3  | <br>DOUT25_2  | <br>DOUT25_1 | DOUT25_0 |

| SPU_DOUT_25_H     | 43h     | 6843h   | DOUT25_15     | DOUT25_14     | DOUT25_13     | DOUT25_12     | DOUT25_11     | DOUT25_10     | DOUT25_9     | DOUT25 8 |

| Register name    | Address | ISPU<br>address | Bit7                  | Bit6                  | Bit5                  | Bit4                  | Bit3                  | Bit2                  | Bit1                  | Bit0                  |

|------------------|---------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ISPU_DOUT_26_L   | 44h     | 6844h           | DOUT26_7              | DOUT26_6              | DOUT26_5              | DOUT26_4              | DOUT26_3              | DOUT26_2              | DOUT26_1              | DOUT26_0              |

| ISPU_DOUT_26_H   | 45h     | 6845h           | DOUT26_15             | DOUT26_14             | DOUT26_13             | DOUT26_12             | DOUT26_11             | DOUT26_10             | DOUT26_9              | DOUT26_8              |

| ISPU_DOUT_27_L   | 46h     | 6846h           | DOUT27_7              | DOUT27_6              | DOUT27_5              | DOUT27_4              | DOUT27_3              | DOUT27_2              | DOUT27_1              | DOUT27_0              |

| ISPU_DOUT_27_H   | 47h     | 6847h           | DOUT27_15             | DOUT27_14             | DOUT27_13             | DOUT27_12             | DOUT27_11             | DOUT27_10             | DOUT27_9              | DOUT27_8              |

| ISPU_DOUT_28_L   | 48h     | 6848h           | DOUT28_7              | DOUT28_6              | DOUT28_5              | DOUT28_4              | DOUT28_3              | DOUT28_2              | DOUT28_1              | DOUT28_0              |

| ISPU_DOUT_28_H   | 49h     | 6849h           | DOUT28_15             | DOUT28_14             | DOUT28_13             | DOUT28_12             | DOUT28_11             | DOUT28_10             | DOUT28_9              | DOUT28_8              |

| ISPU_DOUT_29_L   | 4Ah     | 684Ah           | DOUT29_7              | DOUT29_6              | DOUT29_5              | DOUT29_4              | DOUT29_3              | DOUT29_2              | DOUT29_1              | DOUT29_0              |

| ISPU_DOUT_29_H   | 4Bh     | 684Bh           | DOUT29_15             | DOUT29_14             | DOUT29_13             | DOUT29_12             | DOUT29_11             | DOUT29_10             | DOUT29_9              | DOUT29_8              |

| ISPU_DOUT_30_L   | 4Ch     | 684Ch           | DOUT30_7              | DOUT30_6              | DOUT30_5              | DOUT30_4              | DOUT30_3              | DOUT30_2              | DOUT30_1              | DOUT30_0              |

| ISPU_DOUT_30_H   | 4Dh     | 684Dh           | DOUT30_15             | DOUT30_14             | DOUT30_13             | DOUT30_12             | DOUT30_11             | DOUT30_10             | DOUT30_9              | DOUT30_8              |

| ISPU_DOUT_31_L   | 4Eh     | 684Eh           | DOUT31_7              | DOUT31_6              | DOUT10_5              | DOUT31_4              | DOUT31_3              | DOUT31_2              | DOUT31_1              | DOUT31_0              |

| ISPU_DOUT_31_H   | 4Fh     | 684Fh           | DOUT31_15             | DOUT31_14             | DOUT31_13             | DOUT31_12             | DOUT31_11             | DOUT31_10             | DOUT31_9              | DOUT31_8              |

| ISPU_INT1_CTRL0  | 50h     | 6850h           | ISPU_INT1<br>_CTRL7   | ISPU_INT1<br>_CTRL6   | ISPU_INT1<br>_CTRL5   | ISPU_INT1<br>_CTRL4   | ISPU_INT1<br>_CTRL3   | ISPU_INT1<br>_CTRL2   | ISPU_INT1<br>_CTRL1   | ISPU_INT1<br>_CTRL0   |

| ISPU_INT1_CTRL1  | 51h     | 6851h           | ISPU_INT1<br>_CTRL15  | ISPU_INT1<br>_CTRL14  | ISPU_INT1<br>_CTRL13  | ISPU_INT1<br>_CTRL12  | ISPU_INT1<br>_CTRL11  | ISPU_INT1<br>_CTRL10  | ISPU_INT1<br>_CTRL9   | ISPU_INT1<br>_CTRL8   |

| ISPU_INT1_CTRL2  | 52h     | 6852h           | ISPU_INT1<br>_CTRL23  | ISPU_INT1<br>_CTRL22  | ISPU_INT1<br>_CTRL21  | ISPU_INT1<br>_CTRL20  | ISPU_INT1<br>_CTRL19  | ISPU_INT1<br>_CTRL18  | ISPU_INT1<br>_CTRL17  | ISPU_INT1<br>_CTRL16  |

| ISPU_INT1_CTRL3  | 53h     | 6853h           | 0                     | 0                     | ISPU_INT1<br>_CTRL29  | ISPU_INT1<br>_CTRL28  | ISPU_INT1<br>_CTRL27  | ISPU_INT1<br>_CTRL26  | ISPU_INT1<br>_CTRL25  | ISPU_INT1<br>_CTRL24  |

| ISPU_INT2_CTRL0  | 54h     | 6854h           | ISPU_INT2<br>_CTRL7   | ISPU_INT2<br>_CTRL6   | ISPU_INT2<br>_CTRL5   | ISPU_INT2<br>_CTRL4   | ISPU_INT2<br>_CTRL3   | ISPU_INT2<br>_CTRL2   | ISPU_INT2<br>_CTRL1   | ISPU_INT2<br>_CTRL0   |

| ISPU_INT2_CTRL1  | 55h     | 6855h           | ISPU_INT2<br>_CTRL15  | ISPU_INT2<br>_CTRL14  | ISPU_INT2<br>_CTRL13  | ISPU_INT2<br>_CTRL12  | ISPU_INT2<br>_CTRL11  | ISPU_INT2<br>_CTRL10  | ISPU_INT2<br>_CTRL9   | ISPU_INT2<br>_CTRL8   |

| ISPU_INT2_CTRL2  | 56h     | 6856h           | ISPU_INT2<br>_CTRL23  | ISPU_INT2<br>_CTRL22  | ISPU_INT2<br>_CTRL21  | ISPU_INT2<br>_CTRL20  | ISPU_INT2<br>_CTRL19  | ISPU_INT2<br>_CTRL18  | ISPU_INT2<br>_CTRL17  | ISPU_INT2<br>_CTRL16  |

| ISPU_INT2_CTRL3  | 57h     | 6857h           | 0                     | 0                     | ISPU_INT2<br>_CTRL29  | ISPU_INT2<br>_CTRL28  | ISPU_INT2<br>_CTRL27  | ISPU_INT2<br>_CTRL26  | ISPU_INT2<br>_CTRL25  | ISPU_INT2<br>_CTRL24  |

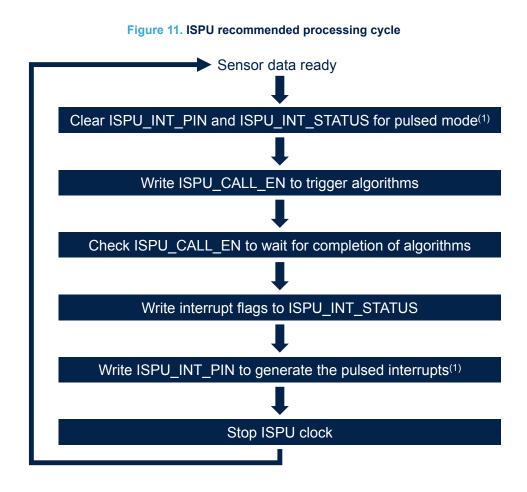

| ISPU_INT_STATUS0 | 58h     | 6858h           | ISPU_INT_<br>STATUS7  | ISPU_INT_<br>STATUS6  | ISPU_INT_<br>STATUS5  | ISPU_INT_<br>STATUS4  | ISPU_INT_<br>STATUS3  | ISPU_INT_<br>STATUS2  | ISPU_INT_<br>STATUS1  | ISPU_INT_<br>STATUS0  |

| ISPU_INT_STATUS1 | 59h     | 6859h           | ISPU_INT_<br>STATUS15 | ISPU_INT_<br>STATUS14 | ISPU_INT_<br>STATUS13 | ISPU_INT_<br>STATUS12 | ISPU_INT_<br>STATUS11 | ISPU_INT_<br>STATUS10 | ISPU_INT_<br>STATUS9  | ISPU_INT_<br>STATUS8  |

| ISPU_INT_STATUS2 | 5Ah     | 685Ah           | ISPU_INT_<br>STATUS23 | ISPU_INT_<br>STATUS22 | ISPU_INT_<br>STATUS21 | ISPU_INT_<br>STATUS20 | ISPU_INT_<br>STATUS19 | ISPU_INT_<br>STATUS18 | ISPU_INT_<br>STATUS17 | ISPU_INT_<br>STATUS16 |

| ISPU_INT_STATUS3 | 5Bh     | 685Bh           | 0                     | 0                     | ISPU_INT_<br>STATUS29 | ISPU_INT_<br>STATUS28 | ISPU_INT_<br>STATUS27 | ISPU_INT_<br>STATUS26 | ISPU_INT_<br>STATUS25 | ISPU_INT_<br>STATUS24 |

| ISPU_ALGO0       | 70h     | 6870h           | ISPU_ALGO7            | ISPU_ALGO6            | ISPU_ALGO5            | ISPU_ALGO4            | ISPU_ALGO3            | ISPU_ALGO2            | ISPU_ALGO1            | ISPU_ALGO0            |

| ISPU_ALGO1       | 71h     | 6871h           | ISPU_ALGO15           | ISPU_ALGO14           | ISPU_ALGO13           | ISPU_ALGO12           | ISPU_ALGO11           | ISPU_ALGO10           | ISPU_ALGO9            | ISPU_ALGO8            |

| ISPU_ALGO2       | 72h     | 6872h           | ISPU_ALGO23           | ISPU_ALGO22           | ISPU_ALGO21           | ISPU_ALGO20           | ISPU_ALGO19           | ISPU_ALGO18           | ISPU_ALGO17           | ISPU_ALGO16           |

| ISPU_ALGO3       | 73h     | 6873h           | 0                     | 0                     | ISPU_ALGO29           | ISPU_ALGO28           | ISPU_ALGO27           | ISPU_ALGO26           | ISPU_ALGO25           | ISPU_ALGO24           |

| ISPU address (hex) | Bytes | Name                                               |

|--------------------|-------|----------------------------------------------------|

| 6940-6941          | 2     | TIMESTAMP0 (40h), TIMESTAMP1 (41h)                 |

| 6942-6943          | 2     | TIMESTAMP2 (42h), TIMESTAMP3 (43h)                 |

| 6974-6975          | 2     | ISPU_DUMMY_CFG_1_L (73h), ISPU_DUMMY_CFG_1_H (74h) |

| 6976-6977          | 2     | ISPU_DUMMY_CFG_2_L (75h), ISPU_DUMMY_CFG_2_H (76h) |

| 6978-6979          | 2     | ISPU_DUMMY_CFG_3_L (77h), ISPU_DUMMY_CFG_3_H (78h) |

| 697A-697B          | 2     | ISPU_DUMMY_CFG_4_L (79h), ISPU_DUMMY_CFG_4_H (7Ah) |

## 2.2 ISPU functions registers

The following table provides a list of the registers internally available in the ISPU architecture.

## Table 5. ISPU interaction registers

| Register name    | ISPU address | Bit7               | Bit6               | Bit5               | Bit4               | Bit3               | Bit2               | Bit1              | Bit0                 |

|------------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------------|----------------------|

| ISPU_GLB_CALL_EN | 6800h        | -                  | -                  | -                  | -                  | -                  | -                  | -                 | ISPU_GLB<br>_CALL_EN |

| ISPU_INT_PIN     | 685Ch        | 0                  | 0                  | 0                  | 0                  | 0                  | 0                  | INT2              | INT1                 |

| ISPU_ARAW_X_L    | 6880h        | ISPU_<br>ARAW_X_7  | ISPU_<br>ARAW_X_6  | ISPU_<br>ARAW_X_5  | ISPU_<br>ARAW_X_4  | ISPU_<br>ARAW_X_3  | ISPU_<br>ARAW_X_2  | ISPU_<br>ARAW_X_1 | ISPU_<br>ARAW_X_0    |

| ISPU_ARAW_X_H    | 6881h        | ISPU_<br>ARAW_X_15 | ISPU_<br>ARAW_X_14 | ISPU_<br>ARAW_X_13 | ISPU_<br>ARAW_X_12 | ISPU_<br>ARAW_X_11 | ISPU_<br>ARAW_X_10 | ISPU_<br>ARAW_X_9 | ISPU_<br>ARAW_X_8    |

| ISPU_ARAW_Y_L    | 6884h        | ISPU_<br>ARAW_Y_7  | ISPU_<br>ARAW_Y_6  | ISPU_<br>ARAW_Y_5  | ISPU_<br>ARAW_Y_4  | ISPU_<br>ARAW_Y_3  | ISPU_<br>ARAW_Y_2  | ISPU_<br>ARAW_Y_1 | ISPU_<br>ARAW_Y_0    |

| ISPU_ARAW_Y_H    | 6885h        | ISPU_<br>ARAW_Y_15 | ISPU_<br>ARAW_Y_14 | ISPU_<br>ARAW_Y_13 | ISPU_<br>ARAW_Y_12 | ISPU_<br>ARAW_Y_11 | ISPU_<br>ARAW_Y_10 | ISPU_<br>ARAW_Y_9 | ISPU_<br>ARAW_Y_8    |

| ISPU_ARAW_Z_L    | 6888h        | ISPU_<br>ARAW_Z_7  | ISPU_<br>ARAW_Z_6  | ISPU_<br>ARAW_Z_5  | ISPU_<br>ARAW_Z_4  | ISPU_<br>ARAW_Z_3  | ISPU_<br>ARAW_Z_2  | ISPU_<br>ARAW_Z_1 | ISPU_<br>ARAW_Z_0    |

| ISPU_ARAW_Z_H    | 6889h        | ISPU_<br>ARAW_Z_15 | ISPU_<br>ARAW_Z_14 | ISPU_<br>ARAW_Z_13 | ISPU_<br>ARAW_Z_12 | ISPU_<br>ARAW_Z_11 | ISPU_<br>ARAW_Z_10 | ISPU_<br>ARAW_Z_9 | ISPU_<br>ARAW_Z_8    |

| ISPU_GRAW_X_L    | 688Ch        | ISPU_<br>GRAW_X_7  | ISPU_<br>GRAW_X_6  | ISPU_<br>GRAW_X_5  | ISPU_<br>GRAW_X_4  | ISPU_<br>GRAW_X_3  | ISPU_<br>GRAW_X_2  | ISPU_<br>GRAW_X_1 | ISPU_<br>GRAW_X_0    |

| ISPU_GRAW_X_H    | 688Dh        | ISPU_<br>GRAW_X_15 | ISPU_<br>GRAW_X_14 | ISPU_<br>GRAW_X_13 | ISPU_<br>GRAW_X_12 | ISPU_<br>GRAW_X_11 | ISPU_<br>GRAW_X_10 | ISPU_<br>GRAW_X_9 | ISPU_<br>GRAW_X_8    |

| ISPU_GRAW_Y_L    | 6890h        | ISPU_<br>GRAW_Y_7  | ISPU_<br>GRAW_Y_6  | ISPU_<br>GRAW_Y_5  | ISPU_<br>GRAW_Y_4  | ISPU_<br>GRAW_Y_3  | ISPU_<br>GRAW_Y_2  | ISPU_<br>GRAW_Y_1 | ISPU_<br>GRAW_Y_0    |

| ISPU_GRAW_Y_H    | 6891h        | ISPU_<br>GRAW_Y_15 | ISPU_<br>GRAW_Y_14 | ISPU_<br>GRAW_Y_13 | ISPU_<br>GRAW_Y_12 | ISPU_<br>GRAW_Y_11 | ISPU_<br>GRAW_Y_10 | ISPU_<br>GRAW_Y_9 | ISPU_<br>GRAW_Y_8    |

| ISPU_GRAW_Z_L    | 6894h        | ISPU_<br>GRAW_Z_7  | ISPU_<br>GRAW_Z_6  | ISPU_<br>GRAW_Z_5  | ISPU_<br>GRAW_Z_4  | ISPU_<br>GRAW_Z_3  | ISPU_<br>GRAW_Z_2  | ISPU_<br>GRAW_Z_1 | ISPU_<br>GRAW_Z_0    |

| ISPU_GRAW_Z_H    | 6895h        | ISPU_<br>GRAW_Z_15 | ISPU_<br>GRAW_Z_14 | ISPU_<br>GRAW_Z_13 | ISPU_<br>GRAW_Z_12 | ISPU_<br>GRAW_Z_11 | ISPU_<br>GRAW_Z_10 | ISPU_<br>GRAW_Z_9 | ISPU_<br>GRAW_z_8    |

| ISPU_ERAW_0_L    | 6898h        | ISPU_<br>ERAW_0_7  | ISPU_<br>ERAW_0_6  | ISPU_<br>ERAW_0_5  | ISPU_<br>ERAW_0_4  | ISPU_<br>ERAW_0_3  | ISPU_<br>ERAW_0_2  | ISPU_<br>ERAW_0_1 | ISPU_<br>ERAW_0_0    |

| ISPU_ERAW_0_H    | 6899h        | ISPU_<br>ERAW_0_15 | ISPU_<br>ERAW_0_14 | ISPU_<br>ERAW_0_13 | ISPU_<br>ERAW_0_12 | ISPU_<br>ERAW_0_11 | ISPU_<br>ERAW_0_10 | ISPU_<br>ERAW_0_9 | ISPU_<br>ERAW_0_8    |

| ISPU_ERAW_1_L    | 689Ch        | ISPU_<br>ERAW_1_7  | ISPU_<br>ERAW_1_6  | ISPU_<br>ERAW_1_5  | ISPU_<br>ERAW_1_4  | ISPU_<br>ERAW_1_3  | ISPU_<br>ERAW_1_2  | ISPU_<br>ERAW_1_1 | ISPU_<br>ERAW_1_0    |

| ISPU_ERAW_1_H    | 689Dh        | ISPU_<br>ERAW_1_15 | ISPU_<br>ERAW_1_14 | ISPU_<br>ERAW_1_13 | ISPU_<br>ERAW_1_12 | ISPU_<br>ERAW_1_11 | ISPU_<br>ERAW_1_10 | ISPU_<br>ERAW_1_9 | ISPU_<br>ERAW_1_8    |

| ISPU_ERAW_2_L    | 68A0h        | ISPU_<br>ERAW_2_7  | ISPU_<br>ERAW_2_6  | ISPU_<br>ERAW_2_5  | ISPU_<br>ERAW_2_4  | ISPU_<br>ERAW_2_3  | ISPU_<br>ERAW_2_2  | ISPU_<br>ERAW_2_1 | ISPU_<br>ERAW_2_0    |

| ISPU_ERAW_2_H    | 68A1h        | ISPU_<br>ERAW_2_15 | ISPU_<br>ERAW_2_14 | ISPU_<br>ERAW_2_13 | ISPU_<br>ERAW_2_12 | ISPU_<br>ERAW_2_11 | ISPU_<br>ERAW_2_10 | ISPU_<br>ERAW_2_9 | ISPU_<br>ERAW_2_8    |

| Register name  | ISPU address | Bit7                  | Bit6                  | Bit5                  | Bit4                  | Bit3                  | Bit2                  | Bit1                  | Bit0                  |

|----------------|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ISPU_TEMP_L    | 68A4h        | ISPU_<br>TEMP_7       | ISPU_<br>TEMP_6       | ISPU_<br>TEMP_5       | ISPU_<br>TEMP_4       | ISPU_<br>TEMP_3       | ISPU_<br>TEMP_2       | ISPU_<br>TEMP_1       | ISPU_<br>TEMP_0       |

| ISPU_TEMP_H    | 68A5h        | ISPU_<br>TEMP_15      | ISPU_<br>TEMP_14      | ISPU_<br>TEMP_13      | ISPU_<br>TEMP_12      | ISPU_<br>TEMP_11      | ISPU_<br>TEMP_10      | ISPU_<br>TEMP_9       | ISPU_<br>TEMP_8       |

| ISPU_CALL_EN_0 | 68B8h        | ISPU_CALL_<br>ALGO_6  | ISPU_CALL_<br>ALGO_5  | ISPU_CALL_<br>ALGO_4  | ISPU_CALL_<br>ALGO_3  | ISPU_CALL_<br>ALGO_2  | ISPU_CALL_<br>ALGO_1  | ISPU_CALL_<br>ALGO_0  | 0                     |

| ISPU_CALL_EN_1 | 68B9h        | ISPU_CALL_<br>ALGO_14 | ISPU_CALL_<br>ALGO_13 | ISPU_CALL_<br>ALGO_12 | ISPU_CALL_<br>ALGO_11 | ISPU_CALL_<br>ALGO_10 | ISPU_CALL_<br>ALGO_9  | ISPU_CALL_<br>ALGO_8  | ISPU_CALL_<br>ALGO_7  |

| ISPU_CALL_EN_2 | 68BAh        | ISPU_CALL_<br>ALGO_22 | ISPU_CALL_<br>ALGO_21 | ISPU_CALL_<br>ALGO_20 | ISPU_CALL_<br>ALGO_19 | ISPU_CALL_<br>ALGO_18 | ISPU_CALL_<br>ALGO_17 | ISPU_CALL_<br>ALGO_16 | ISPU_CALL_<br>ALGO_15 |

| ISPU_CALL_EN_3 | 68BBh        | 0                     | ISPU_CALL_<br>ALGO_29 | ISPU_CALL_<br>ALGO_28 | ISPU_CALL_<br>ALGO_27 | ISPU_CALL_<br>ALGO_26 | ISPU_CALL_<br>ALGO_25 | ISPU_CALL_<br>ALGO_24 | ISPU_CALL_<br>ALGO_23 |

| ISPU_DTIME_0_L | 6948h        | ISPU_DTIME_7          | ISPU_DTIME_6          | ISPU_DTIME_5          | ISPU_DTIME_4          | ISPU_DTIME_3          | ISPU_DTIME_2          | ISPU_DTIME_1          | ISPU_DTIME_0          |

| ISPU_DTIME_0_H | 6949h        | ISPU_DTIME_15         | ISPU_DTIME_14         | ISPU_DTIME_13         | ISPU_DTIME_12         | ISPU_DTIME_11         | ISPU_DTIME_10         | ISPU_DTIME_9          | ISPU_DTIME_8          |

| ISPU_DTIME_1_L | 694Ah        | ISPU_DTIME_23         | ISPU_DTIME_22         | ISPU_DTIME_21         | ISPU_DTIME_20         | ISPU_DTIME_19         | ISPU_DTIME_18         | ISPU_DTIME_17         | ISPU_DTIME_16         |

| ISPU_DTIME_1_H | 694Bh        | ISPU_DTIME_31         | ISPU_DTIME_30         | ISPU_DTIME_29         | ISPU_DTIME_28         | ISPU_DTIME_27         | ISPU_DTIME_26         | ISPU_DTIME_25         | ISPU_DTIME_24         |

5

## 2.3 Sensor hub registers

The sensor hub registers are accessible when bit SHUB\_REG\_ACCESS is set to 1 in the FUNC\_CFG\_ACCESS (01h) register.

## Table 6. Sensor hub registers

| Register name | Address | Bit7                | Bit6          | Bit5          | Bit4                  | Bit3          | Bit2          | Bit1          | Bit0          |

|---------------|---------|---------------------|---------------|---------------|-----------------------|---------------|---------------|---------------|---------------|

| SENSOR_HUB_1  | 02h     | SensorHub1_7        | SensorHub1_6  | SensorHub1_5  | SensorHub1_4          | SensorHub1_3  | SensorHub1_2  | SensorHub1_1  | SensorHub1_0  |

| SENSOR_HUB_2  | 03h     | SensorHub2_7        | SensorHub2_6  | SensorHub2_5  | SensorHub2_4          | SensorHub2_3  | SensorHub2_2  | SensorHub2_1  | SensorHub2_0  |

| SENSOR_HUB_3  | 04h     | SensorHub3_7        | SensorHub3_6  | SensorHub3_5  | SensorHub3_4          | SensorHub3_3  | SensorHub3_2  | SensorHub3_1  | SensorHub3_0  |

| SENSOR_HUB_4  | 05h     | SensorHub4_7        | SensorHub4_6  | SensorHub4_5  | SensorHub4_4          | SensorHub4_3  | SensorHub4_2  | SensorHub4_1  | SensorHub4_0  |

| SENSOR_HUB_5  | 06h     | SensorHub5_7        | SensorHub5_6  | SensorHub5_5  | SensorHub5_4          | SensorHub5_3  | SensorHub5_2  | SensorHub5_1  | SensorHub5_0  |

| SENSOR_HUB_6  | 07h     | SensorHub6_7        | SensorHub6_6  | SensorHub6_5  | SensorHub6_4          | SensorHub6_3  | SensorHub6_2  | SensorHub6_1  | SensorHub6_0  |

| SENSOR_HUB_7  | 08h     | SensorHub7_7        | SensorHub7_6  | SensorHub7_5  | SensorHub7_4          | SensorHub7_3  | SensorHub7_2  | SensorHub7_1  | SensorHub7_0  |

| SENSOR_HUB_8  | 09h     | SensorHub8_7        | SensorHub8_6  | SensorHub8_5  | SensorHub8_4          | SensorHub8_3  | SensorHub8_2  | SensorHub8_1  | SensorHub8_0  |

| SENSOR_HUB_9  | 0Ah     | SensorHub9_7        | SensorHub9_6  | SensorHub9_5  | SensorHub9_4          | SensorHub9_3  | SensorHub9_2  | SensorHub9_1  | SensorHub9_0  |

| SENSOR_HUB_10 | 0Bh     | SensorHub10_7       | SensorHub10_6 | SensorHub10_5 | SensorHub10_4         | SensorHub10_3 | SensorHub10_2 | SensorHub10_1 | SensorHub10_0 |

| SENSOR_HUB_11 | 0Ch     | SensorHub11_7       | SensorHub11_6 | SensorHub11_5 | SensorHub11_4         | SensorHub11_3 | SensorHub11_2 | SensorHub11_1 | SensorHub11_0 |

| SENSOR_HUB_12 | 0Dh     | SensorHub12_7       | SensorHub12_6 | SensorHub12_5 | SensorHub12_4         | SensorHub12_3 | SensorHub12_2 | SensorHub12_1 | SensorHub12_0 |

| SENSOR_HUB_13 | 0Eh     | SensorHub13_7       | SensorHub13_6 | SensorHub13_5 | SensorHub13_4         | SensorHub13_3 | SensorHub13_2 | SensorHub13_1 | SensorHub13_0 |

| SENSOR_HUB_14 | 0Fh     | SensorHub14_7       | SensorHub14_6 | SensorHub14_5 | SensorHub14_4         | SensorHub14_3 | SensorHub14_2 | SensorHub14_1 | SensorHub14_0 |

| SENSOR_HUB_15 | 10h     | SensorHub15_7       | SensorHub15_6 | SensorHub15_5 | SensorHub15_4         | SensorHub15_3 | SensorHub15_2 | SensorHub15_1 | SensorHub15_0 |

| SENSOR_HUB_16 | 11h     | SensorHub16_7       | SensorHub16_6 | SensorHub16_5 | SensorHub16_4         | SensorHub16_3 | SensorHub16_2 | SensorHub16_1 | SensorHub16_0 |

| SENSOR_HUB_17 | 12h     | SensorHub17_7       | SensorHub17_6 | SensorHub17_5 | SensorHub17_4         | SensorHub17_3 | SensorHub17_2 | SensorHub17_1 | SensorHub17_0 |

| SENSOR_HUB_18 | 13h     | SensorHub18_7       | SensorHub18_6 | SensorHub18_5 | SensorHub18_4         | SensorHub18_3 | SensorHub18_2 | SensorHub18_1 | SensorHub18_0 |

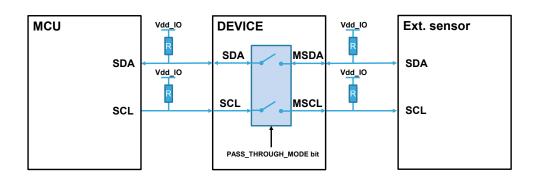

| MASTER_CONFIG | 14h     | RST_MASTER<br>_REGS | WRITE_ONCE    | START_CONFIG  | PASS_<br>THROUGH_MODE | SHUB_PU_EN    | MASTER_ON     | AUX_SENS_ON_1 | AUX_SENS_ON_0 |

| SLV0_ADD      | 15h     | slave0_add6         | slave0_add5   | slave0_add4   | slave0_add3           | slave0_add2   | slave0_add1   | slave0_add0   | rw_0          |

| SLV0_SUBADD   | 16h     | slave0_reg7         | slave0_reg6   | slave0_reg5   | slave0_reg4           | slave0_reg3   | slave0_reg2   | slave0_reg1   | slave0_reg0   |

| SLV0_CONFIG   | 17h     | SHUB_ODR_1          | SHUB_ODR_0    | 0             | 0                     | 0             | Slave0_numop2 | Slave0_numop1 | Slave0_numop0 |

| SLV1_ADD      | 18h     | Slave1_add6         | Slave1_add5   | Slave1_add4   | Slave1_add3           | Slave1_add2   | Slave1_add1   | Slave1_add0   | r_1           |

| SLV1_SUBADD   | 19h     | Slave1_reg7         | Slave1_reg6   | Slave1_reg5   | Slave1_reg4           | Slave1_reg3   | Slave1_reg2   | Slave1_reg1   | Slave1_reg0   |

| SLV1_CONFIG   | 1Ah     | 0                   | 0             | 0             | 0                     | 0             | Slave1_numop2 | Slave1_numop1 | Slave1_numop0 |

| SLV2_ADD      | 1Bh     | Slave2_add6         | Slave2_add5   | Slave2_add4   | Slave2_add3           | Slave2_add2   | Slave2_add1   | Slave2_add0   | r_2           |

| SLV2_SUBADD   | 1Ch     | Slave2_reg7         | Slave2_reg6   | Slave2_reg5   | Slave2_reg4           | Slave2_reg3   | Slave2_reg2   | Slave2_reg1   | Slave2_reg0   |

| SLV2_CONFIG   | 1Dh     | 0                   | 0             | 0             | 0                     | 0             | Slave2_numop2 | Slave2_numop1 | Slave2_numop0 |

| SLV3_ADD      | 1Eh     | Slave3_add6         | Slave3_add5   | Slave3_add4   | Slave3_add3           | Slave3_add2   | Slave3_add1   | Slave3_add0   | r_3           |

| SLV3_SUBADD   | 1Fh     | Slave3_reg7         | Slave3_reg6   | Slave3_reg5   | Slave3_reg4           | Slave3_reg3   | Slave3_reg2   | Slave3_reg1   | Slave3_reg0   |

| Register name  | Address | Bit7          | Bit6          | Bit5          | Bit4          | Bit3          | Bit2          | Bit1          | Bit0               |

|----------------|---------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------------|

| SLV3_CONFIG    | 20h     | 0             | 0             | 0             | 0             | 0             | Slave3_numop2 | Slave3_numop1 | Slave3_numop0      |

| DATAWRITE_SLV0 | 21h     | Slave0_dataw7 | Slave0_dataw6 | Slave0_dataw5 | Slave0_dataw4 | Slave0_dataw3 | Slave0_dataw2 | Slave0_dataw1 | Slave0_dataw0      |

| STATUS_MASTER  | 22h     | WR_ONCE_DONE  | SLAVE3_NACK   | SLAVE2_NACK   | SLAVE1_NACK   | SLAVE0_NACK   | 0             | 0             | SENS_HUB<br>_ENDOP |

## 3 Operating modes

The ISM330IS provides three possible operating configurations:

- only accelerometer active and gyroscope in power-down or sleep mode

- only gyroscope active and accelerometer in power-down

- both accelerometer and gyroscope active with independent ODR

The device offers a wide Vdd voltage range from 1.71 V to 3.6 V and a Vdd\_IO range from 1.62 V to 3.6 V. The power-on sequence is not restricted. The Vdd/Vdd\_IO pins can be set to either power supply level or to ground level (they must not be left floating) and no specific sequence is required for powering them on.

In order to avoid potential conflicts, during the power-on sequence it is recommended to set the lines (on the host side) connected to the device IO pins floating or connected to ground, until Vdd\_IO is set. After Vdd\_IO is set, the lines connected to the IO pins have to be configured according to their default status described in Table 1. In order to avoid an unexpected increase in current consumption, the input pins which are not pulled-up/pulled-down must be polarized by the host.

When the Vdd power supply is applied, the device performs a 10 ms (maximum) boot procedure to load the trimming parameters. After the boot is completed, both the accelerometer and the gyroscope are automatically configured in power-down mode. To guarantee proper power-off of the device it is recommended to maintain the duration of the Vdd line to GND for at least 100 µs.

The accelerometer and the gyroscope can be independently configured in three different power modes: powerdown, low-power, and high-performance mode. They are allowed to have different data rates without any limit. The gyroscope sensor can also be set in sleep mode to reduce its power consumption.

When both the accelerometer and gyroscope are on, the accelerometer is synchronized with the gyroscope, and the data rates of the two sensors are integer multiples of each other.

Referring to the ISM330IS datasheet, the output data rate (ODR\_XL) bits of the CTRL1\_XL register and the high-performance mode (XL\_HM\_MODE) bit of the CTRL6\_C register are used to select the output data rate and the power mode of the accelerometer (Table 7. Accelerometer ODR and power mode selection).

| ODR_XL[3:0] | ODR when                        | ODR when                        |

|-------------|---------------------------------|---------------------------------|

|             | XL_HM_MODE = 1                  | XL_HM_MODE = 0                  |

| 0000        | Power-down mode                 | Power-down mode                 |

| 1011        | 1.6 Hz (low-power mode only)    | 12.5 Hz (high-performance mode) |

| 0001        | 12.5 Hz (low-power mode)        | 12.5 Hz (high-performance mode) |

| 0010        | 26 Hz (low-power mode)          | 26 Hz (high-performance mode)   |

| 0011        | 52 Hz (low-power mode)          | 52 Hz (high-performance mode)   |

| 0100        | 104 Hz (low-power mode)         | 104 Hz (high-performance mode)  |

| 0101        | 208 Hz (low-power mode)         | 208 Hz (high-performance mode)  |

| 0110        | 416 Hz (high-performance mode)  | 416 Hz (high-performance mode)  |

| 0111        | 833 Hz (high-performance mode)  | 833 Hz (high-performance mode)  |

| 1000        | 1667 Hz (high-performance mode) | 1667 Hz (high-performance mode) |

| 1001        | 3333 Hz (high-performance mode) | 3333 Hz (high-performance mode) |

| 1010        | 6667 Hz (high-performance mode) | 6667 Hz (high-performance mode) |

#### Table 7. Accelerometer ODR and power mode selection

The output data rate (ODR\_G) bits of the CTRL2\_G register and the high-performance mode (G\_HM\_MODE) bit of the CTRL7\_G register are used to select the output data rate and the power mode of the gyroscope sensor (Table 8. Gyroscope ODR and power mode selection).

| ODR_G[3:0] | ODR when                                              | ODR when                        |  |  |

|------------|-------------------------------------------------------|---------------------------------|--|--|

|            | G_HM_MODE = 1                                         | G_HM_MODE = 0                   |  |  |

| 0000       | Power-down mode                                       | Power-down mode                 |  |  |

| 0001       | 12.5 Hz (low-power mode)                              | 12.5 Hz (high-performance mode) |  |  |

| 0010       | 26 Hz (low-power mode)                                | 26 Hz (high-performance mode)   |  |  |

| 0011       | 52 Hz (low-power mode)                                | 52 Hz (high-performance mode)   |  |  |

| 0100       | 104 Hz (low-power mode)104 Hz (high-performance mode) |                                 |  |  |

| 0101       | 208 Hz (low-power mode)                               | 208 Hz (high-performance mode)  |  |  |

| 0110       | 416 Hz (high-performance mode)                        | 416 Hz (high-performance mode)  |  |  |

| 0111       | 833 Hz (high-performance mode)                        | 833 Hz (high-performance mode)  |  |  |

| 1000       | 1667 Hz (high-performance mode)                       | 1667 Hz (high-performance mode) |  |  |

| 1001       | 3333 Hz (high-performance mode)                       | 3333 Hz (high-performance mode) |  |  |

| 1010       | 6667 Hz (high-performance mode)                       | 6667 Hz (high-performance mode) |  |  |

#### Table 8. Gyroscope ODR and power mode selection

Table 9. Power consumption (@ Vdd = 1.8 V, T = 25  $^{\circ}$ C) shows the typical values of power consumption for the different operating modes.

| ODR [Hz]                        | Accelerometer only | Gyroscope only | Combo [accelerometer + gyroscope] |  |  |  |  |

|---------------------------------|--------------------|----------------|-----------------------------------|--|--|--|--|

| Power-down mode                 | -                  | -              | 6 μΑ                              |  |  |  |  |

| Sleep mode                      | -                  | 285 µA         | -                                 |  |  |  |  |

| 1.6 Hz (low-power mode)         | 15 µA              | -              | -                                 |  |  |  |  |

| 12.5 Hz (low-power mode)        | 20 µA              | 290 µA         | 300 µA                            |  |  |  |  |

| 26 Hz (low-power mode)          | 25 μΑ              | 300 µA         | 310 µA                            |  |  |  |  |

| 52 Hz (low-power mode)          | 37 µA              | 320 µA         | 330 µA                            |  |  |  |  |

| 104 Hz (low-power mode)         | 55 μΑ              | 350 µA         | 375 μΑ                            |  |  |  |  |

| 208 Hz (low-power mode)         | 97 µA              | 410 µA         | 465 µA                            |  |  |  |  |

| 12.5 Hz (high-performance mode) | 180 µA             | 490 µA         | 595 µA                            |  |  |  |  |

| 26 Hz (high-performance mode)   | 180 µA             | 490 µA         | 595 μΑ                            |  |  |  |  |

| 52 Hz (high-performance mode)   | 180 µA             | 490 µA         | 595 μΑ                            |  |  |  |  |

| 104 Hz (high-performance mode)  | 180 µA             | 490 µA         | 595 μΑ                            |  |  |  |  |

| 208 Hz (high-performance mode)  | 180 µA             | 490 µA         | 595 μΑ                            |  |  |  |  |

| 416 Hz (high-performance mode)  | 180 µA             | 490 µA         | 595 μΑ                            |  |  |  |  |

| 833 Hz (high-performance mode)  | 180 µA             | 490 µA         | 595 µA                            |  |  |  |  |

| 1667 Hz (high-performance mode) | 180 µA             | 490 µA         | 595 µA                            |  |  |  |  |

| 3333 Hz (high-performance mode) | 180 µA             | 490 µA         | 595 µA                            |  |  |  |  |

| 6667 Hz (high-performance mode) | 180 µA             | 490 µA         | 595 µA                            |  |  |  |  |

#### Table 9. Power consumption (@ Vdd = 1.8 V, T = 25 °C)

### 3.1 Power-down mode

When the accelerometer/gyroscope is in power-down mode, almost all internal blocks of the device are switched off to minimize power consumption. The digital interfaces (I<sup>2</sup>C and SPI) are still active to allow communication with the device. The content of the configuration registers is preserved and the output data registers are not updated, keeping the last data sampled in memory before going into power-down mode.

## 3.2 High-performance mode

In high-performance mode, all accelerometer/gyroscope circuitry is always on and data are generated at the data rate selected through the ODR\_XL/ODR\_G bits.

Data interrupt generation is active.

#### 3.3 Low-power mode

While high-performance mode guarantees the best performance in terms of noise, low-power mode further reduces the current consumption. The accelerometer/gyroscope data reading chain is automatically turned on and off to save power. In the gyroscope device, only the driving circuitry is always on. Data interrupt generation is active.

## 3.4 Gyroscope sleep mode

While the gyroscope is in sleep mode the circuitry that drives the oscillation of the gyroscope mass is kept active. Compared to gyroscope power-down, turn-on time from sleep mode to low-power/high-performance mode is drastically reduced.

If the gyroscope is not configured in power-down mode, it enters sleep mode when the sleep mode (SLEEP\_G) bit of the CTRL4\_C register is set to 1, regardless of the selected gyroscope ODR. If the gyroscope is configured in power-down mode, the SLEEP\_G bit configuration is ignored.

## **3.5** Connection modes

The ISM330IS offers two different connection modes, described in detail in this document:

- Mode 1: it is the connection mode enabled by default. The I<sup>2</sup>C slave interface or SPI (3- / 4-wire) serial interface is available.

- Mode 2: it is the sensor hub mode. The I<sup>2</sup>C slave interface or SPI (3- / 4-wire) serial interface and I<sup>2</sup>C interface master for external sensor connections are available. This connection mode is described in Section 6 Mode 2 - sensor hub mode.

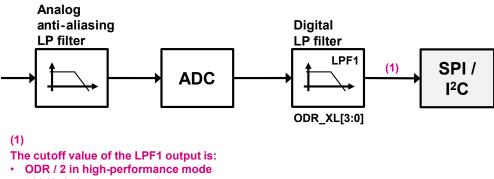

## 3.6 Accelerometer bandwidth

The accelerometer sampling chain is represented by a cascade of three main blocks: an analog anti-aliasing low-pass filter, an ADC converter, and a digital low-pass filter.

As shown in Figure 2. Accelerometer filtering chain, the analog signal coming from the mechanical parts is filtered by an analog low-pass anti-aliasing filter before being converted by the ADC. The anti-aliasing filter is enabled in high-performance mode only.

• 700 Hz in low-power mode

The digital low-pass filter LPF1 cannot be configured by the user and its cutoff frequency depends on the accelerometer mode selected:

- ODR / 2 when the accelerometer is configured in high-performance mode

- 700 Hz when the accelerometer is configured in low-power mode

## **3.7 Gyroscope bandwidth**

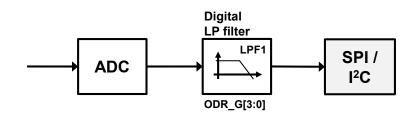

The gyroscope filtering chain configuration is shown in Figure 3. Gyroscope filtering chain. The analog signal coming from the mechanical parts is converted by the ADC and the converted signal is then processed by a digital low-pass filter (LPF1).

#### Figure 3. Gyroscope filtering chain

The digital LPF1 filter cannot be configured by the user and its cutoff frequency depends on the selected gyroscope ODR. When the gyroscope ODR is equal to 6667 Hz, the LPF1 filter is bypassed. The gyroscope bandwidth is summarized in the following table.

#### Table 10. Gyroscope bandwidth

| Gyroscope ODR [Hz] | Bandwidth [Hz] |

|--------------------|----------------|

| 12.5               | 4              |

| 26                 | 8              |

| 52                 | 17             |

| 104                | 33             |

| 208                | 67             |

| 416                | 137            |

| 833                | 312            |

| 1667               | 988            |

| 3333               | 1161           |

| 6667               | 1250           |

## 3.8 Accelerometer and gyroscope turn-on/off time

The accelerometer reading chain contains low-pass filtering to improve signal-to-noise performance and to reduce aliasing effects. For this reason, it is necessary to take into account the settling time of the filters when the accelerometer power mode is switched or when the accelerometer ODR is changed.

The maximum overall turn-on/off time in order to switch accelerometer power modes or accelerometer ODR is shown in Table 11. Accelerometer turn-on/off time

*Note:* The accelerometer ODR timing is not impacted by power mode changes (a new configuration is effective after the completion of the current period).

| Starting mode Target mode        |                                     | Max turn-on/off time <sup>(1)</sup>                                               |  |  |  |

|----------------------------------|-------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Power-down                       | Low-power                           | See Table 12. Accelerometer samples to be discarded                               |  |  |  |

| Power-down                       | High-performance                    | See Table 12. Accelerometer samples to be discarded                               |  |  |  |

| Low-power High-performance       |                                     | See Table 12. Accelerometer samples to be discarded + discard 1 additional sample |  |  |  |

| Low-power Low-power (ODR change) |                                     | See Table 12. Accelerometer samples to be discarded                               |  |  |  |

| High-performance Low-power       |                                     | See Table 12. Accelerometer samples to be discarded + discard 1 additional sample |  |  |  |

| High-performance                 | High-performance<br>@ ODR < 6667 Hz | Discard 3 samples                                                                 |  |  |  |

| High-performance                 | gh-performance Discard 7 samples    |                                                                                   |  |  |  |

| Low-power / high-performance     | Power-down                          | 1 µs                                                                              |  |  |  |

## Table 11. Accelerometer turn-on/off time

1. Settling time @ 99% of the final value

#### Table 12. Accelerometer samples to be discarded

| Target mode<br>accelerometer ODR [Hz] | Number of samples to be discarded |  |  |

|---------------------------------------|-----------------------------------|--|--|

| 1.6 (low-power)                       | 0 (first sample correct)          |  |  |

| 12.5 (low-power)                      | 0 (first sample correct)          |  |  |

| 26 (low-power)                        | 0 (first sample correct)          |  |  |

| 52 (low-power)                        | 0 (first sample correct)          |  |  |

| 104 (low-power)                       | 0 (first sample correct)          |  |  |

| 208 (low-power)                       | 0 (first sample correct)          |  |  |

| 12.5 (high-performance)               | 1                                 |  |  |

| 26 (high-performance)                 | 1                                 |  |  |

| 52 (high-performance)                 | 1                                 |  |  |

| 104 (high-performance)                | 1                                 |  |  |

| 208 (high-performance)                | 1                                 |  |  |

| 416 (high-performance)                | 1                                 |  |  |

| 833 (high-performance)                | 1                                 |  |  |

| 1667 (high-performance)               | 4                                 |  |  |

| 3333 (high-performance)               | 10                                |  |  |

| 6667 (high-performance)               | 32                                |  |  |

Turn-on/off time has to be considered also for the gyroscope sensor when switching its modes or when the gyroscope ODR is changed.

The maximum overall turn-on/off time in order to switch gyroscope power modes or gyroscope ODR is shown in Table 13. Gyroscope turn-on/off time.

*Note:* The gyroscope ODR timing is not impacted by power mode changes (a new configuration is effective after the completion of the current period).

| Starting mode               | Target mode                      | Max turn-on/off time <sup>(1)</sup>                                                 |  |  |

|-----------------------------|----------------------------------|-------------------------------------------------------------------------------------|--|--|

| Power-down Sleep            |                                  | 70 ms                                                                               |  |  |

| Power-down                  | Low-power                        | 70 ms + discard 1 sample                                                            |  |  |

| Power-down                  | High-performance                 | 70 ms + see Table 14. Gyroscope samples to be discarded                             |  |  |

| Sleep                       | Low-power                        | Discard 1 sample                                                                    |  |  |

| Sleep                       | High-performance                 | See Table 14. Gyroscope samples to be discarded                                     |  |  |

| Low-power                   | High-performance                 | Discard 2 samples                                                                   |  |  |

| Low-power                   | Low-power<br>(ODR change)        | Discard 1 sample                                                                    |  |  |

| High-performance            | Low-power                        | Discard 1 sample                                                                    |  |  |

| High-performance            | High-performance<br>(ODR change) | Discard 2 samples                                                                   |  |  |

| ow-power / high-performance | Power-down                       | 1 μs if both accelerometer and gyroscope in PD<br>300 μs if accelerometer not in PD |  |  |

#### Table 13. Gyroscope turn-on/off time

1. Settling time @ 99% of the final value

#### Table 14. Gyroscope samples to be discarded

| Gyroscope ODR [Hz] | Number of samples to be discarded |

|--------------------|-----------------------------------|

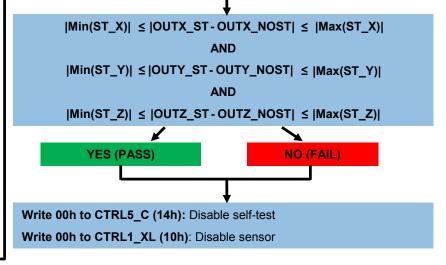

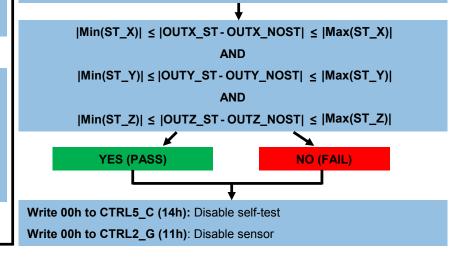

| 12.5 Hz            | 2                                 |