Application note

## SPSB100 NVM configuration

## Introduction

This document is intended to integrate the information provided in the SPSB100 product datasheet, to facilitate the correct procedure to define a customized NVM configuration. A specific focus is reserved to the needed steps to follow to properly write the new content into NVM.

## 1 Features

One of the main advantages in using a NVM solution is the possibility to reconfigure the different parameters, like output voltage, frequency and power-up power-down sequence just to consider the one with the highest impact on device functionality.

The next chapters will describe the single NVM registers and the possible configuration for each of them and the procedure to follow to properly write the desired content into the NVM.

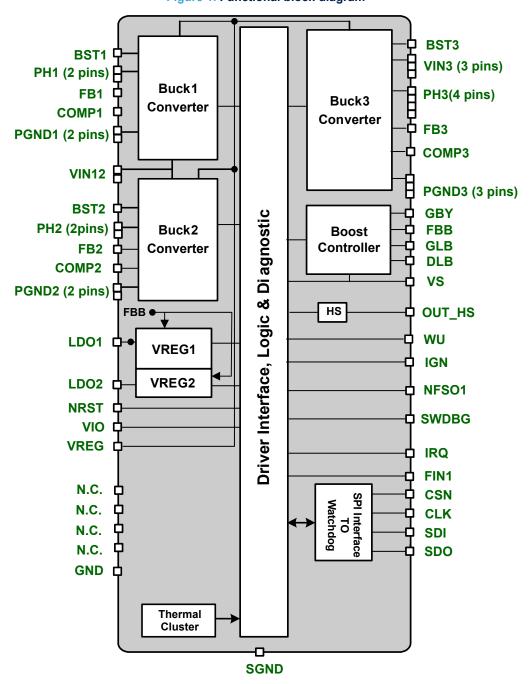

Figure 1. Functional block diagram

AN6052 - Rev 2 page 2/31

## 2 Application use cases for programming

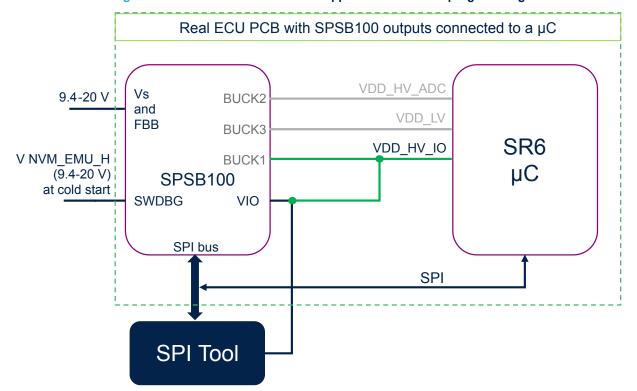

The USER-NVM programming requires the following setup:

- 9.4 20 V power supply at KL30, KL15

- 9.4 20 V signal on SWDBG (see the datasheet specification for allowed voltage range)

- Power supply for VIO (usually taken from SPI HOST side)

- SPI host tool/device

All power outputs of SPSB100 are inactive in programming phase and get active after programming procedure is over and power-up is completed.

Two use cases for USER-NVM programming can be considered.

- · Standalone programming

- In-application programming

Where standalone programming means that there is nothing connected to the SPSB100 power outputs during programming, that is, SPSB100 is programmed, for example, in a dedicated socketed tool.

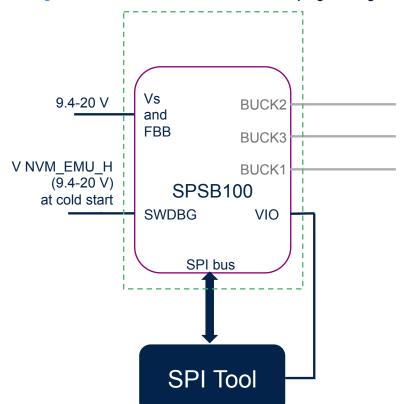

## 2.1 Standalone device programming

Since there is no interference with around parts, standalone device programming does not introduce any specific limitation or "pay attention" points.

Figure 2. Block scheme for device standalone programming

AN6052 - Rev 2 page 3/31

## 2.2 In-application device programming

In principle, there are two possible ways to program SPSB100 in application.

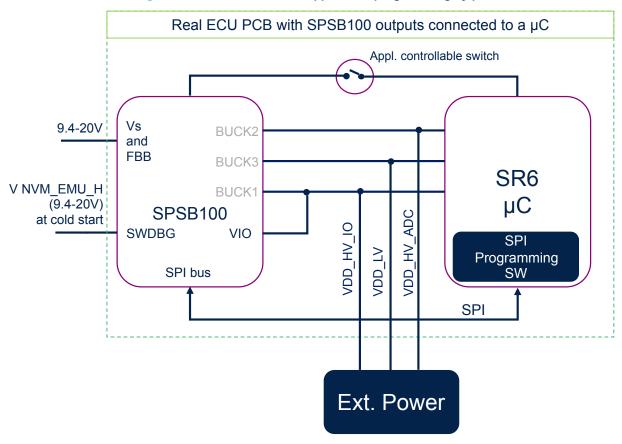

### 2.2.1 By SPI host present in application μC

The main limitation of this way is that there is no power supply for  $\mu C$  present, so

- Power supply needs to be provided externally and

- Programming software needs to be flashed into the uC

Figure 3. Block scheme for in-application programming by  $\mu$ C

Note:

- Picture refers to default configuration of SPSB100 + SR6.

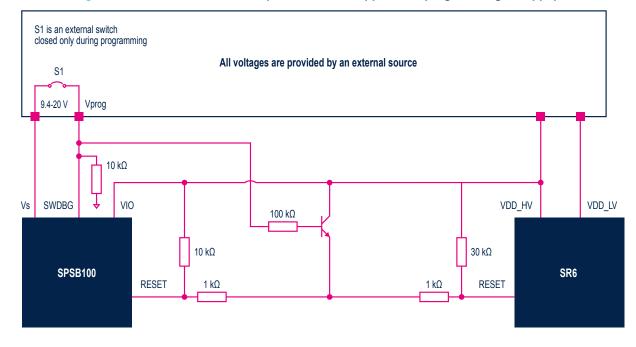

- SPSB100 reset line is held down in SWDBG mode. But μC cannot run any programming code while being under reset. It is needed to implement a hardware solution to disconnect the reset line between SPSB100 and μC during programming. An example of a hardware solution is depicted in the Figure 4.

AN6052 - Rev 2 page 4/31

Figure 4. Hardware solution example to enable in-application programming via app. µC

### 2.2.2 By external SPI tool

Since SPSB100 is connected to  $\mu$ C in real application via SPI, this connection is present also in case the programming shall happen. It implies  $\mu$ C can get powered through internal ESD diodes on SPI IOs. Therefore the VDD\_HV\_IO power rail of  $\mu$ C shall be connected to VIO which eliminates the power injection via ESD diodes. It implies that SPI programming tool IOs should be connected only after VIO supply.

Figure 5. Block scheme for device in-application hardware programming

AN6052 - Rev 2 page 5/31

## 3 NVM configuration

In this chapter the USER-NVM modification procedure is explained.

USER-NVM programmable control registers inside SPSB100 are mapped at SPI address from 0x0Ah to 0x19h. A detailed register description is part of the Section 6: NVM registers DATA field details.

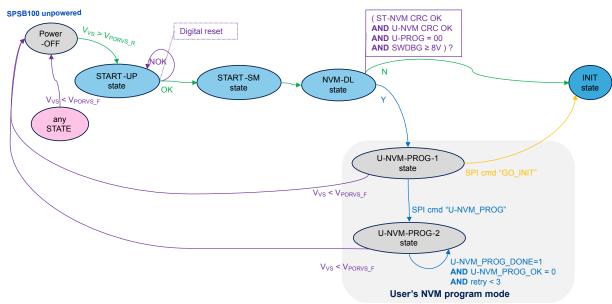

SPSB100 integrates non-volatile memory (NVM) to store ST factory trim data and customer's personalization data. Trim data are stored in ST-NVM space while customer's data are stored in USER-NVM space. The Figure 6 describes the state diagram of the FSM controlling NVM operations.

The following color code is used to indicate the offered possibilities:

- Green: SPSB100 start up with valid data stored in ST-NVM and USER-NVM (USER-NVM previously programmed by ST or by the customer)

- Blue: SPSB100 enters in USER-NVM programming procedure

- Orange: USER-NVM emulation feature is used

Figure 6. NVM configuration state machine

AN6052 - Rev 2 page 6/31

## 3.1 USER-NVM programming procedure

The programming procedure can be done just one time. Once programming is successfully completed, subsequent attempts to program the NVM will be blocked.

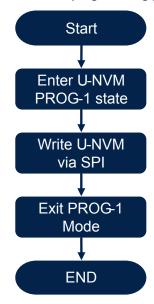

The steps to follow to successfully complete the programming procedure can be divided into 3 macro sections, as reported also in the Figure 7:

- 1. Enter USER-NVM PROG-1 state;

- 2. Modify the USER-NVM content through SPI access;

- 3. Exit the USER-NVM programming mode.

Figure 7. USER-NVM programming procedure

AN6052 - Rev 2 page 7/31

#### 3.1.1 Entering USER-NVM PROG-1 state

The first step is to enter USER-NVM PROG-1.

• Short SWDBG pin to VBAT Provide valid Remove VIO and VBAT VIO voltage Yes Provide VBAT No supply U\_PROG0 = 00b Device cannot U\_PROG1 = 00b be programmed Delay 30 µs Read DSR5 Read DCR17 **DEV STATE** and DCR25 No DEV\_STATE = U-NVM-PROG-1 Yes Release SWDBG pin PROG-1 mode **END**

Figure 8. Enter USER-NVM PROG-1 procedure

Steps to follow to enter USER-NVM PROG-1:

- 1. SWDBG pin forced to a voltage higher than VNVM\_EMU\_H (usually it can be shorted to VBAT but considering the 20 V as max);

- 2. VIO line needs to be supplied externally (regulator outputs are not available);

- 3. Apply 9.4 20 V (voltage should be present at VS and FBB pins);

- 4. SWDBG pin can be released (its value is ignored till the next power-up);

AN6052 - Rev 2 page 8/31

$<sup>^{\</sup>star}$  Add more delay to guarantee minimally 30  $\mu s$  after 9.4 V is present before DSR5 reading.

- 5. As a last step, it is needed to check the device status through the DSR5 reg.

- a. If the status readback is USER-NVM PROG-1, the procedure is correctly completed. Now, the device is prepared to receive USER-NVM content into RAM;

- b. Instead, if the status is different from USER-NVM PROG-1, there are two possibilities:

- i. The procedure to enter USER-NVM PROG-1 is not correct. In such case DCR17 U-PROG0[1:0] and the DCR25 U-PROG1[1:0] fields are '00' (both). It is important to guarantee that the SWDBG pin is at a value higher than VNVM\_EMU\_H (8 V) prior to device logic startup.

Note: Due to excessive capacitive load, even if the SWDBG is shorted to VBAT, it may ramp up too slowly and the result could be not to enter the SWDBG mode. Device logic startup threshold and threshold to enter SWDBG mode are different (SWDBG mode threshold is higher).

ii. The device is already programmed or faulty. In this case, the DCR17 U-PROG0[1:0] and the DCR25 U-PROG1[1:0] (both) fields are different from '00'.

Note:

Be aware that if a device cannot get into the USER-NVM-PROG-1 state and goes into INIT state, it starts up regulators and provides voltages.

AN6052 - Rev 2 page 9/31

#### 3.1.2 Write USER-NVM content

In this step the new USER-NVM configuration is:

- Transferred into RAM

- Written to NVM

The Figure 9 shows the actions to write and check that the NVM was properly written.

Write reg DCRx x=[10:25] Read reg DCRx x=[10:25]Is Read data No content right? Set DCR1 U-NVM PROG bit Read DSR7 register No NVM\_PROG\_DONE Yes Yes No U PROG0 = 00b Device cannot NVM\_PROG\_OK U\_PROG1 = 00b be programmed Yes **NVM END** programmed

Figure 9. Write USER-NVM procedure

Steps to write USER-NVM:

- 1. Write device DCR registers from 10 to 25 through SPI access;

- a. Write '11b' into DCR17 U\_PROG0 and into DCR25 U\_PROG1:

Note: All USER-NVM registers have to be written, even the ones not intended to be modified.

- 2. Read DCR registers to double check the content;

- 3. Set the U-NVM\_PROG bit in DCR1 using SPI access. This starts the USER-NVM programming from RAM. Device changes state into USER-NVM-PROG-2;

- 4. When the USER-NVM programming is completed, the status bit NVM\_PROG\_DONE in DSR7 is set;

AN6052 - Rev 2 page 10/31

Once NVM\_PROG\_DONE is set, read DSR7 NVM\_PROG\_OK to verify that the USER-NVM programming has been completed correctly;

Note:

USER-NVM programming is followed by the USER-NVM verification (self-CRC check).

- 6. In the case NVM\_PROG\_OK is 0, read DCR17 U\_PROG0[1:0] and DCR25 U\_PROG1[1:0]:

- a. If both bitfields are '00', it is necessary to repeat the procedure.

- b. If at least one of the bits is '1', the device is faulty and should not be used.

#### 3.1.3 Exit the USER-NVM programming mode

The last step to complete the USER-NVM modification procedure is to exit from the USER-NVM-PROG-2 mode. In this case, the only option available is to unplug the battery.

#### 3.2 USER-NVM emulation

It is possible to emulate the USER-NVM content using the data stored in RAM image.

This can only be done when the USER-NVM has not been programmed yet.

Steps to follow for NVM emulation:

- Enter programming mode. It is the same procedure as to enter USER-NVM-PROG1 described by the Section 3.1.1: Entering USER-NVM PROG-1 state;

- 2. Write device DCR registers from 10 to 24 through SPI access:

- a. No need to care about DCR17 U\_PROG0 and DCR25 U\_PROG1 fields.

- 3. Read DCR registers to double check the content;

- 4. Write DCR8 GO\_INIT bit to 1 by SPI. The device transits into the INIT state.

The user can emulate the USER-NVM as many times as he wants as far as the USER-NVM is not programmed yet. Once USER-NVM is programmed, it cannot be emulated and the device proceeds with valid data stored in USER-NVM. For default USER-NVM content, see the Section 4: NVM configuration examples.

Note:

The USER-NVM emulated values are lost at chip reset or power supply removal.

AN6052 - Rev 2 page 11/31

## 4 NVM configuration examples

## 4.1 USER-NVM configuration

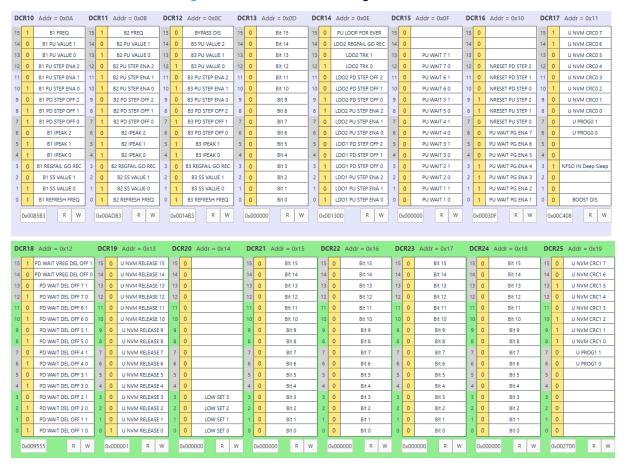

Content of the USER-NVM default configuration:

```

Register = 0x0A, data16 = 0x85B3

Register = 0x0B, data16 = 0xADB3

Register = 0x0C, data16 = 0x14B3

Register = 0x0D, data16 = 0x0000

Register = 0x0E, data16 = 0x130D

Register = 0x0F, data16 = 0x0000

Register = 0x10, data16 = 0x030F

Register = 0x11, data16 = 0xC408

Register = 0x12, data16 = 0x9555

Register = 0x13, data16 = 0x0001

Register = 0x14, data16 = 0x0000

Register = 0x15, data16 = 0x0000

Register = 0x16, data16 = 0x0000

Register = 0x17, data16 = 0x0000

Register = 0x18, data16 = 0x0000

Register = 0x19, data16 = 0x2700

```

Note: Register number and 16 bits data deconstructed from read SPI word.

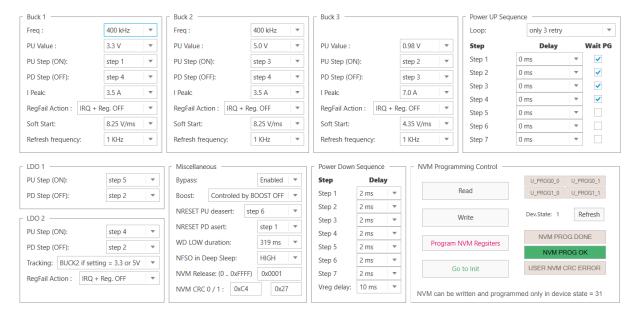

Figure 10. Default USER-NVM registers content

AN6052 - Rev 2 page 12/31

#### Figure 11. Default USER-NVM registers interpretation

AN6052 - Rev 2 page 13/31

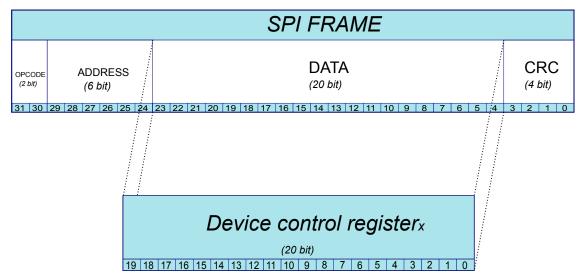

## 5 SPI frame and protocol details

The 32 bits SPI, defined for the device communication, has to be used to manage NVM operations. The 32 bits SPI format is reported in the Figure 12. The frame is divided into 4 different fields:

- OPCODE 2 bits [31:30]

- ADDRESS 6 bits [24:29]

- DATA field 20 bits [23:5], further aim of this field only with re-numbered bits [19:0]

- CRC 4 bits [3:0] This means the bit 4 will be identified as bit 0

Figure 12. SPI frame structure

AN6052 - Rev 2 page 14/31

## 6 NVM registers DATA field details

Write 0 to the "(RESERVED)" and "(NOT USED)" fields.

## 6.1 DCR10 (0X0A)

Table 1. DCR10 DATA field structure

|             |                                  | DCR10                 |                       |             |                                                                          |

|-------------|----------------------------------|-----------------------|-----------------------|-------------|--------------------------------------------------------------------------|

| (RESERVED)  | BUCK1_FREQ<br>BUCK1_PU_VAL<br>UE | BUCK1_PU_STE<br>P_ENA | BUCK1_PD_STE<br>P_OFF | BUCK1_IPEAK | BUCK1_REGFAI<br>L_GO_REC<br>BUCK1_SS_VAL<br>UE<br>BUCK1_REFRES<br>H_FREQ |

| 19 18 17 16 | 15 14 13                         | 12 11 10              | 9 8 7                 | 6 5 4       | 3 2 1 0                                                                  |

#### **BUCK1\_FREQ**

Buck1 switching frequency:

0: 2.4 MHz

1: 0.4 MHz

### BUCK1\_PU\_VALUE [1:0]

Buck1 voltage setting:

00: 3.3 V

01: 5.0 V

1x: 6.5 V

### BUCK1\_PU\_STEP\_ENA [2:0]

Buck1 turn on step:

000: buck is not turned ON

001: step 1

010: step 2

011: step 3

100: step 4

101: step 5

110: step 6

111: step 7

### BUCK1\_PD\_STEP\_OFF [2:0]

Buck1 turn off step:

000: step 1

001: step 2

010: step 3

011: step 4

100: step 5

101: step 6

11x: step 7

## BUCK1\_IPEAK [2:0]

Buck1 peak limitation current:

000: 2.0 Amp

001: 2.5 Amp

010: 3.0 Amp

AN6052 - Rev 2 page 15/31

011: 3.5 Amp

100: 4.0 Amp

101: 4.5 Amp

11x: 5.0 Amp

### BUCK1\_REGFAIL\_GO\_FAIL

Device behavior in case of Buck1 fault:

0: BUCK1 regulator fail generates IRQ (if unmasked) and deactivates regulator (if unmasked)

1: BUCK1 regulator fail initiates a power-down sequence and moves the state machine to REC-2 state

### BUCK1\_SS\_VALUE [1:0]

Buck1 soft start slope setting:

00: 16.5 V/ms 01: 8.25 V/ms 10: 3.3 V/ms 11: 1.65 V/ms

#### **BUCK1\_REFRESH\_FREQ**

Buck1 bootstrap capacitor refresh choice:

1: refresh frequency 1 kHz0: refresh frequency 25 kHz

## 6.2 DCR11 (0X0B)

Table 2. DCR11 DATA field structure

|             |                            | DCR10                 |                       |             |                                                                          |

|-------------|----------------------------|-----------------------|-----------------------|-------------|--------------------------------------------------------------------------|

| (RESERVED)  | BUCK2_FREQ BUCK2_PU_VAL UE | BUCK2_PU_STE<br>P_ENA | BUCK2_PD_STE<br>P_OFF | BUCK2_IPEAK | BUCKZ_REGFAI<br>L_GO_REC<br>BUCKZ_SS_VAL<br>UE<br>BUCKZ_REFRES<br>H_FREQ |

| 19 18 17 16 | 15 14 13                   | 12 11 10              | 9 8 7                 | 6 5 4       | 3 2 1 0                                                                  |

### BUCK2\_FREQ

Buck2 switching frequency:

0: 2.4 MHz 1: 0.4 MHz

#### BUCK2\_PU\_VALUE [1:0]

Buck2 voltage setting:

00: 3.3 V 01: 5.0 V 1x: 6.5 V

#### BUCK2\_PU\_STEP\_ENA [2:0]

Buck2 turn on step:

000: buck is not turned ON

001: step 1 010: step 2 011: step 3 100: step 4 101: step 5 110: step 6

111: step 7

AN6052 - Rev 2 page 16/31

#### BUCK2\_PD\_STEP\_OFF [2:0]

Buck2 turn off step:

000: step 1

001: step 2

010: step 3

011: step 4

100: step 5

101: step 6

11x: step 7

### BUCK2\_IPEAK [2:0]

Buck2 peak limitation current:

000: 2.0 Amp

001: 2.5 Amp

010: 3.0 Amp

011: 3.5 Amp

100: 4.0 Amp

101: 4.5 Amp

11x: 5.0 Amp

### BUCK2\_REGFAIL\_GO\_FAIL

Device behavior in case of Buck2 fault:

0: BUCK2 regulator fail generates IRQ (if unmasked) and deactivates regulator (if unmasked)

1: BUCK2 regulator fail initiates a power-down sequence and moves the state machine to REC-2 state

#### BUCK2\_SS\_VALUE [1:0]

Buck2 soft start slope setting:

00: 16.5 V/ms

01: 8.25 V/ms

10: 3.3 V/ms

11: 1.65 V/ms

### BUCK2\_REFRESH\_FREQ

Buck2 bootstrap capacitor refresh choice:

1: refresh frequency 1 kHz

0: refresh frequency 25 kHz

AN6052 - Rev 2 page 17/31

## 6.3 DCR12 (0X0C)

Table 3. DCR12 DATA field structure

|    |            |    |    |            |              |        |    | DC                    | CR12 |   |                       |   |   |             |   |                          |              |    |                        |

|----|------------|----|----|------------|--------------|--------|----|-----------------------|------|---|-----------------------|---|---|-------------|---|--------------------------|--------------|----|------------------------|

|    | (RESERVED) | j  |    | BYPASS_DIS | BUCK3_PU_VAL | J<br>N |    | BUCK3_PU_STE<br>P_ENA |      |   | BUCK3_PD_STE<br>P_OFF |   |   | BUCK3_IPEAK |   | BUCK3_REGFAI<br>L_GO_REC | BUCK3_SS_VAL | ЭŊ | BUCK3_REFRES<br>H_FREQ |

| 19 | 18         | 17 | 16 | 15         | 14           | 13     | 12 | 11                    | 10   | 9 | 8                     | 7 | 6 | 5           | 4 | 3                        | 2            | 1  | 0                      |

### BYPASS\_DIS

Boost bypass option:

1: Disabled-Bypass disable

0: Enabled–Bypass enable (will be ON or OFF based on the sensed value on the VS pin)

#### BUCK3\_PU\_VALUE [2:0]

Buck3 voltage setting:

001: 0.98 V

010: 1.1 V

011: 1.2 V

100: 1.25 V

101: 3.3 V

11x: 6.5 V

#### BUCK3\_PU\_STEP\_ENA [2:0]

Buck3 turn on step:

000: buck is not turned ON

001: step 1

010: step 2

011: step 3

100: step 4

101: step 5

110: step 6

111: step 7

#### BUCK3\_PD\_STEP\_OFF [2:0]

Buck3 turn off step:

000: step 1

001: step 2

010: step 3

011: step 4

100: step 5

101: step 6

11x: step 7

#### BUCK3\_IPEAK [2:0]

Buck3 peak limitation current:

00: 4.0 Amp

01: 5.0 Amp

10: 6.0 Amp

11: 7.0 Amp

AN6052 - Rev 2 page 18/31

#### BUCK3\_REGFAIL\_GO\_FAIL

Device behavior in case of Buck3 fault:

0: BUCK3 regulator fail generates IRQ (if unmasked) and deactivates regulator (if unmasked)

1: BUCK3 regulator fail initiates a power-down sequence and moves the state machine to REC-2 state

#### BUCK3\_SS\_VALUE [1:0]

Buck3 soft start slope setting:

00: 8.7 V/ms

01: 4.35 V/ms

10: 1.75 V/ms

11: 0.87 V/ms

#### BUCK3\_REFRESH\_FREQ

Buck3 bootstrap capacitor refresh choice:

1: refresh frequency 1 kHz

0: refresh frequency 25 kHz

## 6.4 DCR13 (0X0D), DCR21-24 (0x15-0x18)

Table 4. DCR13, DCR21-24 DATA field structure

|    |    |    |    |    |    |    | DCR1  | 3, DCF   | R21-24   |     |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|----|-------|----------|----------|-----|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    | NC | T USE | D – writ | te 0x000 | 000 |   |   |   |   |   |   |   |   |   |

| 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12    | 11       | 10       | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

## 6.5 DCR14 (0X0E)

Table 5. DCR14 DATA field structure

|    |             |    |    |             |                         |         |        | DC | CR14                 |   |   |                      |   |   |                  |   |   |                      |   |

|----|-------------|----|----|-------------|-------------------------|---------|--------|----|----------------------|---|---|----------------------|---|---|------------------|---|---|----------------------|---|

|    | (OESTED/CE) |    |    | PU_LOOP_EVE | LDO2_REGFAIL_<br>GO_REC | YGT COU | ב<br>ו |    | LDO2_PD_STEP<br>_OFF |   |   | LDO2_PU_STEP<br>_ENA |   |   | LDO1_PD_STEP_OFF |   |   | LDO1_PU_STEP<br>_ENA |   |

| 19 | 18          | 17 | 16 | 15          | 14                      | 13      | 12     | 11 | 10                   | 9 | 8 | 7                    | 6 | 5 | 4                | 3 | 2 | 1                    | 0 |

## LDO2\_REGFAIL\_GO\_FAIL

Device behavior in case of LDO2 fault:

0: LDO2 regulator fail generates IRQ (if unmasked) and deactivates regulator (if unmasked)

1: LDO2 regulator fail initiates a power-down sequence and moves the state machine to REC-2 state

#### LDO2\_TRK [1:0]

LDO2 tracked voltage setting:

00: BUCK1 (only if BUCK1 output voltage is 3.3 V or 5 V otherwise LDO2 OFF)

01: BUCK2 (only if BUCK2 output voltage is 3.3 V or 5 V otherwise LDO2 OFF)

1x: BUCK3 (only if BUCK3 output voltage is 3.3 V otherwise LDO2 OFF)

## LDO2\_PD\_STEP\_OFF [2:0]

LDO2 turn off step:

000: step 1 001: step 2 010: step 3 011: step 4

AN6052 - Rev 2 page 19/31

100: step 5

101: step 6

11X: step 7

## LDO2\_PU\_STEP\_ENA [2:0]

LDO2 turn on step:

000: LDO is not turned ON

001: step 1

010: step 2

011: step 3

100: step 4

101: step 5

110: step 6

111: step 7

## LDO1\_PD\_STEP\_OFF [2:0]

LDO1 turn off step:

000: step 1

001: step 2

010: step 3

011: step 4

100: step 5

101: step 6

11x: step 7

## LDO1\_PU\_STEP\_ENA [2:0]

LDO1 turn on step:

000: LDO is not turned ON

001: step 1

010: step 2

011: step 3

100: step 4

101: step 5

110: step 6

111: step 7

AN6052 - Rev 2 page 20/31

## 6.6 DCR15 (0X0F)

Table 6. DCR15 DATA field structure

|             |                               | DCR15                                          |                                                |                                                |

|-------------|-------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| (RESERVED)  | (NOT USED) PU_WAIT_DEL_ ENA_7 | PU_WAIT_DEL_<br>ENA_6<br>PU_WAIT_DEL_<br>ENA_5 | PU_WAIT_DEL_<br>ENA_4<br>PU_WAIT_DEL_<br>ENA_3 | PU_WAIT_DEL_<br>ENA_2<br>PU_WAIT_DEL_<br>ENA_1 |

| 19 18 17 16 | 15 14 13 12                   | 11 10 9 8                                      | 7 6 5 4                                        | 3 2 1 0                                        |

### PU\_WAIT\_DEL\_ENA\_7 [1:0]

Power up delay at step 7:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

#### PU\_WAIT\_DEL\_ENA\_6 [1:0]

Power up delay at step 6:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

#### PU\_WAIT\_DEL\_ENA\_5 [1:0]

Power up delay at step 5:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_ENA\_4 [1:0]

Power up delay at step 4:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_ENA\_3 [1:0]

Power up delay at step 3:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_ENA\_2 [1:0]

Power up delay at step 2:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

AN6052 - Rev 2 page 21/31

#### PU\_WAIT\_DEL\_ENA\_1 [1:0]

Power up delay at step 1:

00: 0 ms 01: 2 ms 10: 5 ms 11: 10 ms

## 6.7 DCR16 (0X10)

Table 7. DCR16 DATA field structure

|    |              |    |    |    |            |    |    | DC                        | CR16 |   |                             |   |                      |                      |              |                      |                      |                      |                      |

|----|--------------|----|----|----|------------|----|----|---------------------------|------|---|-----------------------------|---|----------------------|----------------------|--------------|----------------------|----------------------|----------------------|----------------------|

|    | (DESERBY/FD) | >  |    |    | (NOT USED) |    |    | NRESET_PD_ST<br>EP_ASSERT |      |   | NRESET_PU_ST<br>EP_DEASSERT |   | PU_WAIT_PG_E<br>NA_7 | PU_WAIT_PG_E<br>NA_6 | PU_WAIT_PG_E | PU_WAIT_PG_E<br>NA 4 | PU_WAIT_PG_E<br>NA 3 | PU_WAIT_PG_E<br>NA 2 | PU_WAIT_PG_E<br>NA_1 |

| 19 | 18           | 17 | 16 | 15 | 14         | 13 | 12 | 11                        | 10   | 9 | 8                           | 7 | 6                    | 5                    | 4            | 3                    | 2                    | 1                    | 0                    |

#### NRESET\_PD\_STEP\_ASSERT [2:0]

To define NRESET assertion steps:

000: step 1 001: step 2

010: step 3

011: step 4

100: step 5

101: step 6

11x: step 7

## NRESET\_PU\_STEP\_DEASSERT [2:0]

To define NRESET de-assertion and WD start step:

000: end of step 7

001: step 1

010: step 2

011: step 3

100: step 4

101: step 5

110: step 6

111: step 7

### PU\_WAIT\_PG\_ENA\_7

Power-good signal choice:

1: at power-up step 7 wait for power-good signal

0: at power-up step 7 does not wait for power-good signal

#### PU\_WAIT\_PG\_ENA\_6

Power-good signal choice:

1: at power-up step 6 wait for power-good signal

0: at power-up step 6 does not wait for power-good signal

#### PU\_WAIT\_PG\_ENA\_5

Power-good signal choice:

1: at power-up step 5 wait for power-good signal

0: at power-up step 5 does not wait for power-good signal

AN6052 - Rev 2 page 22/31

#### PU\_WAIT\_PG\_ENA\_4

Power-good signal choice:

1: at power-up step 4 wait for power-good signal

0: at power-up step 4 does not wait for power-good signal

#### PU\_WAIT\_PG\_ENA\_3

Power-good signal choice:

1: at power-up step 3 wait for power-good signal

0: at power-up step 3 does not wait for power-good signal

#### PU\_WAIT\_PG\_ENA\_2

Power-good signal choice:

1: at power-up step 2 wait for power-good signal

0: at power-up step 2 does not wait for power-good signal

#### PU\_WAIT\_PG\_ENA\_1

Power-good signal choice:

1: at power-up step 1 wait for power-good signal

0: at power-up step 1 does not wait for power-good signal

## 6.8 DCR17 (0X11)

Table 8. DCR17 DATA field structure

|    |                                                                                                                     |            |    |    |    |    |            | DC | CR17 |   |   |   |         |     |   |                               |   |        |           |

|----|---------------------------------------------------------------------------------------------------------------------|------------|----|----|----|----|------------|----|------|---|---|---|---------|-----|---|-------------------------------|---|--------|-----------|

|    | ָרָרָ אָרָרָרָיִיּרָ אָרָרָרָיִיּרָ אָרָרָרָיִיּרָ אָרָרָיִיּרָיִייִּרְיִיּרָיִיִּרְיִייִּרְיִיּרְיִיִּרְיִיִּרְיִי | (RESERVED) |    |    |    |    | U_NVM_CRC0 |    |      |   |   |   | 05087_0 | HON | _ | NFSO_STATE_IN_<br>_DEEP_SLEEP | H | <br> - | BOOST_DIS |

| 19 | 18                                                                                                                  | 17         | 16 | 15 | 14 | 13 | 12         | 11 | 10   | 9 | 8 | 7 | 6       | 5   | 4 | 3                             | 2 | 1      | 0         |

#### U\_NVM\_CRC0 [7:0]

Control CRC

Note:

Written by SPSB100. Content is ignored during writing done by the user.

#### U\_PROG0 [1:0]

Confirmation user NVM has been programmed:

00: not programmed

11: already programmed

#### NFSO\_STATE\_IN\_DEEP\_SLEEP

NFSO option:

1: NFSO pin is high when FSM in DEEP\_SLEEP state

0: NFSO pin is low when FSM in DEEP\_SLEEP state

#### BOOST\_DIS

Boost option:

1: Disabled-boost function is not used

0: Enabled-boost function is used and depends on BOOST\_OFF control bit

AN6052 - Rev 2 page 23/31

## 6.9 DCR18 (0X12)

Table 9. DCR18 DATA field structure

|    |          |    |    |              |          |              |       | DC          | CR18    |              |       |              |       |              |        |              |       |              |       |

|----|----------|----|----|--------------|----------|--------------|-------|-------------|---------|--------------|-------|--------------|-------|--------------|--------|--------------|-------|--------------|-------|

|    | <u>.</u> |    |    | PD_WAIT_VREG | _DEL_OFF | PD_WAIT_DEL_ | OFF_7 | PD WAIT DEL | _ OFF_6 | PD_WAIT_DEL_ | OFF_5 | PD_WAIT_DEL_ | OFF_4 | PD_WAIT_DEL_ | _OFF_3 | PD_WAIT_DEL_ | OFF_2 | PD_WAIT_DEL_ | OFF_1 |

| 19 | 18       | 17 | 16 | 15           | 14       | 13           | 12    | 11          | 10      | 9            | 8     | 7            | 6     | 5            | 4      | 3            | 2     | 1            | 0     |

### PD\_WAIT\_VREG\_DEL\_OFF [1:0]

Power down delay for Vreg:

00: 2 ms

01: 5 ms

10: 10 ms

11: 20 ms

#### PU\_WAIT\_DEL\_OFF\_7 [1:0]

Power down delay at step 7:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

#### PU\_WAIT\_DEL\_OFF\_6 [1:0]

Power down delay at step 6:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_OFF\_5 [1:0]

Power down delay at step 5:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_OFF\_4 [1:0]

Power down delay at step 4:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## PU\_WAIT\_DEL\_OFF\_3 [1:0]

Power down delay at step 3:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

AN6052 - Rev 2 page 24/31

### PU\_WAIT\_DEL\_OFF\_2 [1:0]

Power down delay at step 2:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

#### PU\_WAIT\_DEL\_OFF\_1 [1:0]

Power down delay at step 1:

00: 0 ms

01: 2 ms

10: 5 ms

11: 10 ms

## 6.10 DCR19 (0X13)

#### Table 10. DCR19 DATA field structure

|    |                          |       |    |    |    |    |     | DCR19   | )          |         |      |      |        |       |   |   |   |   |   |

|----|--------------------------|-------|----|----|----|----|-----|---------|------------|---------|------|------|--------|-------|---|---|---|---|---|

|    | (RESERVED) U_NVM_RELEASE |       |    |    |    |    |     |         |            |         |      |      |        |       |   |   |   |   |   |

|    | (KESE                    | KVED) |    |    |    |    | (16 | bit ide | ntificatio | on of l | JSEF | _NVI | M rele | ease) |   |   |   |   |   |

| 19 | 18                       | 17    | 16 | 15 | 14 | 13 | 12  | 11      | 10         | 9       | 8    | 7    | 6      | 5     | 4 | 3 | 2 | 1 | 0 |

## 6.11 DCR20 (0X14)

Table 11. DCR20 DATA field structure

|   |   |       |       |    |    |    |    |    | DCR2 | )     |   |   |   |   |   |   |   |     |     |   |

|---|---|-------|-------|----|----|----|----|----|------|-------|---|---|---|---|---|---|---|-----|-----|---|

|   |   | (RESE | RVED) |    |    |    |    |    | (NOT | USED) | ) |   |   |   |   |   |   | LOW | SET |   |

| 1 | 9 | 18    | 17    | 16 | 15 | 14 | 13 | 12 | 11   | 10    | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0 |

### LOW\_SET [3:0]

Long open window setting

0000: 319 ms max.

0001: 479 ms max.

0010: 638 ms max.

0011: 1025 ms max.

0100: 115 ms max.

0101: 159 ms max.

0110: 230 ms max.

0111: 460 ms max.

1000-1011: 2300 ms max.

1100: 4600 ms max.

1101: 6900 ms max.

1110: 9200 ms max.

1111: infinite

AN6052 - Rev 2 page 25/31

## 6.12 DCR25 (0X19)

Table 12. DCR25 DATA field structure

|    |                                          |    |    |    |    |    |    | D  | CR25 |   |   |   |   |   |   |   |   |   |   |

|----|------------------------------------------|----|----|----|----|----|----|----|------|---|---|---|---|---|---|---|---|---|---|

|    | (RESERVED) U_NVM_CRC1 U_PROG1 (NOT USED) |    |    |    |    |    |    |    |      |   |   |   |   |   |   |   |   |   |   |

| 19 | 18                                       | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

U\_NVM\_CRC1 [7:0]

Control CRC

Note: Written by SPSB100. Content is ignored during writing done by the user.

U\_PROG1 [1:0]

Confirmation user NVM has been programmed:

00: not programmed11: already programmed

AN6052 - Rev 2 page 26/31

## **Revision history**

Table 13. Document revision history

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                 |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Feb-2024 | 1       | Initial release.                                                                                                                                                                                                                                                                                        |

| 12-Jul-2024 | 2       | Updated Figure 1. Functional block diagram, Figure 10. Default USER-NVM registers content, Figure 11. Default USER-NVM registers interpretation and Section 6.8: DCR17 (0X11).  Removed section "Recommended configuration (BA silicon)" and "Write example of recommended configuration (BA silicon)". |

AN6052 - Rev 2 page 27/31

## **Contents**

| 1   | Feat  | ures     |                                       | 2  |

|-----|-------|----------|---------------------------------------|----|

| 2   | Appl  | lication | use cases for programming             | 3  |

|     | 2.1   | Stand    | alone device programming              | 3  |

|     | 2.2   | In-app   | olication device programming          | 4  |

|     |       | 2.2.1    | By SPI host present in application μC | 4  |

|     |       | 2.2.2    | By external SPI tool                  | 5  |

| 3   | NVM   | config   | guration                              | 6  |

|     | 3.1   | USER     | R-NVM programming procedure           | 7  |

|     |       | 3.1.1    | Entering USER-NVM PROG-1 state        | 8  |

|     |       | 3.1.2    | Write USER-NVM content                | 10 |

|     |       | 3.1.3    | Exit the USER-NVM programming mode    | 11 |

|     | 3.2   | USER     | R-NVM emulation                       | 11 |

| 4   | NVM   | config   | guration examples                     | 12 |

|     | 4.1   | USER     | R-NVM configuration                   | 12 |

| 5   | SPI 1 | frame a  | and protocol details                  | 14 |

| 6   | NVM   | l regist | ers DATA field details                | 15 |

|     | 6.1   | DCR1     | 0 (0X0A)                              | 15 |

|     | 6.2   | DCR1     | 1 (0X0B)                              | 16 |

|     | 6.3   | DCR1     | 2 (0X0C)                              | 18 |

|     | 6.4   | DCR1     | 3 (0X0D), DCR21-24 (0x15-0x18)        | 19 |

|     | 6.5   | DCR1     | 4 (0X0E)                              | 19 |

|     | 6.6   | DCR1     | 5 (0X0F)                              | 21 |

|     | 6.7   | DCR1     | 6 (0X10)                              | 22 |

|     | 6.8   | DCR1     | 7 (0X11)                              | 23 |

|     | 6.9   | DCR1     | 8 (0X12)                              | 24 |

|     | 6.10  | DCR1     | 9 (0X13)                              | 25 |

|     | 6.11  |          | 20 (0X14)                             |    |

|     | 6.12  |          | 25 (0X19)                             |    |

| Rev | ision |          | /                                     |    |

## List of tables

| Table 1.  | DCR10 DATA field structure           |    |

|-----------|--------------------------------------|----|

| Table 2.  | DCR11 DATA field structure           |    |

| Table 3.  | DCR12 DATA field structure           |    |

| Table 4.  | DCR13, DCR21-24 DATA field structure |    |

| Table 5.  | DCR14 DATA field structure           |    |

| Table 6.  | DCR15 DATA field structure           |    |

| Table 7.  | DCR16 DATA field structure           |    |

| Table 8.  | DCR17 DATA field structure           |    |

| Table 9.  | DCR18 DATA field structure           |    |

|           | DCR19 DATA field structure           |    |

|           | DCR20 DATA field structure           |    |

| Table 12. | DCR25 DATA field structure           | 26 |

| Table 13. | Document revision history            | 27 |

# **List of figures**

| Figure 1.  | Functional block diagram                                                   | 2  |

|------------|----------------------------------------------------------------------------|----|

| Figure 2.  | Block scheme for device standalone programming                             | 3  |

| Figure 3.  | Block scheme for in-application programming by $\mu C$                     | 4  |

| Figure 4.  | Hardware solution example to enable in-application programming via app. μC | 5  |

| Figure 5.  | Block scheme for device in-application hardware programming                | 5  |

| Figure 6.  | NVM configuration state machine                                            | 6  |

| Figure 7.  | USER-NVM programming procedure                                             | 7  |

| Figure 8.  | Enter USER-NVM PROG-1 procedure                                            | 8  |

| Figure 9.  | Write USER-NVM procedure                                                   | 10 |

| Figure 10. | Default USER-NVM registers content                                         | 12 |

| Figure 11. | Default USER-NVM registers interpretation                                  | 13 |

| Figure 12. | SPI frame structure                                                        | 14 |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

AN6052 - Rev 2 page 31/31