### STSAFE-TPM trusted platform module 2.0 with a SPI interface

UFQFPN32 (5 × 5 × 0.55 mm)

#### **Features**

#### **TPM** features

- Flash-memory-based trusted platform module (TPM)

- Compliant with Trusted Computing Group (TCG) trusted platform module (TPM)

Library specifications 2.0, revision 1.59 errata version 1.4 and TCG PC Client

Platform TPM Profile (PTP) for TPM 2.0 Version 1.05

- Fault-tolerant firmware loader that keeps the *TPM* fully functional when the loading process is interrupted (self-recovery)

- SP800-193 compliant for protection, detection and recovery requirements

- Targeted certifications:

- Common Criteria EAL4+ in compliance with the TPM 2.0 protection profile (augmented with AVA\_VAN.5, resistant to high-potential attacks)

- FIPS 140-3

- TCG certification

- SPI communication bus running at up to 66 MHz

#### **Hardware features**

- Highly reliable flash memory with error correction code

- Extended temperature range: -40 °C to 105 °C

- Electrostatic discharge (ESD) protection up to 4 kV (HBM)

- 1.8 V or 3.3 V supply voltage range

#### Product status link

ST33KTPM2XSPI

#### Security features

- Active shield

- Monitoring of environmental parameters

- Hardware and software protection against fault injection and side channel attacks

- FIPS SP800-90A and AIS20-compliant deterministic random-bit generator (DRBG)

- FIPS SP800-90B and AIS31-compliant true random-number generator (TRNG)

- · Cryptographic algorithms:

- RSA key generation (1024, 2048, 3072 and 4096 bits)

- RSA signature (RSASSA-PSS, RSASSA-PKCS1v1\_5)

- RSA encryption (RSAES-OAEP, RSAESPKCS1-v1\_5)

- SHA-1, SHA-2 (256 and 384 bits), SHA-3 (256 and 384 bits)

- HMAC SHA-1, SHA-2 and SHA-3

- AES-128,192 and 256 bits

- ECC (NIST P-256, P-384 curves): key generation, ECDH and ECDSA, ECSchnorr

- ECDAA (BN-256 curve)

- Device provided with 3 endorsement keys (EK) and EK certificates (RSA2048, ECC NIST P\_256 and ECC NIST P\_384)

Device provisioned with three 2048-bit RSA key pairs to reduce the TPM provisioning time

#### Product's targeted compliance

- Compliant with Microsoft ® Windows® 10 and 11

- Compliant with Linux<sup>®</sup> drivers

- Compliant with Intel® vPro® technology

- Compliant with TCG test suite for TPM 2.0

- Compliant with the open-source TCG TPM 2.0 TSS implementation

DB4737 - Rev 3 page 2/22

### 1 Description

The STSAFE-TPM (trusted platform module) family of products offers a broad portfolio of standardized solutions for embedded, PC, mobile, and computing applications.

It includes turnkey products compliant with the Trusted Computing Group (TCG) standards that provide services to protect the confidentiality, integrity, and authenticity of information and devices.

The STSAFE-TPM devices are easy to integrate thanks to the variety of supported interfaces and the availability of TPM ecosystem software solutions.

The STSAFE-TPM devices target Common Criteria, TCG, and FIPS certification.

The ST33KTPM2XSPI offers a slave serial peripheral interface (SPI) compliant with the TCG PC Client TPM Profile specifications.

It offers resilience services during the TPM firmware upgrade process, and self-recovery of TPM firmware and critical data upon failure detection.

The ST33KTPM2XSPI device operates in the -40 °C to 105 °C extended temperature range.

The device is offered in the UFQFPN32 ECOPACK2 package. ECOPACK is an ST trademark.

DB4737 - Rev 3 page 3/22

# 2 UFQFPN32 pin and signal description

The figure below gives the pinout of the UFQFPN32 package in which the devices are delivered. The table describes the associated signals.

32 31 30 29 28 27 26 25 VPS 1 24 SPI\_MISO GND 2 23 NiC NiC 3 22 VPS UFQFPN32 NiC 4 21 SPI\_MOSI NiC 33 NiC 5 20 SPI\_CS NC 6 SPI\_CLK 19 GPIO\_PP 7 **PIRQ** 18 NiC 8 17 RST 9 10 11 12 13 14 15 16

Figure 1. UFQFPN32 pinout

Table 1. Pin descriptions

| Signal            | Туре         | Description                                                                                                                                                                                                      |

|-------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPS               | Input        | <b>Power supply</b> . This pin must be connected to 1.8 V or 3.3 V DC power rail supplied by the motherboard.                                                                                                    |

| GND               | Input        | Ground, has to be connected to the main motherboard ground.                                                                                                                                                      |

| RST               | Input        | <b>Reset</b> , active low, used to re-initialize the device. Must not be unconnected. External pull-up resistor required if it cannot be driven.                                                                 |

| SPI_MISO          | Output       | SPI Master Input, Slave Output (output from slave)                                                                                                                                                               |

| SPI_MOSI          | Input        | SPI Master Output, Slave Input (output from master)                                                                                                                                                              |

| SPI_CLK           | Input        | SPI Serial Clock (output from master)                                                                                                                                                                            |

| SPI_CS            | Input        | SPI Chip (or Slave) Select, internal pull-up (active low; output from master)                                                                                                                                    |

| PIRQ              | Output       | IRQ, active low, open drain, used by the TPM to generate an interrupt                                                                                                                                            |

| GPIO_PP           | Input        | <b>Physical Presence</b> , active high, internal pull-down. Used to indicate Physical Presence to the TPM. The GPIO function could be modified by activating the GPIOs mapped with the NV storage index feature. |

| NiC               | -            | <b>Not internally connected</b> : not connected to the die. May be left unconnected but no impact on TPM if connected.                                                                                           |

| NC                | -            | Not connected: connected to the die but unused. Must be left unconnected.                                                                                                                                        |

| GPIO_5 and GPIO_6 | Input/Output | The GPIO function could be modified by activating the GPIOs mapped with the NV storage index feature.                                                                                                            |

Note:

The UFQFPN32 package has a central pad (PIN33) on the bottom, which is not connected to the die. This pin does not impact the TPM, be it connected or not.

DB4737 - Rev 3 page 4/22

# 3 Electrical integration guidance

This section gives some guidance on how to integrate the ST33KTPM2XSPI device in an application.

#### 3.1 Recommended power supply filtering

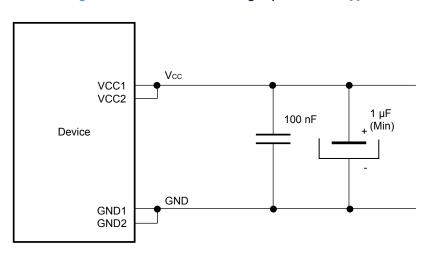

The power supply of the device should be filtered using the circuit shown in the figure below.

Figure 2. Recommended filtering capacitors on V<sub>CC</sub>

F64224V1

Table 2. V<sub>CC</sub> rising slope

Data based on design simulation and/or characterization results, not tested in production.

| Symbol           | Parameter                    | Min. | Тур. | Max.                | Unit |

|------------------|------------------------------|------|------|---------------------|------|

| S <sub>VCC</sub> | V <sub>CC</sub> rising slope | 2    | -    | 2 · 10 <sup>3</sup> | V/ms |

Note:

Measurement must be done between 1.36 V and 1.62 V. If  $V_{CC}$  rising slope requirement is unreachable for the concerned platform or if there is any other noisy environment at boot, a "power-on reset and warm reset sequence" must be run.

### 3.2 SPI\_CS optional filtering

Recommendation for SPI\_CS integration: It is mandatory that SPI\_CLK is at the low logic level when the falling edge occurs on the SPI\_CS signal. An external capacitance of 56 pF is recommended on SPI\_CS for that purpose. This capacitor might not be required depending on the intrinsic line capacitance, the SPI bus frequency, or both.

DB4737 - Rev 3 page 5/22

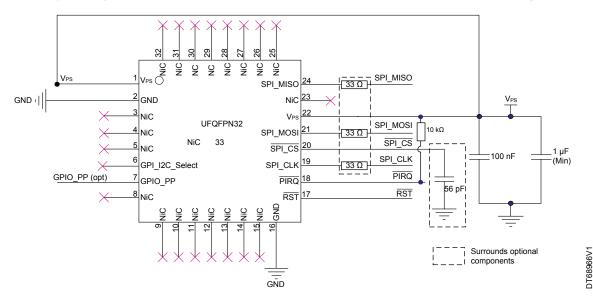

#### 3.3 Device integration for SPI communication

The figure below shows the typical hardware implementation of the ST33KTPM2XSPI device for *SPI* communication.

Figure 3. Typical hardware implementation for SPI communication (UFQFPN32 package)

Note: The use of a low-value resistor (typically 33  $\Omega$ ) on SPI\_MISO, SPI\_MOSI and SPI\_CLK can be recommended for line adaptation when the signals are affected by parasite spikes. Its use is mandatory to avoid disturbance of the ramp-up and ramp-down signals.

Note: The capacitor on SPI\_CS is optional (see Section 3.2 SPI\_CS optional filtering).

Note: The pull-up resistor on the PIRQ line is mandatory to optimize the power consumption in standby mode.

DB4737 - Rev 3 page 6/22

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

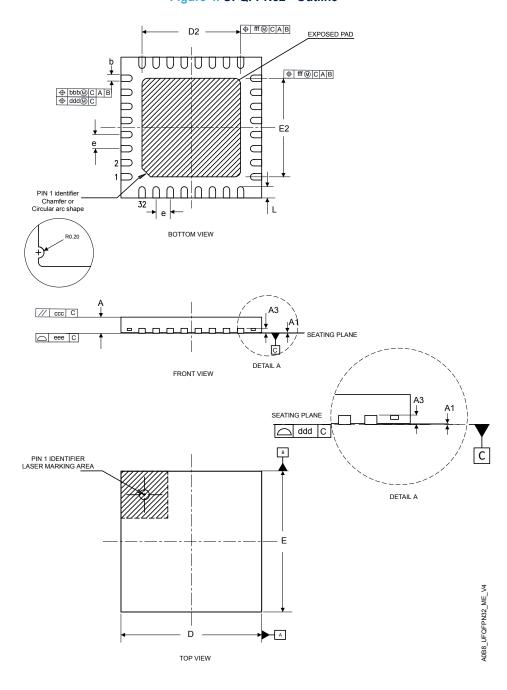

### 4.1 UFQFPN32 package information

This UFQFPN is a 32 pins, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package.

Figure 4. UFQFPN32 - Outline

DB4737 - Rev 3 page 7/22

- 1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this backside pad to PCB ground.

Table 3. UFQFPN32 - Mechanical data

| Cumbal                   |                     | millimeters(1) |      |            | inches <sup>(2)</sup> |        |  |

|--------------------------|---------------------|----------------|------|------------|-----------------------|--------|--|

| Symbol                   | Min                 | Тур            | Max  | Min        | Тур                   | Max    |  |

| A <sup>(3)(4)</sup>      | 0.50                | 0.55           | 0.60 | 0.0197     | 0.0217                | 0.0236 |  |

| A1 <sup>(5)</sup>        | 0.00                | -              | 0.05 | 0.000      | -                     | 0.0020 |  |

| A3 <sup>(6)</sup>        | -                   | 0.15           | -    | -          | 0.0060                | -      |  |

| b <sup>(7)</sup>         | 0.18                | 0.25           | 0.30 | 0.0071     | 0.010                 | 0.0118 |  |

| D <sub>(8)(9)</sub>      |                     | 5.00 BSC       |      | 0.1969 BSC |                       |        |  |

| D2                       | 3.50                | 3.60           | 3.70 | 0.139      | 0.143                 | 0.147  |  |

| E(8)(9)                  | 5.00 BSC 0.1969 BSC |                |      |            |                       |        |  |

| E2                       | 3.50                | 3.60           | 3.70 | 0.139      | 0.143                 | 0.147  |  |

| <b>e</b> <sup>(9)</sup>  | -                   | 0.50           | -    | -          | 0.02                  | -      |  |

| <b>N</b> <sup>(10)</sup> |                     |                |      | 32         |                       |        |  |

| K                        | 0.15                | -              | -    | 0.006      | -                     | -      |  |

| L                        | 0.30                | -              | 0.50 | 0.0119     | -                     | 0.0199 |  |

| R                        | 0.09                | -              | -    | 0.004      | -                     | -      |  |

- All dimensions are in millimetres. Dimensioning and tolerancing schemes are conform to ASME Y14.5M-2018 except European.

- 2. Values in inches are converted from mm and rounded to 4 decimal digits.

- 3. UFQFPN stands for Ultra thin Fine pitch Quad Flat Package No lead:  $A \le 0.60mm$  / Fine pitch  $e \le 1.00mm$ .

- 4. The profile height, A, is the distance from the seating plane to the highest point on the package. It is measured perpendicular to the seating plane.

- 5. A1 is the vertical distance from the bottom surface of the plastic body to the nearest metallized package feature.

- 6. A3 is the distance from the seating plane to the upper surface of the terminals.

- 7. Dimension b applies to metallized terminal. If the terminal has the optional radius on the other end of the terminal, the dimension b must not be measured in that radius area.

- 8. Dimensions D and E do not include mold protrusion, not to exceed 0,15mm.

- 9. BSC stands for BASIC dimensions. It corresponds to the nominal value and has no tolerance. For tolerances refer to Table 4

- 10. N represents the total number of terminals.

Table 4. Tolerance of form and position

| Symbol <sup>(1)</sup> | Tolerance of form and position <sup>(2)</sup> In millimeters | Tolerance of form and position <sup>(3)</sup><br>In inches |

|-----------------------|--------------------------------------------------------------|------------------------------------------------------------|

| aaa                   | 0.15                                                         | 0.006                                                      |

| bbb                   | 0.10                                                         | 0.004                                                      |

| ccc                   | 0.10                                                         | 0.004                                                      |

| ddd                   | 0.05                                                         | 0.002                                                      |

| eee                   | 0.10                                                         | 0.004                                                      |

| fff                   | 0.10                                                         | 0.004                                                      |

DB4737 - Rev 3 page 8/22

- 1. For the tolerance of form and position definitions see Table 5.

- All dimensions are in millimetres. Dimensioning and tolerancing schemes are conform to ASME Y14.5M-2018 except European.

- 3. Values in inches are converted from mm and rounded to 4 decimal digits.

Table 5. Tolerance of form and position symbol definition

| Symbol | Definition                                                                                                                                                                                                 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aaa    | The bilateral profile tolerance that controls the position of the plastic body sides. The centres of the profile zones are defined by the basic dimensions D and E.                                        |

| bbb    | The tolerance that controls the position of the terminals with respect to Datums A and B. The centre of the tolerance zone for each terminal is defined by basic dimension e as related to datums A and B. |

| ccc    | The tolerance located parallel to the seating plane in which the top surface of the package must be located.                                                                                               |

| ddd    | The tolerance that controls the position of the terminals to each other. The centres of the profile zones are defined by basic dimension e.                                                                |

| eee    | The unilateral tolerance located above the seating plane wherein the bottom surface of all terminals must be located = coplanarity                                                                         |

| fff    | The tolerance that controls the position of the exposed metal heat feature. The centre of the tolerance zone is the data defined by the centrelines of the package body                                    |

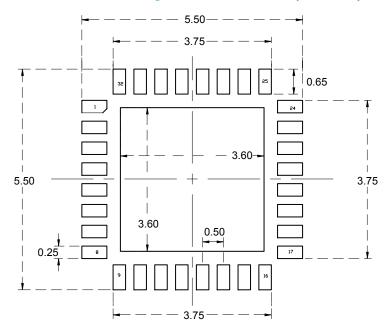

Figure 5. UFQFPN32 - Footprint example

Dimensions are expressed in millimeters.

A0B8\_UFQFPN32\_FP\_V1

DB4737 - Rev 3

page 9/22

# 4.2 Thermal characteristics of packages

The table below provides the thermal characteristics of the UFQFPN32 package.

**Table 6. Thermal characteristics**

| Parame                                  | Symbol                                 | Value                          |               |

|-----------------------------------------|----------------------------------------|--------------------------------|---------------|

|                                         | Ambient temperature                    | T <sub>A</sub>                 | −40 to 105 °C |

| Recommended operating temperature range | Case temperature                       | T <sub>C</sub>                 | -             |

|                                         | Junction temperature                   | TJ                             | -43 to 108 °C |

| Absolute maximum junction temperature   | -                                      | 125 °C                         |               |

| Maximum power dissipation               |                                        | -                              | 66 mW         |

|                                         | Junction to ambient thermal resistance | θ <sub>JA</sub> <sup>(1)</sup> | 35 °C/W       |

| Theta-JA, -JB and -JC                   | Junction to case thermal resistance    | $\theta_{JC}$                  | 5 °C/W        |

|                                         | Junction to board thermal resistance   | $\theta_{JB}$                  | 20 °C/W       |

<sup>1.</sup> According to JESD51-2 (still air condition).

DB4737 - Rev 3 page 10/22

# 5 Delivery packing

Surface-mount packages can be supplied with tape and reel packing. The reels have a 13" typical diameter. Reels are in plastic, either anti-static or conductive, with a black conductive cavity tape. The cover tape is transparent anti-static or conductive.

The devices are positioned in the cavities with the identifying pin (normally Pin "1") on the same side as the sprocket holes in the tape.

The STMicroelectronics tape and reel specifications are compliant with the EIA 481-A standard specification.

Table 7. Packages on tape and reel

| Package  | Description                                          | Tape width | Tape pitch | Reel diameter | Quantity per reel |

|----------|------------------------------------------------------|------------|------------|---------------|-------------------|

| UFQFPN32 | Ultra thin fine pitch quad flat pack no-lead package | 12 mm      | 8 mm       | 13 in.        | 3000              |

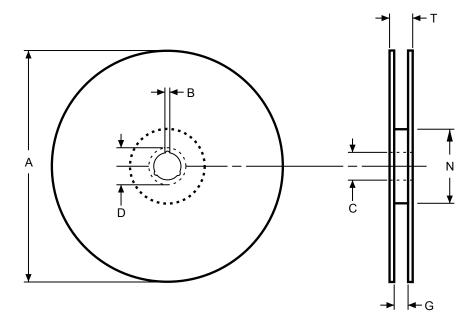

Figure 6. Reel diagram

Table 8. Reel dimensions

| Reel size | Tape width | A Max. | B Min. | С       | D Min. | G Max. | N Min. | T Max. | Unit |

|-----------|------------|--------|--------|---------|--------|--------|--------|--------|------|

| 13"       | 12         | 330    | 1.5    | 13 ±0.2 | 20.2   | 12.6   | 100    | 18.4   | mm   |

DB4737 - Rev 3 page 11/22

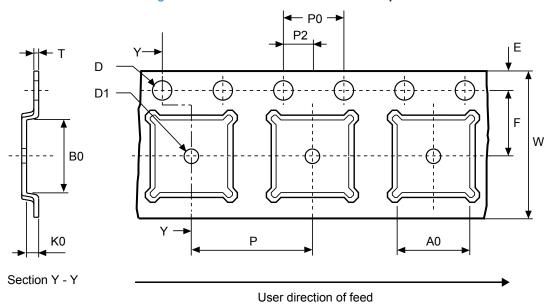

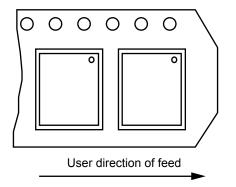

Figure 7. UFQFPN32 - Embossed carrier tape

1. Drawing is not to scale.

Figure 8. UFQFPN32 - Chip orientation in the embossed carrier tape

Table 9. UFQFPN32 - Carrier tape dimensions

| Package    | A0       | В0       | K0        | D1 Min. | Р      | P2      | D          | P0     | E         | F        | W       | T Max.    | Unit |

|------------|----------|----------|-----------|---------|--------|---------|------------|--------|-----------|----------|---------|-----------|------|

| UFQFPN 5×5 | 5.3 ±0.1 | 5.3 ±0.1 | 0.75 ±0.1 | 1.5     | 8 ±0.1 | 2 ±0.05 | 1.55 ±0.05 | 4 ±0.1 | 1.75 ±0.1 | 5.5 ±0.1 | 12 ±0.3 | 0.3 ±0.05 | mm   |

DB4737 - Rev 3 page 12/22

# 6 UFQFPN32 package marking information

Parts marked as E or ES (for engineering sample) are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

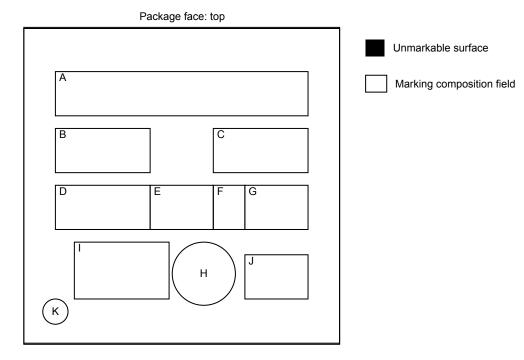

Figure 9. UFQFPN32 - Standard marking example

#### Legend:

- A: Marking area Up to 8 digits

- B: Marking area 3 digits

- C: BE sequence (LLL)

- D: Country of origin (3 characters allowed (max.))

- E: Assembly plant (PP)

- F: Assembly year (Y)

- 1. The dot on the back side indicates the pin 1 location.

- G: Assembly week (WW)

- H: Second level interconnect

- I: Standard STMicroelectronics logo

- J: Diffusion traceability plant (WX)

- K: Dot<sup>(1)</sup>

DB4737 - Rev 3 page 13/22

# 7 Ordering information

Table 10. Ordering information

| Ordering code    | Generic product | Factory firmware<br>version | Package  | Minimum<br>ordering<br>quantity | Marking<br>(area A) | Marking<br>(area B) |

|------------------|-----------------|-----------------------------|----------|---------------------------------|---------------------|---------------------|

| ST33KTPM2X32DKG8 |                 | 9.257<br>(0x00.09.01.01)    | UFQFPN32 | 3000                            | KTPM                | KG8                 |

| ST33KTPM2X32CKE2 | ST33KTPM2XSPI   | 9.256<br>(0x00.09.01.00)    | UFQFFN32 | 3000                            | KIFW                | KE2                 |

DB4737 - Rev 3 page 14/22

# 8 Support and information

Additional information regarding ST TPM devices can be obtained from the www.st.com website.

For any specific support information you can contact STMicroelectronics through the following e-mail: TPMsupport@list.st.com.

STMicroelectronics has put in place a Product Security Incident Response Team (ST PSIRT). We encourage you to report any potential security vulnerability that you might suspect in our products through the ST PSIRT web page: https://www.st.com/psirt.

DB4737 - Rev 3 page 15/22

# **Appendix A Referenced documents**

The following materials are to be used in conjunction with or are referenced by this document.

[TPM 2.0 P1 r159] TPM Library, Part 1, Architecture, Family 2.0, rev 1.59, TCG

[TPM 2.0 P2 r159] TPM Library, Part 2, Structures, Family 2.0, rev 1.59, TCG

[TPM 2.0 P3 r159] TPM Library, Part 3, Commands, Family 2.0, rev 1.59, TCG

[TPM 2.0 P4 r159] TPM Library, Part 4, Supporting routines, Family 2.0, rev 1.59, TCG

[TPM 2.0 rev159 Err 1.4] Errata Version 1.4 for Trusted Platform Module Library Family 2.0 Revision 1.59, TCG

[PTP 2.0 r1.05] TCG PC Client Platform TPM Profile (PTP) for TPM 2.0 Version 1.05 Revision 14, TCG

[PTP 2.0 errata] Errata version 1.0 for PC Client Platform TPM Profile (PTP) for TPM 2.0 Version 1.05 Revision

0.14, TCG

[PKCS#1] PKCS#1: v2.1 RSA Cryptography Standard, RSA Laboratories

[AN2639] Application note, Soldering recommendations and package information for Lead-free

ECOPACK microcontrollers, STMicroelectronics

[TCG EK Cre Profile TPM 2.3] TCG EK credential profile for TPM Family 2.0 Level 0. Specification Version 2.3 Revision 2, 23

July 2020, TCG.

[TPM 2.0 PP] TCG Protection Profile for PC Client Specific TPM 2.0 Library Revision 1.59; Version 1.3

[SP800-90B] Recommendation for the entropy sources used for random bit generation, January 2018, NIST

Recommendation for random number generation using deterministic random bit generators,

June 2015, NIST

[SP800-90Ar1]

DB4737 - Rev 3 page 16/22

# **Revision history**

**Table 11. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-May-2022 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 27-Jan-2023 | 2        | <ul> <li>Updated:         <ul> <li>and in cover page</li> </ul> </li> <li>Section 1 Description</li> <li>UFQFPN32 pin and signal description including Figure 1 and Table 1</li> <li>Section 3.1 Recommended power supply filtering including Figure 2. Recommended filtering capacitors on V<sub>CC</sub> and Table 2. V<sub>CC</sub> rising slope</li> <li>Section 3.2 SPI_CS optional filtering</li> <li>Section 3.3 Device integration for SPI communication inlcuding Figure 3. Typical hardware implementation for SPI communication (UFQFPN32 package)</li> <li>including</li> <li>UFQFPN32 package information: corrected typo on introduction and on line D2 of Table 1</li> </ul> |

| 30-Jan-2024 | 3        | Changed the scope of the document to limit it to ST33KTPM2XSPI (For information on ST33KTPM2XI2C, refer to DB5191).  Updated the following sections:  Section Features  Section 1 Description  Section 2 UFQFPN32 pin and signal description  Section 4.1 UFQFPN32 package information  Section 7 Ordering information  Section 3.1 Recommended power supply filtering  Added the following sections:  Section 4.2 Thermal characteristics of packages  Section Appendix A Referenced documents                                                                                                                                                                                             |

DB4737 - Rev 3 page 17/22

#### **Glossary**

**AES** Advanced encryption standard

**CA** Certification Authority

**CC** Common Criteria

**DRBG** Deterministic random bit generator

**EC** Elliptic curve

**ECC** Elliptic curve cryptography

**ECDAA** Elliptic curve direct anonymous attestation (algorithm)

**ECDH** Elliptic curve Diffie-Hellman

ECDSA Elliptic curve digital signature algorithm

**EK** Endorsement key

**ESD** Electrostatic discharge

FIPS Federal Information Processing Standards

**GPIO** General purpose input/output

**HBM** Human body model

**HMAC** Hash-based message authentication code or keyed-hash message authentication code

I<sup>2</sup>C Inter-integrated circuit

NIST National Institute of Standards and Technology

**NV** Nonvolatile

PKCS Public key cryptographic standards

**PSS** Probabilistic signature scheme

**RNG** Random number generator

**RSA** Public-key cryptosystem (created by Ron Rivest, Adi Shamir and Leonard Adleman)

**RSAES** Rivest Shamir Adelman encryption/decryption scheme

**RSASSA** Rivest Shamir Adelman signature scheme with appendix

SHA Secure Hash algorithm

SPI Serial peripheral interface

TCG Trusted Computing Group®

**TPM** Trusted platform module

**TRNG** True random number generator

TSS TPM software stack

DB4737 - Rev 3 page 18/22

### **Contents**

| 1    | Des                                   | cription                                 | 3    |  |  |  |  |  |

|------|---------------------------------------|------------------------------------------|------|--|--|--|--|--|

| 2    | 2 UFQFPN32 pin and signal description |                                          |      |  |  |  |  |  |

| 3    | Elec                                  | ctrical integration guidance             | 5    |  |  |  |  |  |

|      | 3.1                                   | Recommended power supply filtering       | 5    |  |  |  |  |  |

|      | 3.2                                   | SPI_CS optional filtering                | 5    |  |  |  |  |  |

|      | 3.3                                   | Device integration for SPI communication | 6    |  |  |  |  |  |

| 4    | Pacl                                  | kage information                         | 7    |  |  |  |  |  |

|      | 4.1                                   | UFQFPN32 package information             | 7    |  |  |  |  |  |

|      | 4.2                                   | Thermal characteristics of packages      | . 10 |  |  |  |  |  |

| 5    | Deli                                  | very packing                             | .11  |  |  |  |  |  |

| 6    | Pacl                                  | kage marking information                 | .13  |  |  |  |  |  |

| 7    | Orde                                  | ering information                        | .14  |  |  |  |  |  |

| 8    | Sup                                   | port and information                     | .15  |  |  |  |  |  |

| App  | pendix                                | x A Referenced documents                 | .16  |  |  |  |  |  |

| Rev  | ision                                 | history                                  | .17  |  |  |  |  |  |

| Cor  | ntents                                | ;                                        | .19  |  |  |  |  |  |

| List | t of tal                              | bles                                     | .20  |  |  |  |  |  |

| List | t of fic                              | qures                                    | .21  |  |  |  |  |  |

# **List of tables**

| Table 1.  | Pin descriptions                                 | 4  |

|-----------|--------------------------------------------------|----|

| Table 2.  | V <sub>CC</sub> rising slope                     | 5  |

| Table 3.  | UFQFPN32 - Mechanical data                       | 8  |

| Table 4.  | Tolerance of form and position                   | 8  |

| Table 5.  | Tolerance of form and position symbol definition | 9  |

| Table 6.  | Thermal characteristics                          | 10 |

| Table 7.  | Packages on tape and reel                        | 11 |

| Table 8.  | Reel dimensions                                  | 11 |

| Table 9.  | UFQFPN32 - Carrier tape dimensions               | 12 |

| Table 10. | Ordering information                             | 14 |

| Table 11. | Document revision history                        | 17 |

DB4737 - Rev 3 page 20/22

# **List of figures**

| Figure 1. | UFQFPN32 pinout                                                          | . 4 |

|-----------|--------------------------------------------------------------------------|-----|

| Figure 2. | Recommended filtering capacitors on V <sub>CC</sub>                      | . 5 |

| Figure 3. | Typical hardware implementation for SPI communication (UFQFPN32 package) | . 6 |

| Figure 4. | UFQFPN32 - Outline                                                       | . 7 |

| Figure 5. | UFQFPN32 - Footprint example                                             | . 9 |

| Figure 6. | Reel diagram                                                             | 11  |

| Figure 7. | UFQFPN32 - Embossed carrier tape                                         | 12  |

| Figure 8. | UFQFPN32 - Chip orientation in the embossed carrier tape                 | 12  |

| Figure 9. | UFQFPN32 - Standard marking example                                      | 13  |

DB4737 - Rev 3 page 21/22

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics - All rights reserved

DB4737 - Rev 3 page 22/22